우리가 소위 말하는 RAM은 DRAM을 지칭한다.

하지만 DRAM 말고도 여러 종류의 RAM이 존재한다.

RAM은 Random Access Memory임을 직관적으로 알자.

플래쉬메모리와 혼동되는 부분이 일부 있으니

이 부분은 계속 비교를 의식할 수 있도록 하자.

성능은 주로 다음 3가지 지표를 기준한다.

DRAM은

동기식/비동기식

동기식 중에서도 SD, RD, DDR 등으로 나뉜다.

그 중 DDR이 주요 기술로 발전했다.

DDR = DDR SDRAM

DDR은 메모리칩셋과 메모리컨트롤러로 구성된다.

SDR에서 DDR로 발전했으며

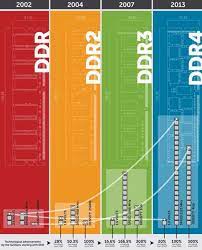

각 DDR1,2,3,4,5 가 어떤 점에서 기술발전 흐름을 갖는지를 관찰해보자.

https://information-factory.tistory.com/61

DDR이란? DDR1, DDR2 ,DDR3, DDR4, DDR5 (차이,뜻,정의)

DDR이란? DDR1, DDR2 ,DDR3, DDR4, DDR5 RAM을 구매할 때 DDR3, DDR4 라는 얘기를 많이 듣습니다. DDR을 무엇을 의미하는건지 알아보겠습니다. DDR 개념 이해를 위한 clock 파형 학습 DDR 개념을 알아보기 전에 c..

information-factory.tistory.com

외형적으로 노치 위치가 다르다.

성능의 경우 bus clk speed가 증가하고, 구동 voltage가 감소한다.

clk speed는 빠른 데이터 처리에 영향을 끼치며

voltage는 구동전압의 감소로 인한 소모전력의 감소에 영향을 끼친다.

DDR3 이후의 사례를 조금더 직접적으로 관찰해보자.

DDR3 vs DDR4 difference

https://www.atpinc.com/blog/ddr4-vs-ddr3-differences-advantages

DDR4 differences and advantages over previous generation modules

Physically, a DDR4 module, looks very similar to a DDR3. However, DDR4 has 288 pins compared with DDR3’s 240 pins; DDR4 SO-DIMMS have 260 pins instead of 204 in DDR3

www.atpinc.com

SDRAM

동기식 동적 램(SDRAM)은 다른 컴퓨터 구성 요소의 속도가 높아지면서 개발되었습니다. 다른 컴퓨터 구성 요소의 속도가 증가하면서 메모리 속도도 증가해야 했습니다. 이중 데이터 전송률(DDR)이 개발되었으며 이전 기술은 단일 데이터 전송률(SDR)로 부릅니다. DDR은 SDR보다 더 빠르면서도 전력은 더 적게 사용합니다. DDR 메모리는 클럭 신호의 상승 및 하강 에지 모두에서 데이터를 프로세서로 전송합니다.

SDRAM은 다른 컴퓨터 구성 요소들의 속도가 높아짐에 따라 1988년 개발되었습니다. 이전에는 메모리가 비동기식 즉, 프로세서와 독립적으로 작동해야 했습니다. 동기식 메모리는 메모리 모듈의 반응성을 시스템 버스 및 CPU 타이밍과 동기화합니다.

CPU와 동기화하여 메모리 모듈은 정확한 클럭 주기를 인식하여 CPU는 메모리 액세스 사이에 기다릴 필요가 없습니다. SDRAM은 클럭 주기당 한 번만 읽고 쓸 수 있습니다.

DDR

DDR은 SDRAM에 이은 차세대 제품으로 2000년에 도입되었습니다. DDR은 이전의 단일 데이터 전송률 메모리보다 더 큰 대역폭과 속도를 제공합니다. DDR은 클럭 신호의 상승 및 하강 에지 모두에서 데이터를 프로세서로 전송하므로 사이클당 2배를 제공합니다. 클럭 신호는 다운비트와 업비트로 구성됩니다. 두 비트를 모두 사용하여 데이터를 전송하면 데이터를 전송하기 위해 클럭 신호의 한 에지만 사용하는 단일 데이터 전송률 메모리보다 데이터 속도 메모리가 2배로 훨씬 더 빨라집니다.

DDR은 클럭 주기당 2비트의 데이터를 메모리 어레이에서 내부 입/출력 버퍼로 전송합니다. 이것을 2비트 프리페치라고 합니다. DDR 전송 속도는 일반적으로 266MT/s~400MT/s입니다.

이중 데이터 속도는 이중 채널 메모리와 다릅니다. 이중 채널 메모리에 대해서는 여기에서 알아보시기 바랍니다.

DDR2

DDR2는 2003년에 도입되어, 개선된 버스 신호를 이용해 DDR보다 2배 빠르게 외부 데이터를 운영합니다. DDR2는 DDR과 동일한 내부 클럭 속도로 작동하지만 향상된 입력/출력 버스 신호를 이용하여 전송 속도가 더 빠릅니다. DDR2은 DDR의 2배인 4비트 프리페치입니다. DDR2는 533MT/s~800MT/s를 제공합니다.

DDR3

2007년 DDR3의 전력 소비는 DDR2 대비 약 40% 감소하였으며, 프리페치 데이터를 8비트로 2배 증가시켰습니다. 전력 소비가 줄면 작동 전류와 전압을 낮출 수 있습니다. DDR이 작동하는 전압은 약 2.5V이고 DDR2는 평균 약 1.8V이며 DDR3의 경우 전압을 1.5V로 낮추었습니다. DDR3의 전송 속도는 800MT/s~1,600MT/s입니다.

DDR4

DDR4는 2014년에 도입된 이중 데이터 속도 랜덤 액세스 메모리의 최신 세대입니다. 1.2V로 가장 낮은 작동 전압으로, 이전 세대보다 높은 전송 속도를 제공합니다. DDR4는 16의 프리페치가 바람직하지 않기 때문에 뱅크 그룹을 도입하였습니다. 뱅크 그룹을 사용하면 각 그룹은 서로 독립적으로 8비트 데이터를 실행할 수 있습니다. 이를 통해 DDR4는 클럭 주기 내에서 여러 데이터 요청을 처리할 수 있습니다.

DDR4 전송 속도는 지속적으로 증가하고 있으며 DDR4 모듈은 5,100MT/s의 속도를 낼 수 있으며, 오버클럭 시 훨씬 더 빠른 속도를 제공합니다. Crucial Ballistix MAX 모듈은 2020년에 수많은 오버클러킹 세계 기록을 갱신했습니다.

DDR5

DDR5 메모리는 2021년에 도입되어 혁신적인 도약을 이룬 아키텍처로 채널 효율성 및 전력 관리 개선, 성능 최적화를 통해 차세대 멀티 코어 컴퓨팅 시스템을 구현합니다. DDR5의 출시 시 속도는 DDR4 대역폭의 거의 두 배입니다. 또한 테스트 환경에서뿐만 아니라 실제 조건에서도 더 빠른 속도를 제공하면서 채널 효율성을 저하하지 않고 메모리 성능을 확장할 수 있습니다. Crucial DDR5 메모리는 출시 시 최대 표준 DDR4 속도의 1.5배인 4,800MT/s로 작동합니다.

https://www.crucial.kr/articles/about-memory/difference-among-ddr2-ddr3-and-ddr4-memory

DDR2, DDR3 및 DDR4 메모리의 차이점 | Crucial.com

DDR4는 차세대 RAM입니다. 두 배의 데이터 속도를 내는 차세대 메모리의 차이점에 대해 알아보십시오.

www.crucial.kr

무언가의 이유로 직접 드러나지 않는다.

다음과 같은 요소에 초점을 맞춰야한다.

- 대역폭

- 전압

- 프리페치 (아키텍처)

여기서 프리페치에 대한 내용은 거의 처음 등장하는데 자세히 살펴보자.

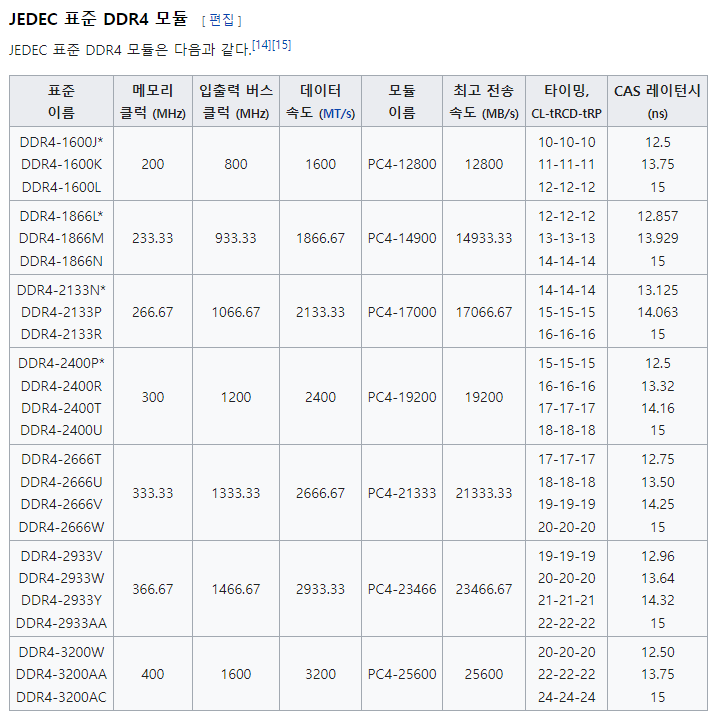

위의 표를 다시보면,

프리페치 비트가 몇인지가 아키텍처적 구별요소중 하나이다.

우선 여기까지 본 후에

DDR6 DDR6x 이 둘의 차이도 한번 살펴보자.

DDR4, GDDR5 및 GDDR6 / GDDR6X의 차이점

https://quasarzone.com/bbs/qn_hardware/views/772992

DDR4, GDDR5 및 GDDR6 / GDDR6X의 차이점

하드웨어에 미치고 유저들을 사랑하는 남자, 생각하는 모든 것들을 현실로 만들 수 있는 열정을 가진 남자,퀘이…

quasarzone.com

앞에 붙은 G는 Graphic을 의미한다.

GDDR5는 DDR3의 표준을 기반으로 한다. 그래서 1.2V가 아닌 1.5V이다.

GDDR5X는 전압을 1.35V로 낮추며, 대역폭을 16Bbit/s로 증가시킨다.

(하지만 X 시리즈에 대한 부정적인 커뮤니티 여론이 있는 것을 확인할 수 있다.)

여기서부터는 표준화가 되지 않고 분화되는 것을 확인할 수 있는데

정리하자면

1. DDR 이랑 비했을 때 GDDR은, band width를 높히기 위해 data rate을 높힘

2. GDDR에서는 QDR기술까지 적용해 가며 data rate을 높혀왔음

3. 근데 data rate이 높으면, 에너지 효율이 떨어져서 나온게 HBM임

4. HBM은 data rate는 낮지만 (느리지만), data width가 넓어서 밴드위쓰는 높음 (느리게 한번에 많이 보냄)

5. HBM은 3D stacking의 장점도 있지만, 너무 비싼 문제가 있음

6. GDDR6X은 QAM4라는 (새로운건 아니고, 이미 통신쪽에서는 있던 기술) 것을 적용하여 유효 data rate을 2배로 올림, 그러나 노이즈에 취약한 기술이라 yield 문제가 좀 있다고 알려져있고, 게다가 JEDEC standard가 아님 (현재 마이크론만 생산)

여기서 QDR, HBM, QAM4 와 같은 별도의 기술들이 도입되는 것을 볼 수 있는데, 잠시 생략하자.

그리고 무언가가 보이게 될때 JEDEC 표준을 만족하고 있는지를 확인하는 것은 도움이 된다.

그리고 아직 주류로 사용되고 있는 것은 DDR3,4 이며

아직 DDR5 또한 주류가 아니다.

하지만 이번 삼성이 DDR6를 발표한 것은 기술개발 측면이 강하다.

(실제 제품이 나오기까지 5년 정도가 걸릴 것으로 예상된다.)

https://quasarzone.com/bbs/qn_hardware/views/1278674

DDR6 메모리 첫 노출: 용량, 성능 향상

현재 DDR5 메모리는 주류가 아닙니다. 그러나 DRAM 메모리 칩의 주요 제조업체는 이미 DDR6 개발을 …

quasarzone.com

그럼 현재로서 가장 초점에 맞춰야 하는 것은

DDR4와 DDR5의 차이점과

아직 대중화되지 못하고 있는 이유임을 파악했다.

DDR5 대중화에 대한 커뮤니티 의견

(고가라인에서는 지금도 쓰인다, 다만 소비자시장인 데스크탑에!)

https://quasarzone.com/bbs/qf_cmr/views/1544727

2022년 상반기에는 DDR5 대중화 될까요?

2021년 7월104002070SUPERDDR4 16G본체 팔고2022년에 DDR5 기다리는데요내년 상반기에…

quasarzone.com

https://coolenjoy.net/bbs/27/3015152?sca=%ED%86%A0%EB%A1%A0

쿨엔조이,쿨앤조이 coolenjoy, cooln, 쿨엔, 검은동네

pc,컴퓨터, 하드웨어,CPU오버클럭,VGA쿨러,오버클럭,PC튜닝,케이스튜닝,cpu,vga

coolenjoy.net

http://www.hwbattle.com/bbs/board.php?bo_table=cpumbram&wr_id=156142

DDR5는 2023년이나 되야 데탑용으로 일반화될 겁니다만... > CPU, 메인보드, 램 게시판 - 하드웨어 배

DDR5는 2023년이나 되야 데탑용으로 일반화될 겁니다만... > CPU, 메인보드, 램 게시판 - 하드웨어 배틀(Hardware Battle)

www.hwbattle.com

가장 맞물려 돌아가는 것은

Zen3에서 Zen4로의 Transition인데

AMD ZEN4 CPU 마이크로아키텍처

AMD ZEN 4 마이크로아키텍처 - 나무위키

ZEN 4 마이크로아키텍처 기반의 고성능 노트북용 제품군으로 알려져 있으며, Raphael과 같은 칩렛 구조라는 소문이 있다. ZEN 4 마이크로아키텍처 기반의 APU용 제품군으로 알려져 있으며, 2022년 6월 9

namu.wiki

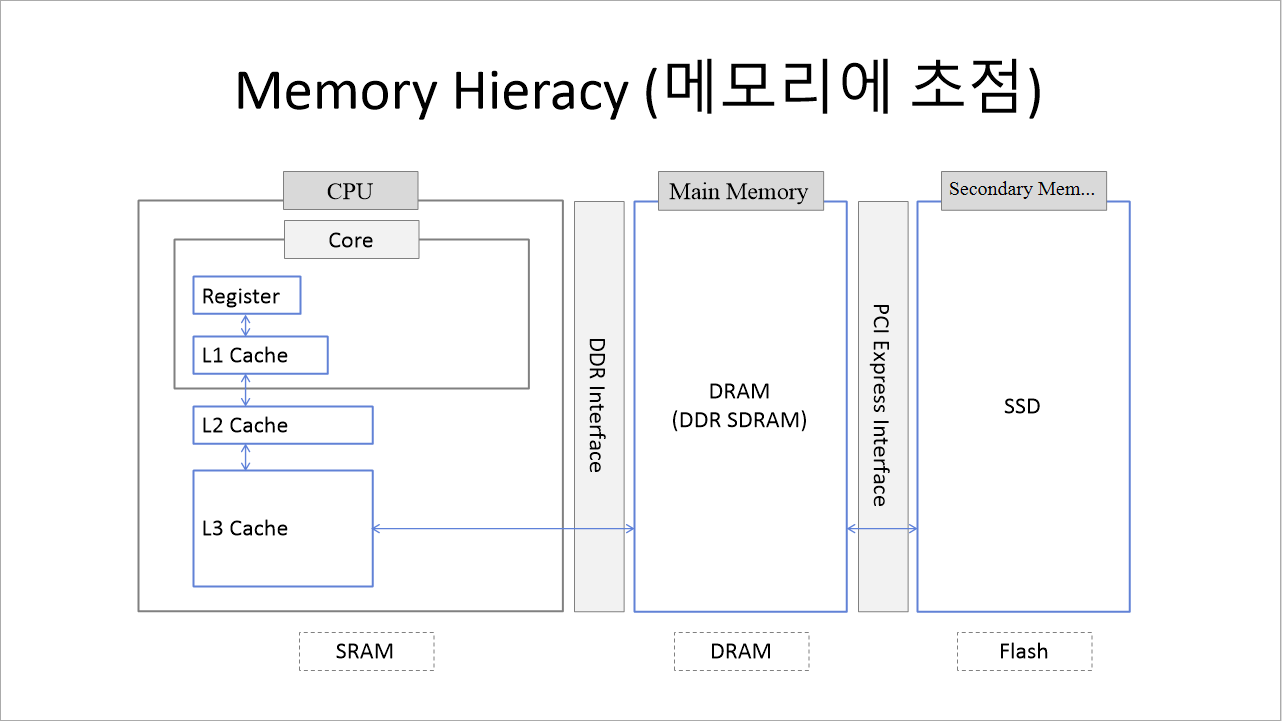

이는 Memory Hierachy 에서

DRAM이 Cache(SRAM)을 보완하는 빠른 메모리이기 때문이며

이 구조를 다시한번 상기하면, DRAM과 SSD의 역할이 잘 보인다.

https://lifeisenjoyable.tistory.com/3

컴퓨터 내 DRAM의 역할과 흐름

DRAM은 무엇일까요? DRAM은 컴퓨터 프로세서가 필요로 하는 데이터를 저장한 후 공급하는 역할을 하고 있습니다. 현대 컴퓨터 프로세서는 모두 Von-Neumann 구조를 따르죠. Von-Neumann 구조에서 프로세

lifeisenjoyable.tistory.com

그림을 그려보자.

우선 현재로서 내 머리속의 구조는 다음과 같다.

Interface에 대한 지식이 부족하므로

우선 CPU - DDR Interface - DRAM 부분을 살펴보자.

예를들어 ZEN과 같은 CPU가 DRAM Interface 호환성을 어떻게 지원하는지 등.

(이런 시리즈글도 있네. 주로 스트로브 및 아날로그 시그널 레이어 등을 다루지만 이해도 증강에 도움될듯)

https://m.blog.naver.com/lecroykorea/221030514225

DDR 메모리 인터페이스의 기본

DDR 메모리 인터페이스의 기본 그림 1: DDR 물리계층 테스트의 대표적인 테스트 설정 더블 데이터 레...

blog.naver.com

https://m.blog.naver.com/lecroykorea/221040787353

DDR 메모리 인터페이스의 물리 계층 테스트(Part 1)

DDR 메모리 인터페이스의 물리 계층 테스트(Part 1) 그림 1: DDR 테스트에서 꼭 필요한 클럭, 스트...

blog.naver.com

https://m.blog.naver.com/lecroykorea/221045372376

DDR 메모리 인터페이스의 물리 계층 테스트(Part 2)

DDR 메모리 인터페이스의 물리 계층 테스트(Part 2) 그림 1: DDR 메모리의 전형적인 BGA 패키지 ...

blog.naver.com

https://m.blog.naver.com/lecroykorea/221050329087

DDR 메모리 인터페이스의 물리계층 테스트 (Part 3)

DDR 메모리 인터페이스의 물리계층 테스트 (Part 3) 지난 포스팅까지는 DDR 인터페이스의 물리계층 ...

blog.naver.com

https://m.blog.naver.com/lecroykorea/221054723064

DDR 메모리 인터페이스의 물리계층 테스트 (Part 4)

DDR 메모리 인터페이스의 물리계층 테스트 (Part 4) DDR 인터페이스의 물리적 계층을 테스트하는 다...

blog.naver.com

DRAM Controller

메모리와 메모리컨트롤러 사이의 데이터전송은 버스트 형태로 발생한다.

이를 위해 스트로브(DSQ)신호는 읽기 및 쓰기 동작중에만 동작하는 차동 버스트 클럭이다.

(한 석사논문 DDR 알고리즘 및 구현, 세종대, 차재아 및 이성주님)

DDR SDRAM은 이름과 같이 double data rate로 기존의 SDRAM의 전송속도가 2배 빠른 RAM이다. DDR은 기존의 SDRAM과 비교했을 때, 더 높은 속도의 클락으로 동작한다. 이러한 장점으로 인해 다양한 복잡한 전자기기들을 개발하는 SoC 또는 embedded 시스템 엔지니어들은 대부분 그들의 설계에서 방대하고 필수적인 정보를 빠르게 읽고 쓰기 위해 DDR SDRAM을 사용한다. 설계자들은 DDR을 인터페이스하는 모듈을 직접 설계하기 위해서는 DDR의 스펙와 동작에 대해 알아야 한다. 하지만 이 모든 것을 연구하기에는 설계자에게 있어 엄청난 시간적 부담감을 야기한다. 따라서 본 논문에서는 DDR을 안정적으로 interface하는 모듈을 설계하는 방법을 제시한다. 덧붙여 interface 모듈이 칩의 면적을 차지하는 비율을 줄이기 위한 효율적인 설계 방식도 제안한다. 제안한 인터페이스 시스템은 Micron사의 MT46H16M16LF DDR 모델을 타겟으로 하여 verilog HDL을 사용하여 구현하 였고, HDL 시뮬레이션으로 검증하였다. 그 다음 post 시뮬레이션을 통해 FPGA 환경으로 검증한 뒤 Spartan-6에 구현하였다. 따라서 모든 검증과 보드 테스트 결과는 DDR 인터페이스가 안정적인 정상 동작을 가지면서 작은 복잡도와 비용을 갖는다는 것을 확인할 수 있다.

https://scienceon.kisti.re.kr/srch/selectPORSrchArticle.do?cn=DIKO0014007355&dbt=DIKO

[논문]DDR Interface의 알고리즘 및 구현

DDR SDRAM은 이름과 같이 double data rate로 기존의 SDRAM의 전송속도가 2배 빠른 RAM이다. DDR은 기존의 SDRAM과 비교했을 때, 더 높은 속도의 클락으로 동작한다. 이러한 장점으로 인해 다양한 복잡한 전자

scienceon.kisti.re.kr

http://www.riss.kr/search/detail/DetailView.do?p_mat_type=be54d9b8bc7cdb09&control_no=b2f898212b0a3ed4ffe0bdc3ef48d419&outLink=K

www.riss.kr

http://sejong.dcollection.net/public_resource/pdf/000002226935_20220716115005.pdf

고속 DRAM Interface와 관련된 한 리서치논문

https://koreascience.kr/article/JAKO201216238707697.pdf

CPU와 RAM간의 통신관계를 모델링하기 위한 기초적인 모델링은 해당글을 참고하면 된다.

https://itigic.com/ko/communication-between-cpu-and-ram-how-does-it-occur/

CPU와 RAM 간의 통신, 어떻게 발생합니까? | ITIGIC

데이터를 얻기 위해 할당한 RAM과 프로세서가 뒤따르는 프로세스가 무엇인지 궁금하다면 운이 좋을 것입니다. 이 기사에서 이 프로세스가 무엇인지 설명할 것이기 때문입니다. 무엇 사이의 의사

itigic.com

이 블로그에도 좋은 글이 많다.

https://itigic.com/ko/tag/ram/

ITIGIC

기술 방법, 팁 및 요령

itigic.com

이 글에서도 컨트롤러에 대한 인사이트를 제공한다.

https://itigic.com/ko/ssd-dram-less-features-storage-access-and-future/

SSD DRAM-리스, 기능, 스토리지 액세스 및 미래 | ITIGIC

DRAM이 없는 SSD 장치는 이름에서 알 수 있듯이 온보드 DRAM 메모리가 없기 때문에 기존 SSD보다 훨씬 저렴한 SSD 유형입니다. 그러나 RAM 부족은 그러한 SSD에 어떤 영향을 미치며 그 이유는 무엇입니

itigic.com

이 글도 인터페이스 관련 설명이 풍부한데

https://it-eldorado.tistory.com/48

[CSAPP] Memory Hierarchy

1. 메모리 계층 (Memory Hierarchy) DRAM은 비트 당 가격이 저렴하지만 접근 속도가 매우 느리고, SRAM은 비트 당 가격이 비싸지만 접근 속도가 매우 빠르다. 이때 뒤에서 설명할 지역성(Locality)을 잘 활용

it-eldorado.tistory.com

(CSAPP를 공부하는 사람들이 있구나)

Computer Systems: A Programmer's Perspective

CS:APP3e, Bryant and O'Hallaron

Overview. This book (CS:APP3e) is the third edition of a book that stems from the introductory computer systems course we developed at Carnegie Mellon University, starting in the Fall of 1998, called "Introduction to Computer Systems" (ICS). The presentati

csapp.cs.cmu.edu

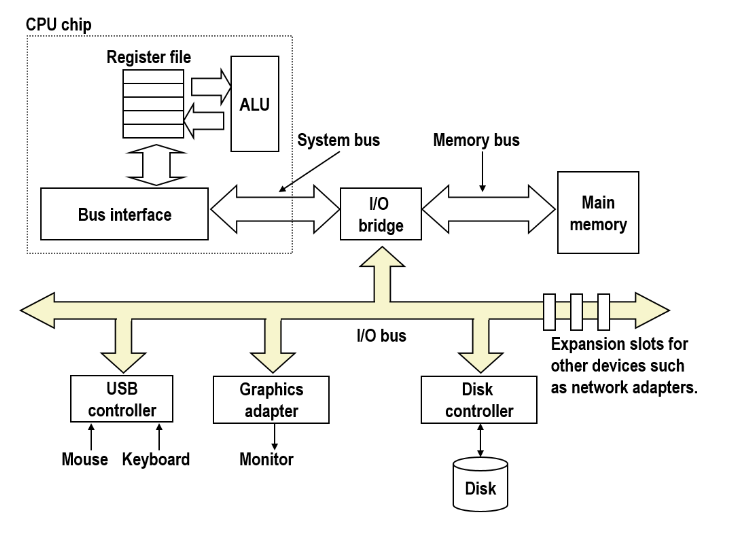

아 내가 지금 Computer Bus에 대한 이해 없이

Interface를 접근하려고 해서 혼동이 있는 것일 수 있겠다.

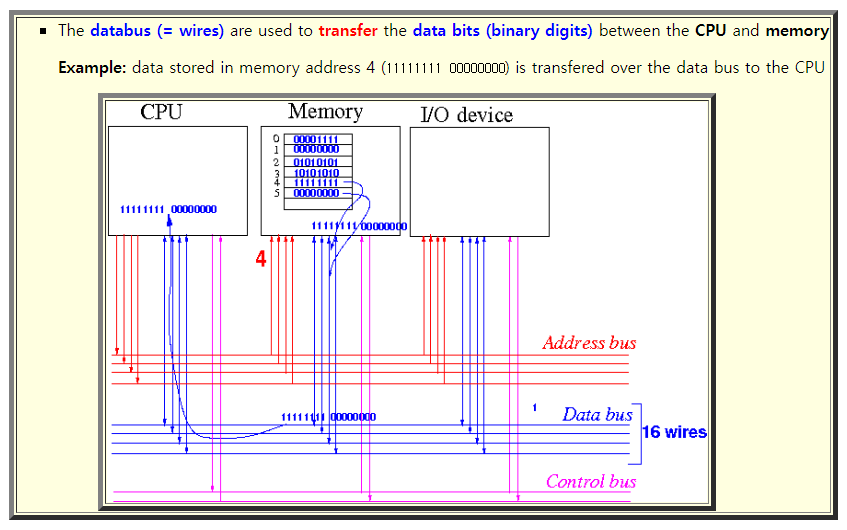

CPU 와 메모리가 소통할때는 직접 소통하는 것이 아닌 시스템 버스를 이용해서 소통을 한다.

이제부터 메모리에 대해서는 일반 블로그가 아닌 학문 강의자료 또는 논문을 참고하는게 빠를듯하다.

단 컴퓨터 그리고 임베디드 관련해서는 일반 블로그를 계속 참고한다.

https://users.ece.cmu.edu/~koopman/lectures/ece348/08_bus_memory_handouts.pdf

A High-Performance Memory Interface for Next-Generation Data Centers

A High-Performance Memory Interface for Next-Generation Data Centers - Global Semiconductor Alliance

Over the past 30 years processor development has been on a tremendous path. Transistor densities rose according to Moore’s Law, and the clock frequencies of processors and their cores are now in the 4 GHz range. Due

www.gsaglobal.org

그리고 여기서부터는 north-bridge 같은 어떠한 architecture를 차용했는지에 따른 구성이 달라질 수 있다.

https://www.mdpi.com/1424-8220/19/1/140/htm

A Processing-in-Memory Architecture Programming Paradigm for Wireless Internet-of-Things Applications

The widespread applications of the wireless Internet of Things (IoT) is one of the leading factors in the emerging of Big Data. Huge amounts of data need to be transferred and processed. The bandwidth and latency of data transfers have posed a new challeng

www.mdpi.com

http://www.embeddedlinux.org.cn/EmbSysFirmDemy/0015.html

The CPU/Memory Interface--Embedded Systems Firmware Demystified--퓌흙駕linux櫓匡籃

The most critical interface in any computing system is the connection between memory and the CPU. If this interface doesn’t function properly, the CPU cannot function because it cannot retrieve instructions. If the processor can’t reliably retrieve ins

www.embeddedlinux.org.cn

The last CPU : CPU가 없는 구조에 대한 제안임. 주의

[PDF] The last CPU | Semantic Scholar

The role and the structure of the OS in a system that has no CPU is explored and it is demonstrated that all necessary functionality can be moved to other hardware. Since the end of Dennard scaling and Moore's Law have been foreseen, specialized hardware h

www.semanticscholar.org

https://dl.acm.org/doi/10.1145/3458336.3465291

The last CPU | Proceedings of the Workshop on Hot Topics in Operating Systems

ABSTRACT Since the end of Dennard scaling and Moore's Law have been foreseen, specialized hardware has become the focus for continued scaling of application performance. Programmable accelerators such as smart memory, smart disks, and smart NICs are now be

dl.acm.org

ABSTRACT

Since the end of Dennard scaling and Moore's Law have been foreseen, specialized hardware has become the focus for continued scaling of application performance. Programmable accelerators such as smart memory, smart disks, and smart NICs are now being integrated into our systems. Many accelerators can be programmed to process their data autonomously and require little or no intervention during normal operation. In this way, entire applications are offloaded, leaving the CPU with the minimal responsibilities of initialization, coordination and error handling.

We claim that these responsibilities can also be handled in simple hardware other than the CPU and that it is wasteful to use a CPU for these purposes. We explore the role and the structure of the OS in a system that has no CPU and demonstrate that all necessary functionality can be moved to other hardware. We show that almost all of the pieces for such a system design are already available today. The responsibilities of the operating system must be split between self-managing devices and a system bus that handles privileged operations.

https://dl.acm.org/doi/pdf/10.1145/3458336.3465291

http://www.mathcs.emory.edu/~cheung/Courses/255/Syl-ARM/4-intro/bus-width.html

http://www.mathcs.emory.edu/~cheung/Courses/255/Syl-ARM/4-intro/bus-width.html

Each wire of the address bus can convey (= transfer) 1 bit of the address Therefore: An address bus that contains n wires can convey n bits Each memory byte is identified by a unique memory address !!! So: A address bus that consists of 8 wires (= bits), c

www.mathcs.emory.edu

우선 현재까지의 결론적인 모식은 다음과 같다.

이 부분을 파기 위해서 어디를 봐야할지 간만에 보니 감이 안 잡힌다.

아 여기서 중요 포인트를 하나 잡았는데

노스브릿지 구조 전후에 따라

어떤 DRAM이냐 어떤 CPU이냐에 따른 차이가 생겼으며

현재는 JEDEC 표준으로서의 DDR4에 초점을 맞추는 것이 좋으며

어떤 제조사의 DRAM을 선택하는지도 치명적이다.

https://quasarzone.com/bbs/qf_overclocking/views/19657

메모리 컨트롤러가 뭔지 간략하게 설명을 해볼까 합니다

이걸 대체 어디서부터 설명을 해야 할지 막막하기도 하고... 일단 전기 분야의 전문 용어를 사용하면(저는 전…

quasarzone.com

최종 규격[편집]

2012년 9월 25일, 메모리 표준 규격을 정하는 JEDEC (Joint Electron Device Engineering Council ) 은 차기 메모리인 DDR4 의 최종 규격을 발표했다. 이에 의하면 핀당 전송 속도는 최소 1.6 GT/s (Gigatransfer per second)에서 최대 3.2 GT/s 가 기본이지만 이전 DDR3 이하 메모리에서 그랬듯이 이보다 더 빠른 규격이 등장할 수도 있을 것으로 예상되었다. 또한 DDR4 메모리는 기본이 1.2 V 로 작동해 1.5 V 로 작동하는 DDR3 메모리보다 전력 소모가 줄어들고 속도는 빨라졌기 때문에 도입되면 큰 이점이 있을 것으로 기대되었다.[13]

DDR4 SDRAM - 위키백과, 우리 모두의 백과사전

ko.wikipedia.org

https://kor.go-travels.com/19748-ddr4-memory-833028-5055828

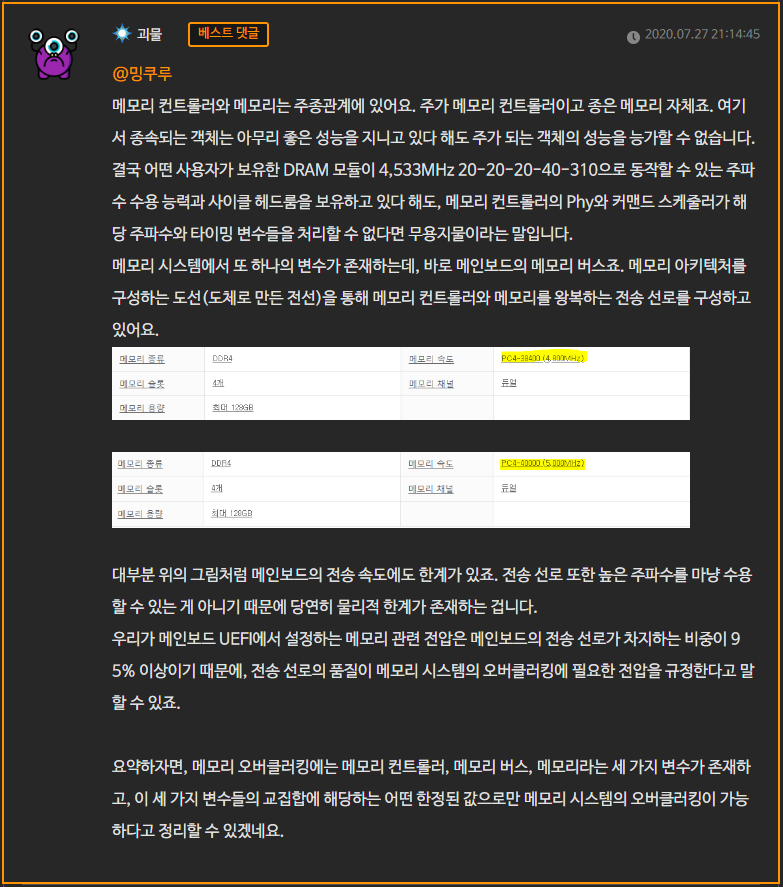

CPU에 내장되어있기 위해서는 표준이라는 것이 필요하다.

소켓 : 메모리 컨트롤러가 CPU 내부로 진입한 게 마냥 좋은 것만은 아닙니다. 프로세서가 특정한 종류의 메모리만 인식할 수 있게 제한받을뿐만 아니라 새로운 메모리 기술을 지원하려면 칩 자체를 재설계해야 하는 부담을 안겨 줄 수 있습니다. 지금 어마디의 AM4의 소켓이 그렇죠. 메모리 컨트롤러를 바꾸려면 아키텍처의 설계를 처음부터 다시 해야 하고 소켓 또한 변경해야 해서 Gear-down 등을 이용해 상황을 개선하려 많은 노력을 하고 있죠. 모듈 인식률 재고와 IF 동기화에 필요한 클럭 등의 확보를 위해 메모리 타이밍을 희생하고 그로 인해 획득한 클럭으로 CPU와 소통하게 됩니다. 물론... 이것으로도 역부족인 게 현실입니다.

이 사람 글은 모아볼 가치가 있는듯

https://quasarzone.com/bbs/qf_overclocking/views/58747

왜 그런 거짓을 말하는지는 생각해보면 간단하죠

제가 제조사를 직접 거론하면 뭐 달라지나요? 저는 x86 프로세서를 만드는 두 회사에서 모두 근무한 기록이 …

quasarzone.com

https://quasarzone.com/bbs/qf_overclocking/views/57527

Prime95 사용 방법을 모르면 수만 시간을 실행해도 효과 없어요

Priority 수치 조절하지 않고 Priority '1'에서 Prime95를 실행하는 건 세상 둘도 없는 …

quasarzone.com

https://quasarzone.com/bbs/qf_overclocking/views/57350

어디서부터가 메모리 오버클러킹인지는 표준을 보면 알죠

메모리라는 게 주파수와 타이밍으로 움직인다는 건 다들 아실 테니 그냥 패스할게요. 이건 뭐... 상식이니까요…

quasarzone.com

https://quasarzone.com/bbs/qf_overclocking/views/57174

오버클럭된 칩의 신뢰도 측정에 관한 법령이 존재해요

퀘이사존이라는 사이트가 무슨 논문 수준의 원고를 다루거나 접근 회원들이 관련 학술 자료를 찾으러 방문하는 건…

quasarzone.com

인텔에서 FPGA에서 제공하는 메모리 컨트롤러

고성능 메모리 컨트롤러 II SDRAM 인텔® FPGA IP 코어

고성능 메모리 컨트롤러 II는 DDR2 SDRAM 사용의 복잡한 측면을 처리합니다.

www.intel.co.kr

fpga 메모리 컨트롤러

xilinx의 MIg Core Design

http://libertron.com/portfolio-items/memory-interface/

리버트론

FPGA & Embedded System 토탈 솔류션 제공, 반도체 전문 기업

libertron.com

Textbook

How to Design a High-Speed Memory Interface

https://studylib.net/doc/8748142/xilinx-xapp688-creating-high-speed-memory-interfaces-with...

Xilinx XAPP688 Creating High-Speed Memory Interfaces with Virtex

Free essays, homework help, flashcards, research papers, book reports, term papers, history, science, politics

studylib.net

리버트론의 교육 커리큘럼

10개 주제정도 있는데 다 나름 재미있어 보인다.

https://libertron.com/%ea%b5%90%ec%9c%a1%ec%84%bc%ed%84%b0/%ea%b5%90%ec%9c%a1%ea%b3%bc%eb%aa%a9/

리버트론

FPGA & Embedded System 토탈 솔류션 제공, 반도체 전문 기업

libertron.com

https://www.xilinx.com/products/intellectual-property/mig.html

Memory Interface

Memory Interface is a free software tool used to generate memory controllers and interfaces for Xilinx FPGAs.

www.xilinx.com

Memory Interfaces - UltraScale DDR3/DDR4 Memory

www.xilinx.com

https://www.xilinx.com/products/intellectual-property/ddr4.html

DDR4 Controller

The Xilinx DDR4 core can generate a full controller or phy only for custom controller needs. The controller will run up to 2400Mbps in UltraScale and 2667Mbps in UltraScale+.

www.xilinx.com

우선 여기서부터는

개괄 공부는 끝났고

직접적인 구현을 하면서 디테일들을 잡아나가야 할듯한데

직접적인 구현 등을 위한 공부 리소스에 대해서는 어느정도 확보한듯하다.

다시 현재 듣던 FPGA 강의를 마스터 한 후에, 그 다음 공부 주제를 이쪽으로 선택하자.

'적극적 생각 > 전공버퍼' 카테고리의 다른 글

| 2학기 SoC 에서의 포인트 (0) | 2022.07.16 |

|---|---|

| SK하이닉스, 연산 가능한 차세대 메모리 'PIM' 첫 개발, GDDR6-AiM (0) | 2022.07.16 |

| Samsung is releasing 512 GB DDR5 RAM modules — how this can supercharge zk-rollups (0) | 2022.07.16 |

| 삼성 메모리 공부할 것 리스트업 {DRAM, SSD} (0) | 2022.07.16 |

| GDDR6 (0) | 2022.07.16 |