자 주소문제를 해결해보도록 하자.

나는 지금 많은 데이터를 저장할 필요가 없다.

딱 4번만 저장하더라도, 그 4번을 어떤 주소에 저장해내는지를 파악해내는가가 관건이다.

그것을 추적할 수 있는 환경을 만든 후

오버플로우를 유도하고

거기서 생기는 문제를 풀어주면

첫 주소와 끝 주소를 확인할 수 있을듯 해 보인다.

---

MEM_DEPTH = 4로 조정해서

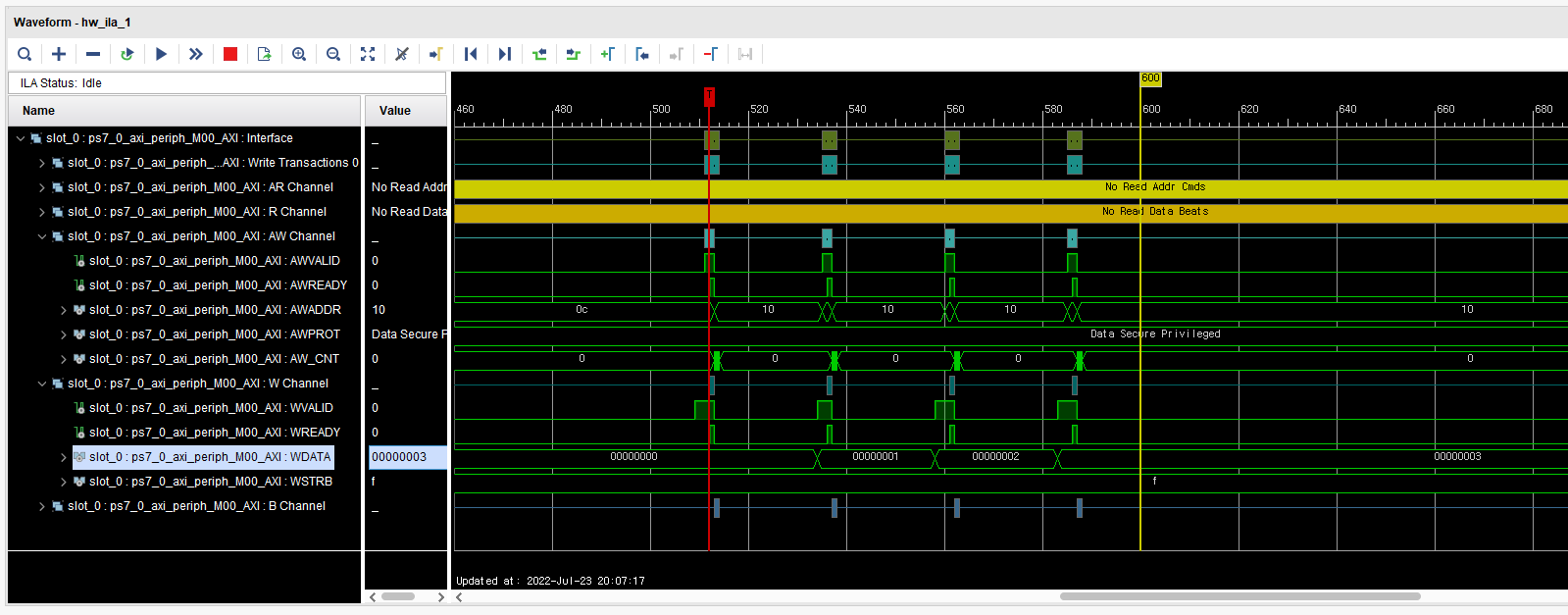

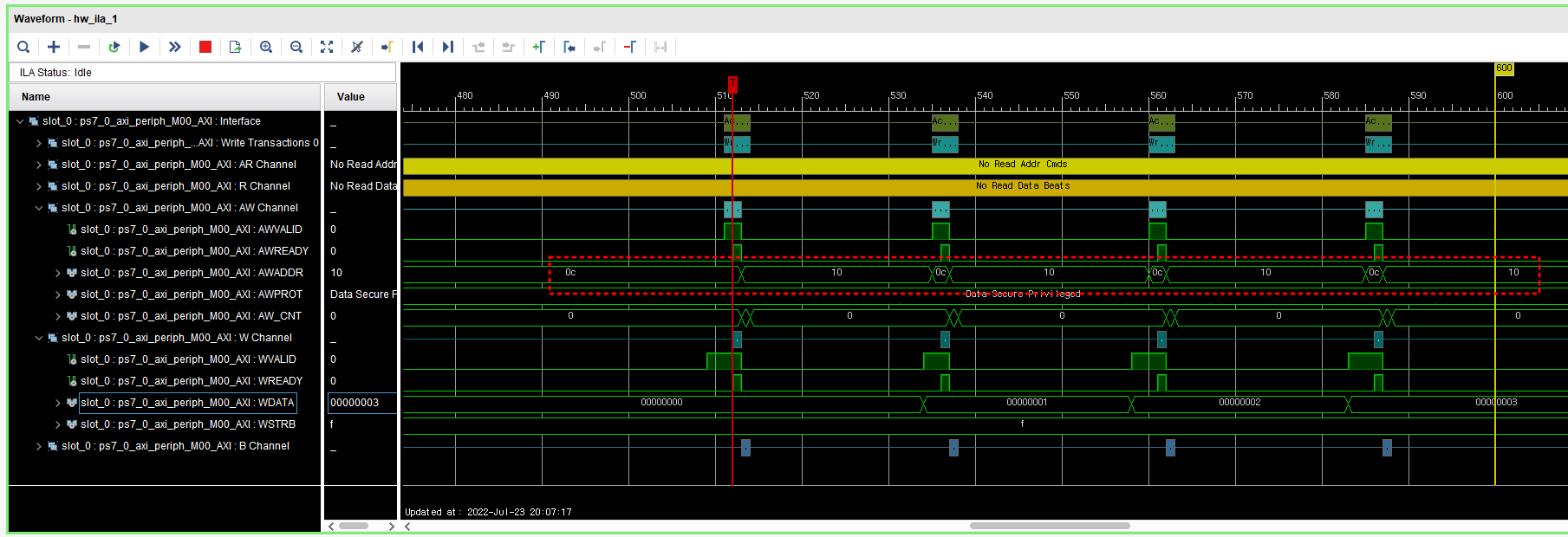

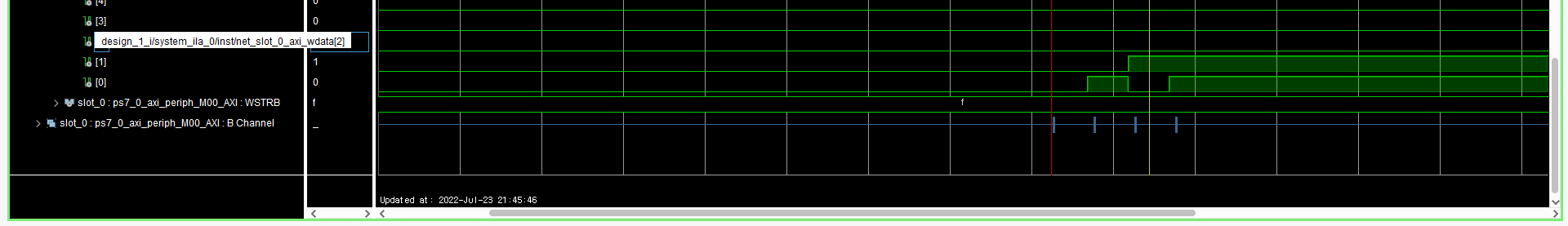

WRITE를 4번했다.

0,1,2,3을 잘 저장한 것을 볼 수 있다.

그때 우리는 주소를 '10번지'와 '0c번지'에 번갈아 보내주고 있다.

왜 이렇게 하느냐? 하면

BRAM에 보내기 위하여 Data Register를 사용하기 때문이다.

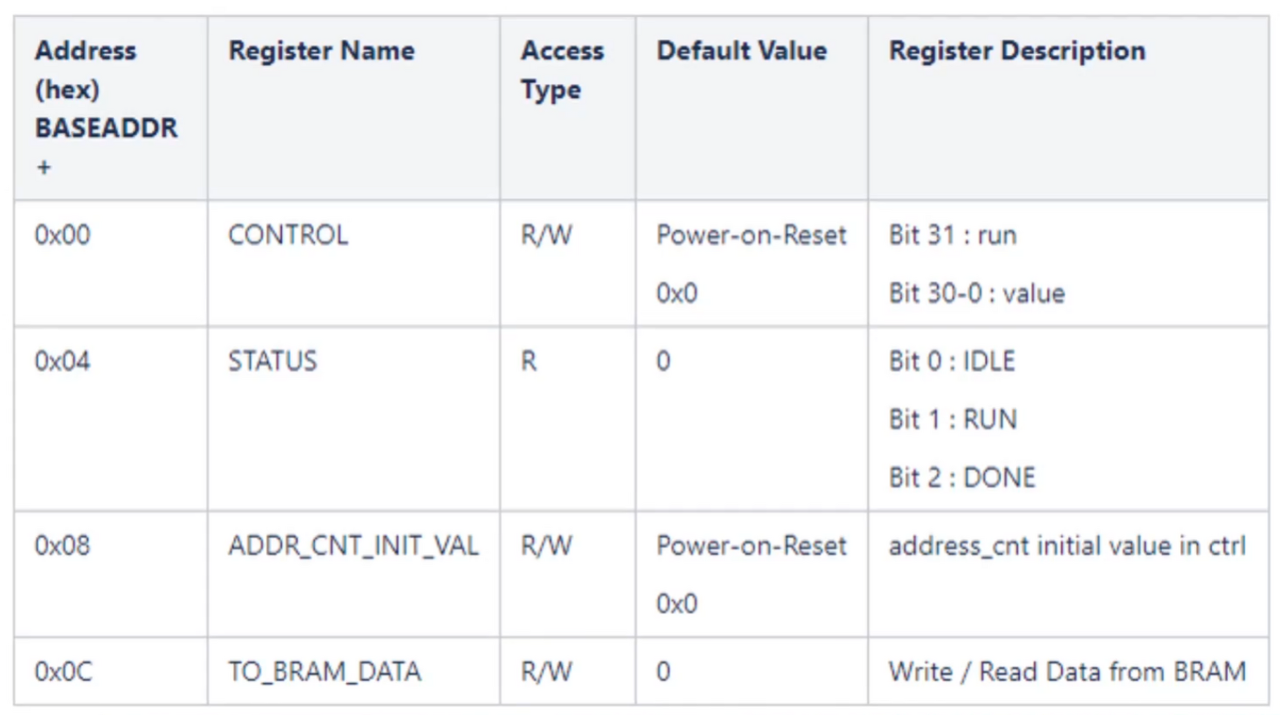

RegisterMap을 보자.

BASEADDR + 0x08 : Address 초기화

BASEADDR + 0x0c : Data Register

---

BASEADDR 그리고 Data Register에 대해서 더 파악하자.

얘(=Memory I/F Ctrl Reg)를 찾아야 한다.

찾아보자.

지금 레지스터 16개가 사용되고 있는데

왜 4개에서 16개로 늘어난건지 이해를 못한듯하다.

아

지금 우리는 레지스터 4개만 쓰고 있다.

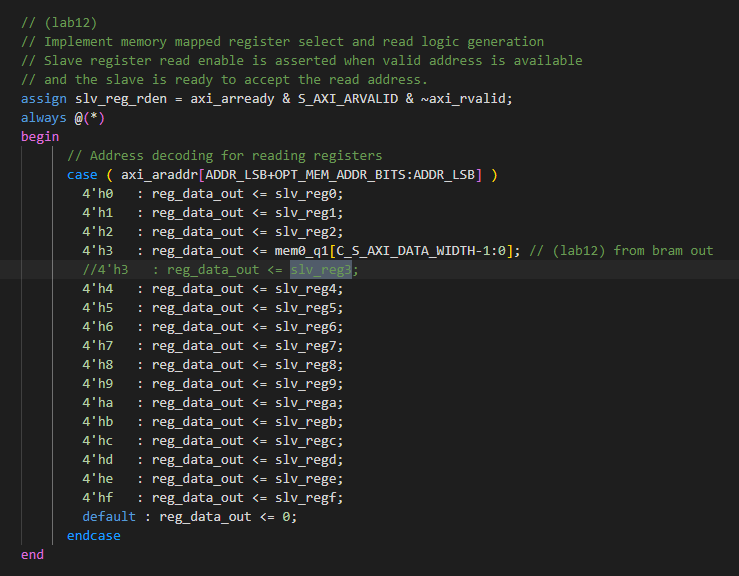

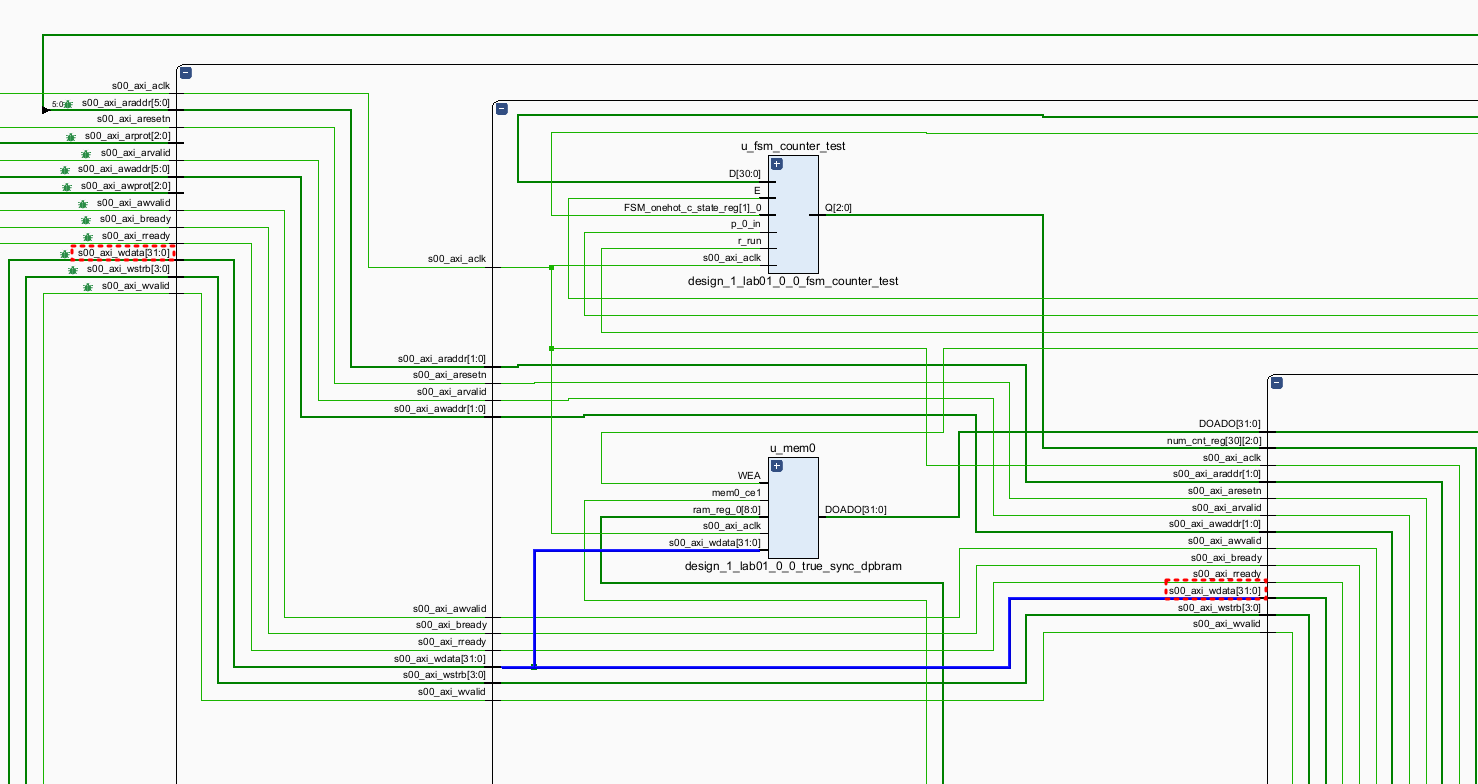

즉 설계모식도에 의하면 slv_reg3 = data register 이다.

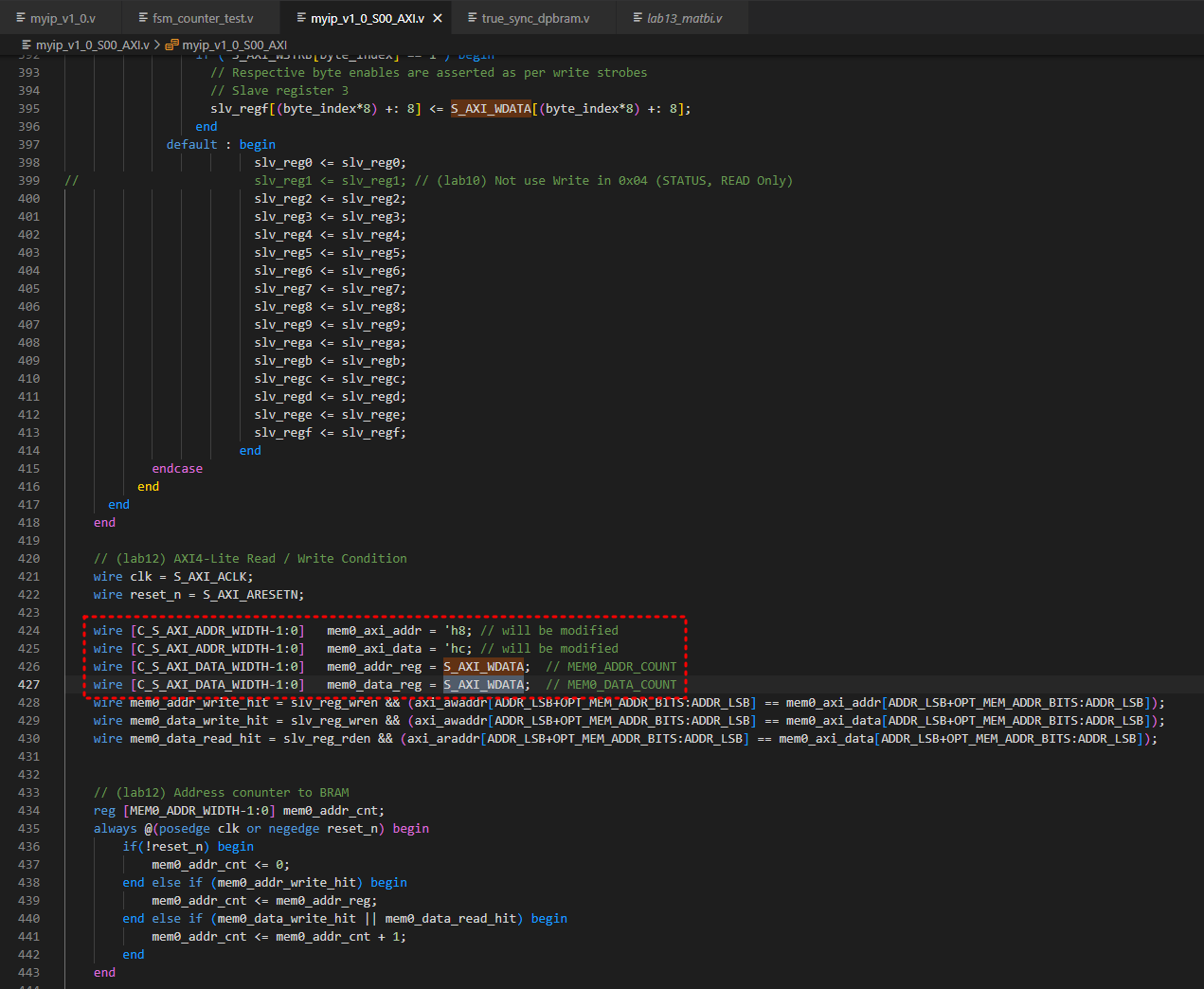

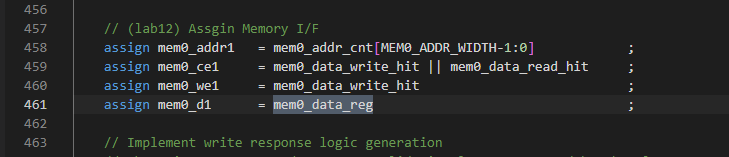

이와 관련된 동작이 write 그리고 read에서 각각 이렇게 구현(implement)되어있다.

S_AXI_WDATA를 버스 슬라이싱해서 사용한다.

이쪽에서 관계가 약간 애매한듯하여 모식을 통해 정리해나갈 수 있도록 하자.

손으로 그리려고 했는데, 이거 손으로 할 수 있는 영역이 아니다.

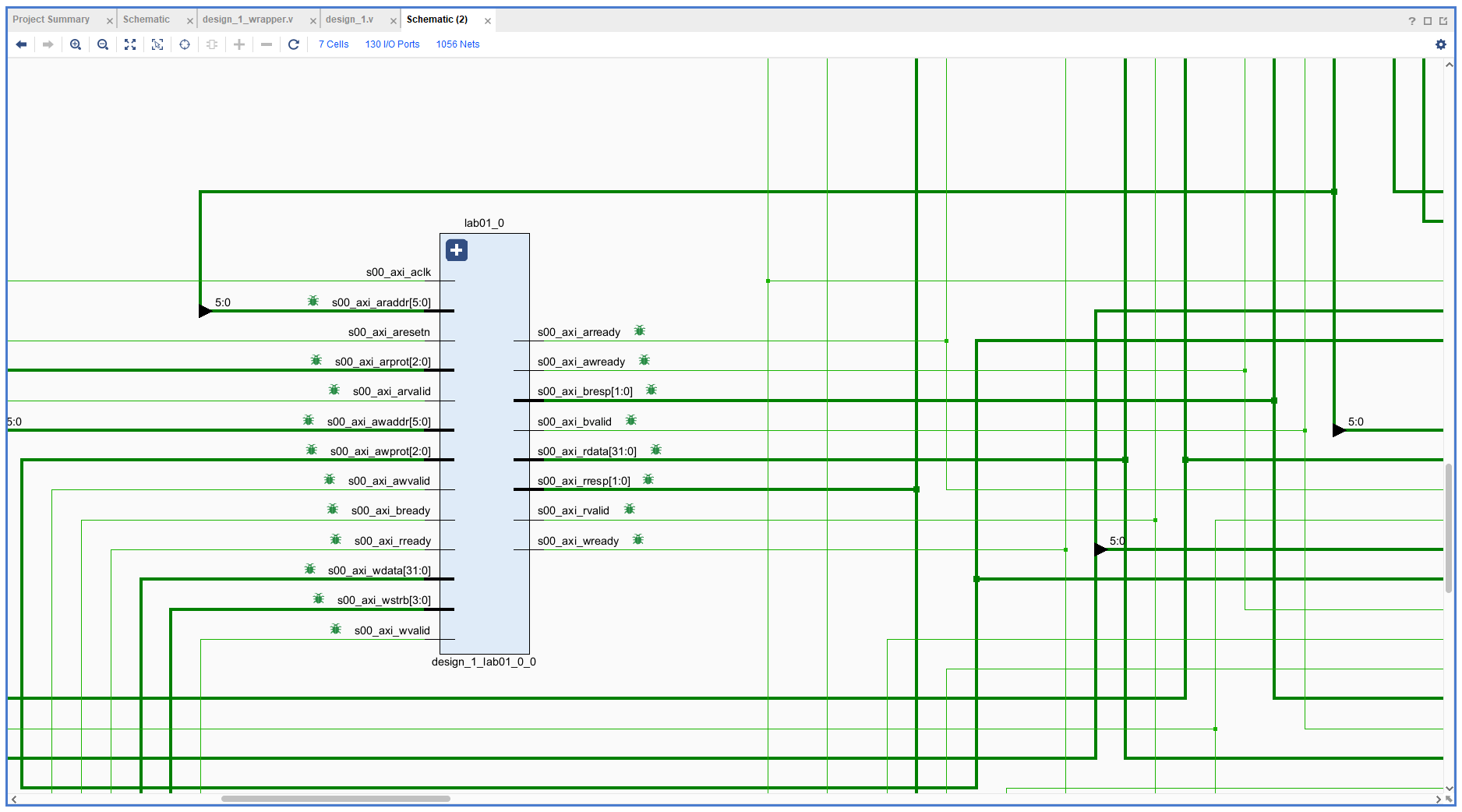

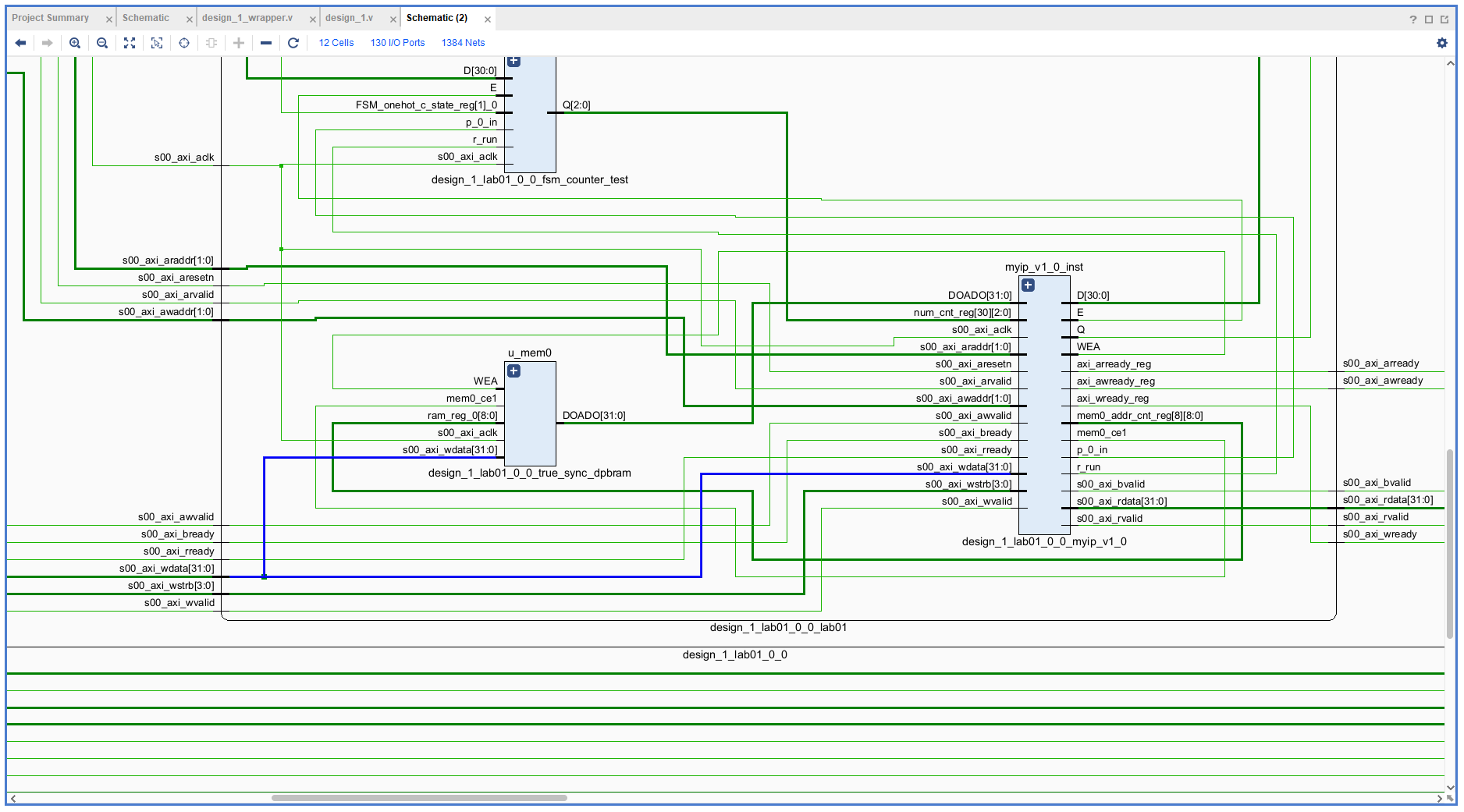

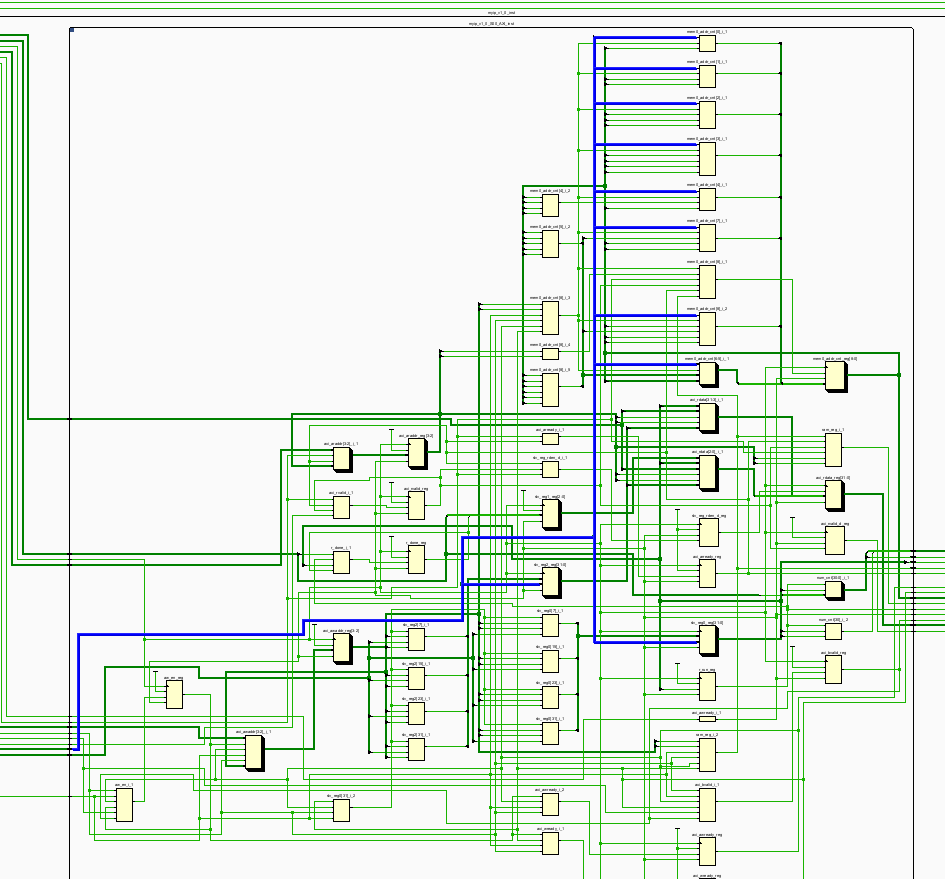

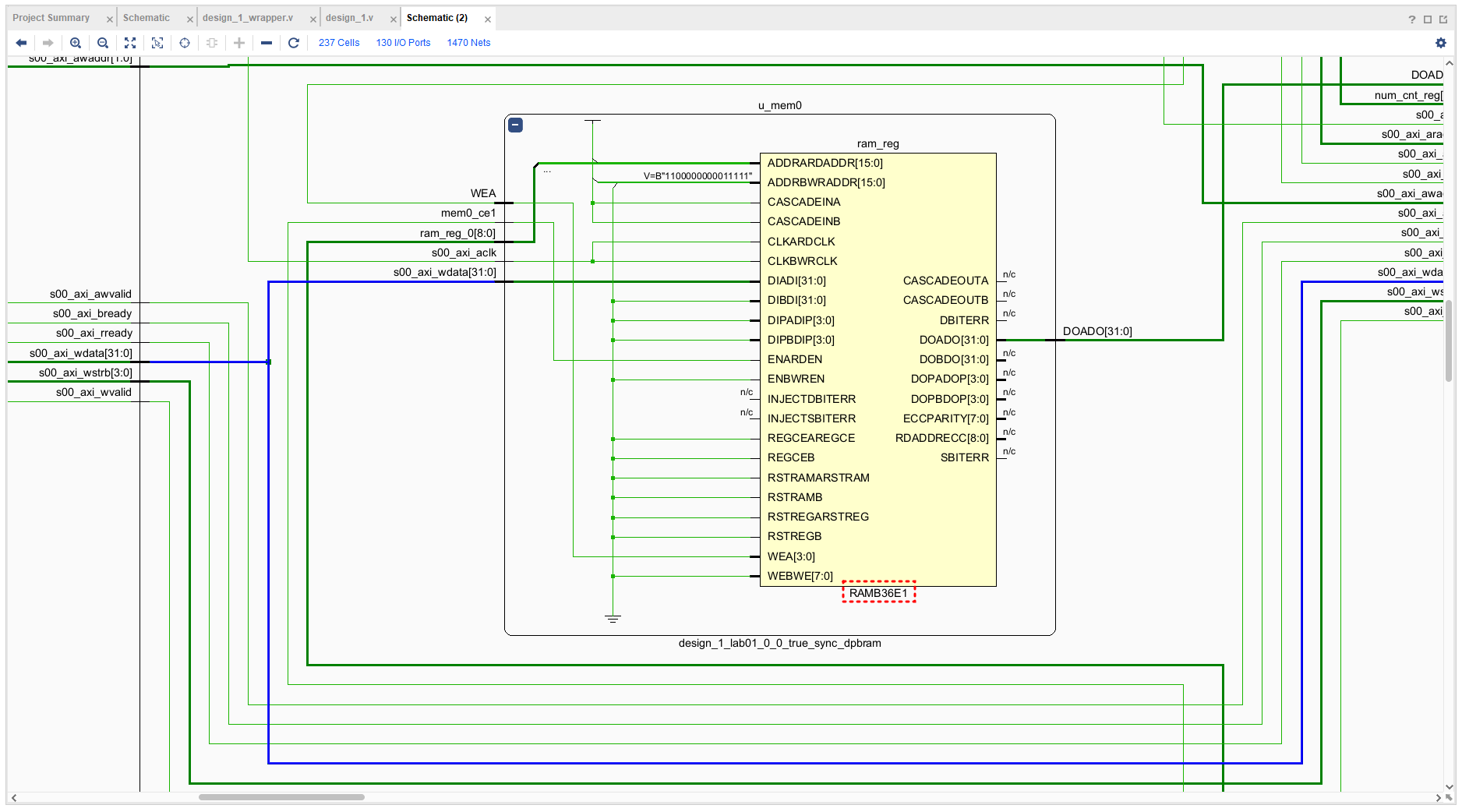

RTL Schematic을 활용해보았다.

이 중에서 얘를 까고들어가자.

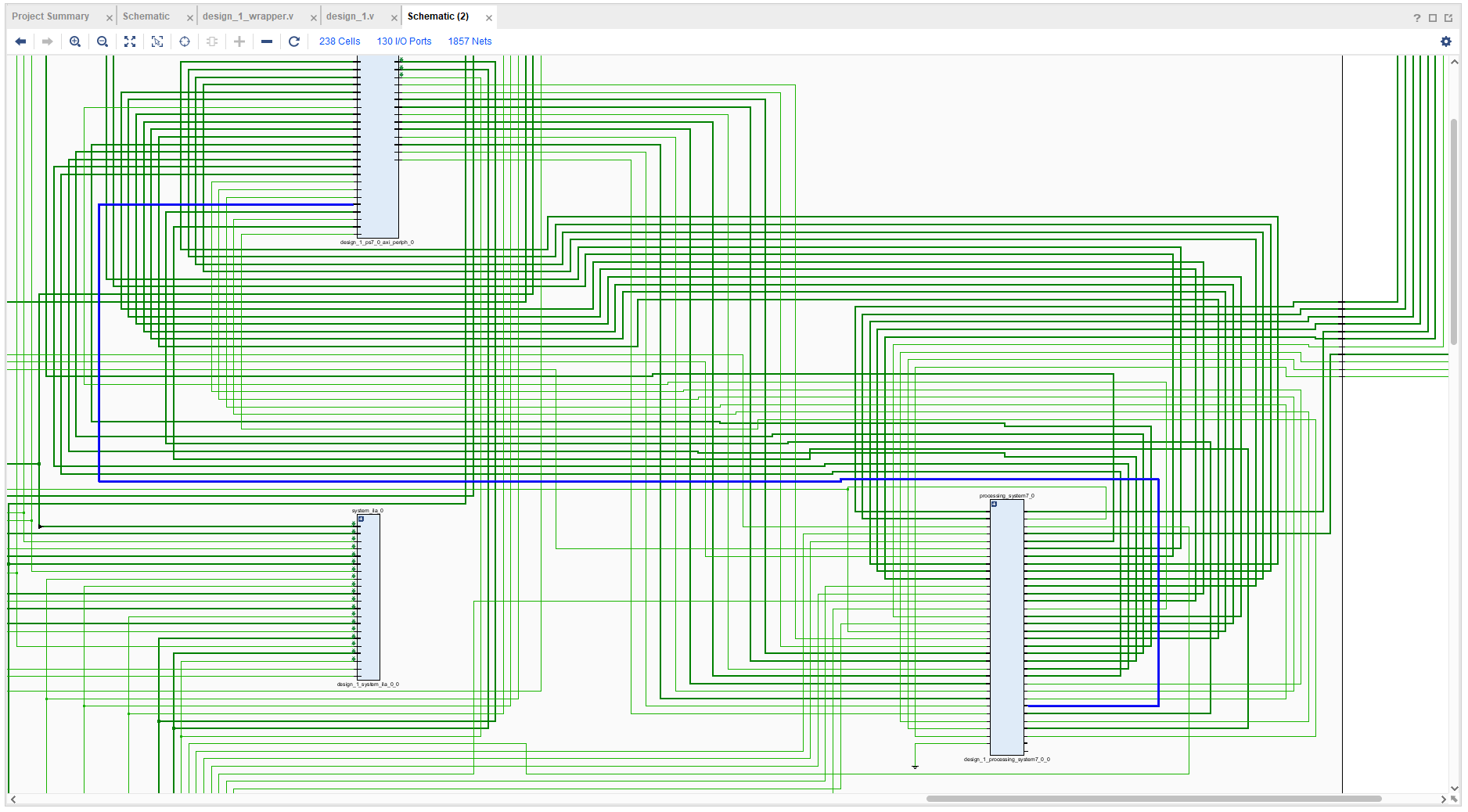

memory와 myip 모듈은 다음과 같이 axi_wdata[31:0]을 통해서 통신하는데

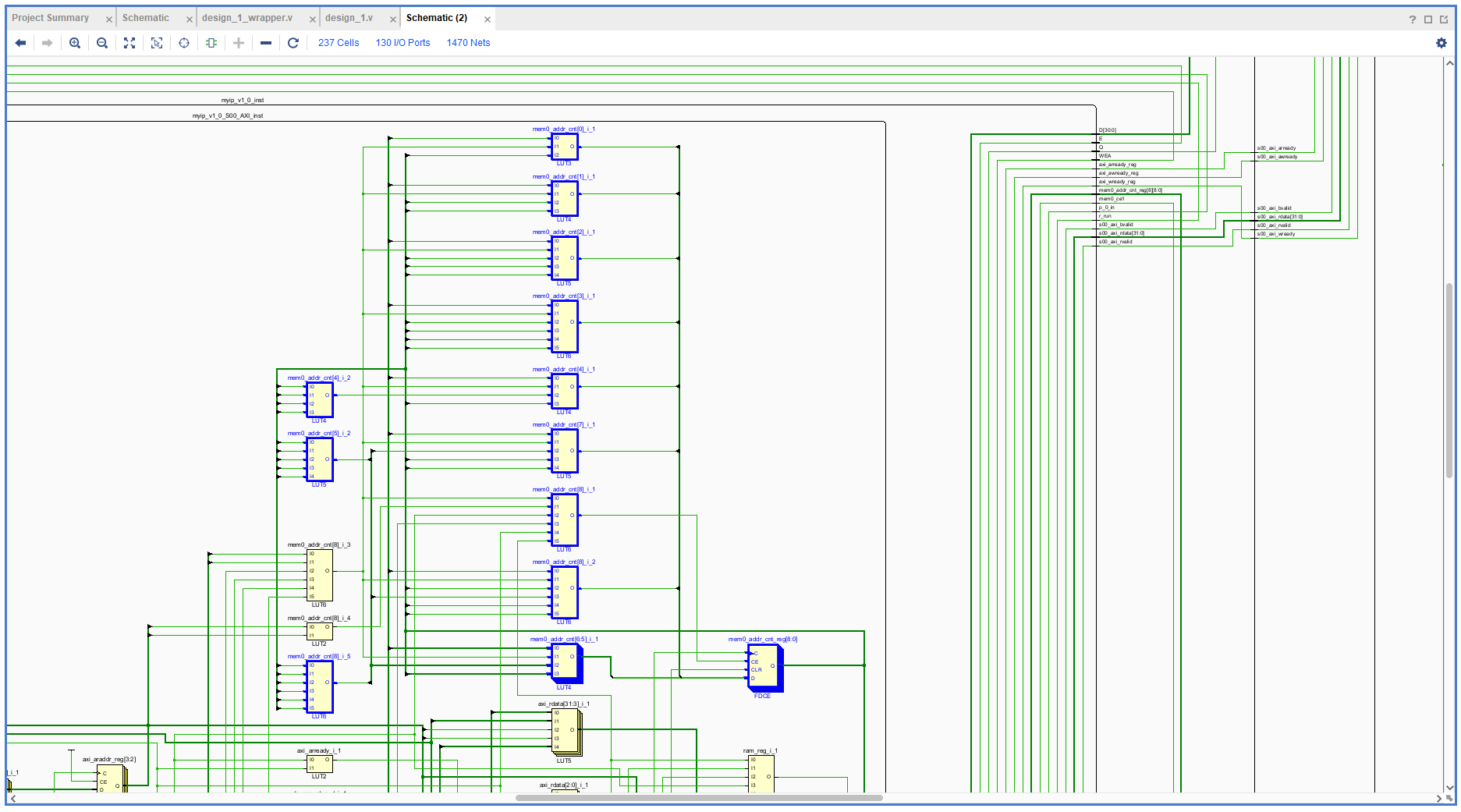

myip를 까면

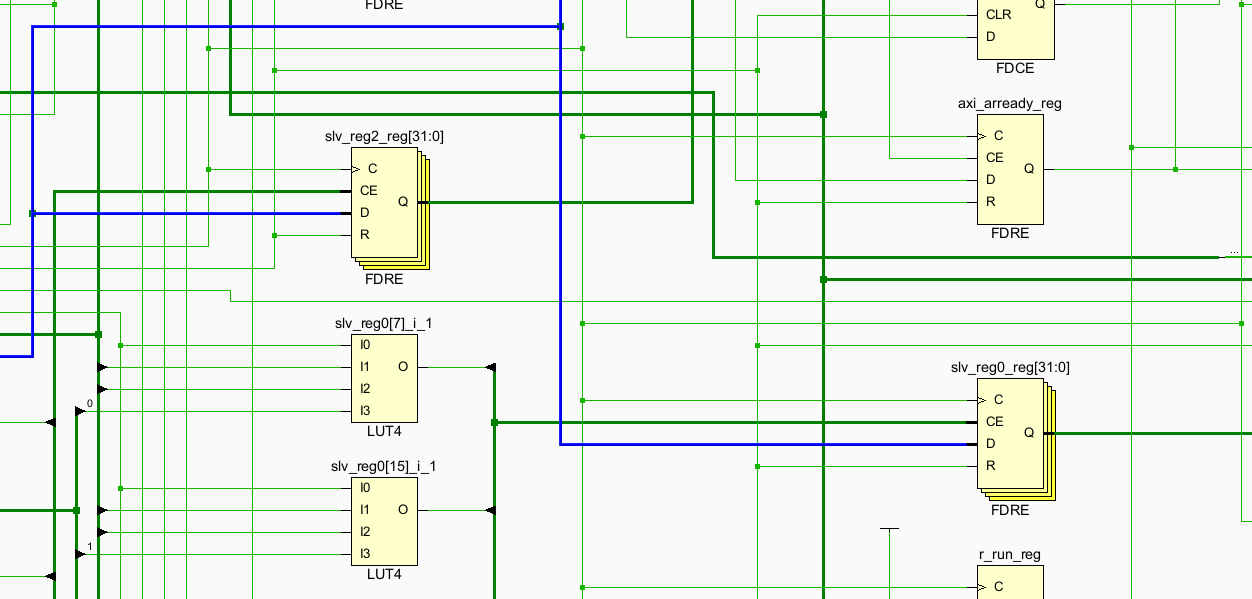

레지스터들이 등장한다!

그래서 axi_wdata와 통신하는 레지스터들은

얘네들인데

안쓰거나 주소와 관련된 레지스터가 너무 많아서 잘 안보인다.

mem과 myip가 연결되는 지점 말고

zynq와 myip가 연결되는 지점을 보자.

zynq와 myip는 직접 연결되지 않고 axi periph를 통해서 연결된다.

myip : axi_periph = S00_AXI_wdata[31:0] : M00_AXI_wdata[31:0]

이때 ila는 무시

아 하긴 그래도 bus라서 결국 같은 지점으로 도착하기는 한다.

소거법을 통해 보면 얘네 둘중 하나다.

위에있는 얘들은 다 addr 관련이다.

이 시점에서 reg0과 reg2의 판단을 위해 위의 모식을 다시한번 참고해도 ... 누군지 잘 모르겠다 흠.

코드를 볼때랑 같은 상황인데

rdata는 명시가 되어있으면서

wdata는 명시가 왜 안되어있지?

무언가 이해못한 게 있는건가?

아 이쯤되서 다시 timing diagram 한번 보고오자.

지금 0,1,2,3, ...를 만드는 것은 wdata[31:0]이다.

하 근데 그래도 상황은 똑같긴 하다.

중간에 메모

현재 내부에 쓰인 BRAM의 이름은 다음과 같다. RAMB36E1 (연관 키워드 RAMB18E1)

https://docs.xilinx.com/r/en-US/ug953-vivado-7series-libraries/RAMB36E1

RAMB36E1 - 2022.1 English

Primitive: 36K-bit Configurable Synchronous Block RAM Introduction 7 series devices contain several block RAM memories that can be configured as FIFOs, automatic error correction RAM, or general-purpose 36 Kb or 18 Kb RAM/ROM memories. These block RAM memo

docs.xilinx.com

문제가 잘 풀리지 않는다.

다시 지금 내가 데이터 레지스터를 찾는 목적을 상기해보자.

myip_v1_0_S00_AXI 모듈 내부에 있는 Memory I/F Ctrl 레지스터에 대하여 파악하기 위함인데.

(참고로 얘 또한 레지스터가 맞다.)

코드에서 그 동작이 잘 보이지 않는다.

이 생각을 하고보니

지금 여기서 얘(네)가 addr를 다루기는 하지만 Ctrl 일수도 있겠다 싶다.

내부 구조에 대한 파악은 이 정도로 하고

다시 다음 목표로 넘어가보자.

'적극적 생각 > FPGA' 카테고리의 다른 글

| FPGA BRAM에 데이터 저장 (2) 주소문제 해결하기 (3) (0) | 2022.07.24 |

|---|---|

| FPGA BRAM에 데이터 저장 (2) 주소문제 해결하기 (2) (0) | 2022.07.23 |

| ILA PG172 Document : Integrated Logic Analyzer v6.2 LogiCORE IP Product Guide Vivado Design Suite PG172 October 5, 2016 (0) | 2022.07.23 |

| FPGA BRAM에 데이터 저장. (0) | 2022.07.23 |

| ieeexplore.ieee.org (0) | 2022.07.23 |