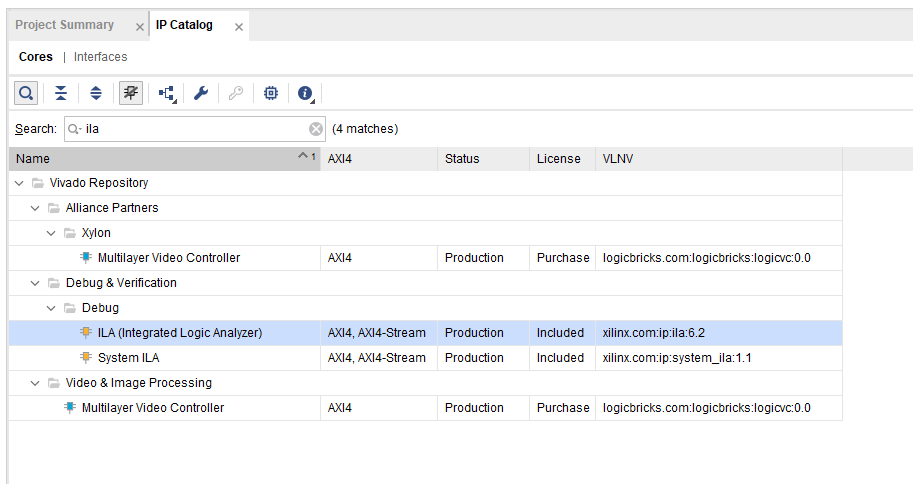

메뉴바의 IP Core를 이용해 ILA 모듈을 가져오자.

우선 이 core의 사용법을 알고싶은 것이기 때문에

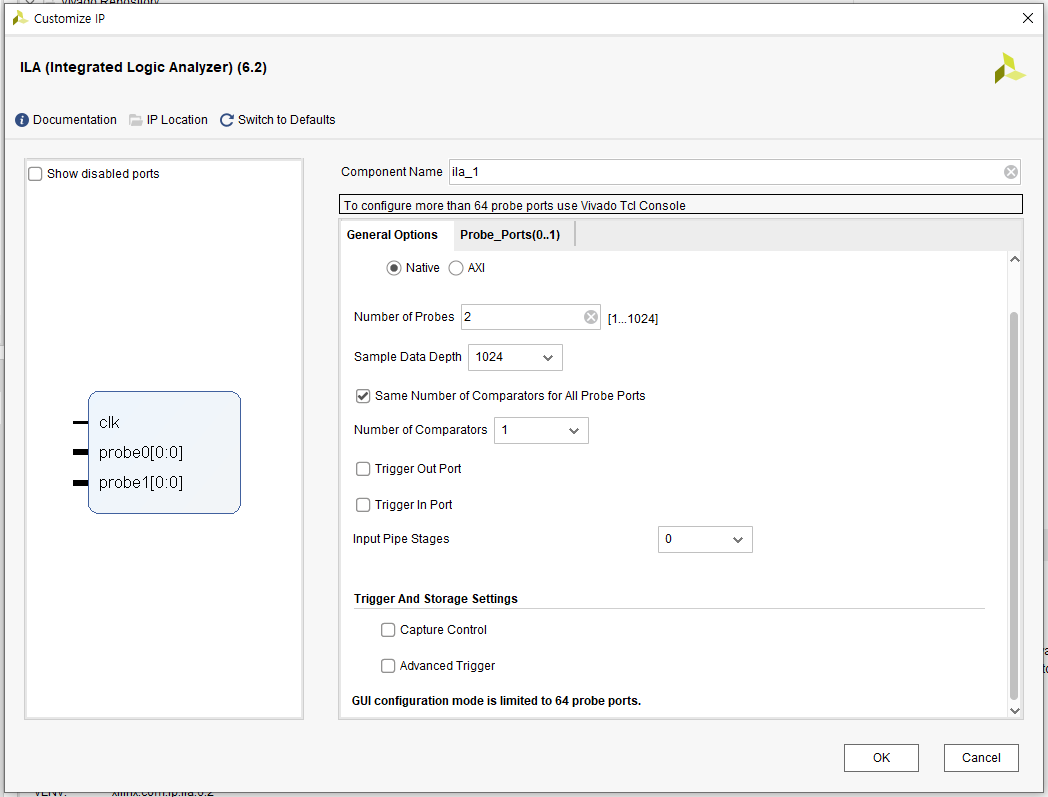

probes를 2개 정도로 설정해보자.

data depth는 그대로.

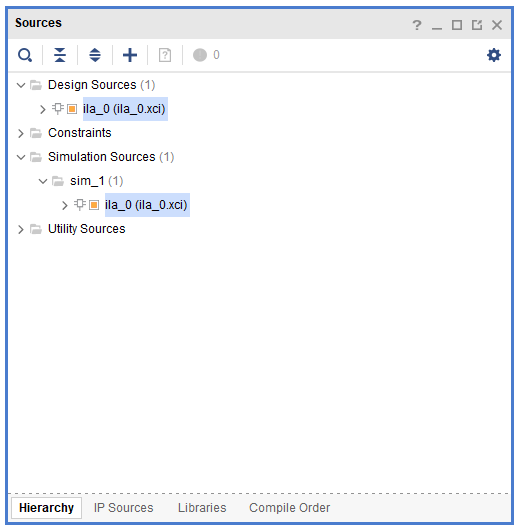

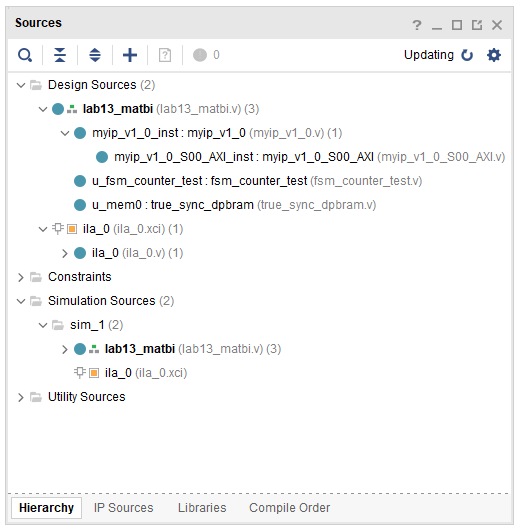

생성이 되었다.

근데 예상했던 .v가 아닌 .xci 파일이 생성된다.

수정하지 말고 포트만 갖다 쓰는것이 목적인가보다.

얘를 적당한 곳에 직접 wiring 해주면 되나보다.

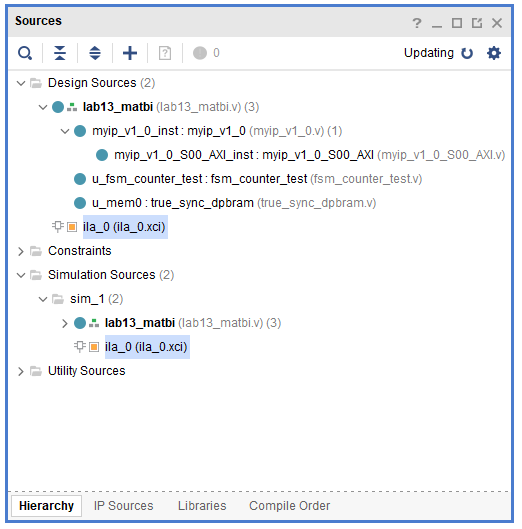

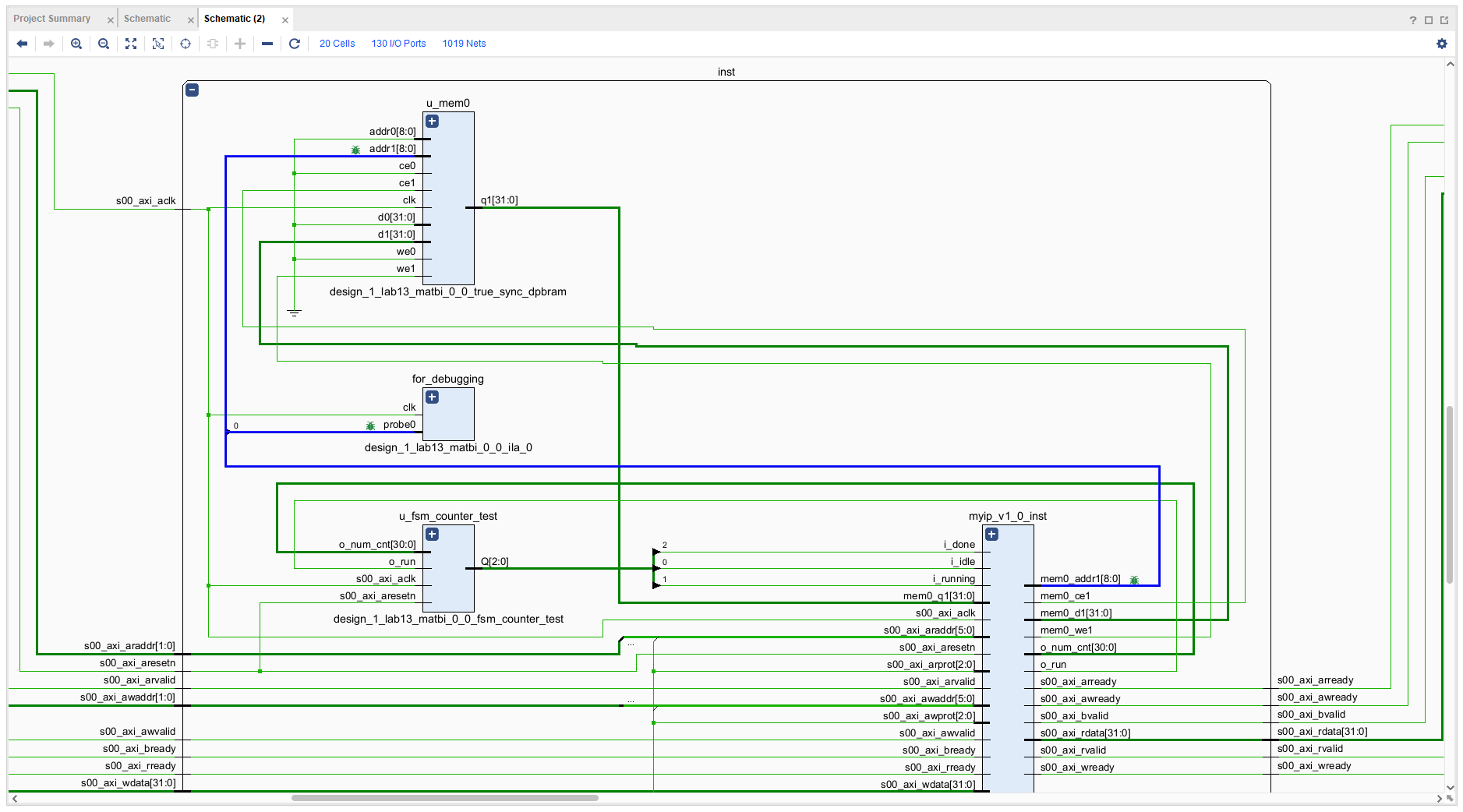

top모듈과 그 아래의 모듈들을 가져왔다.

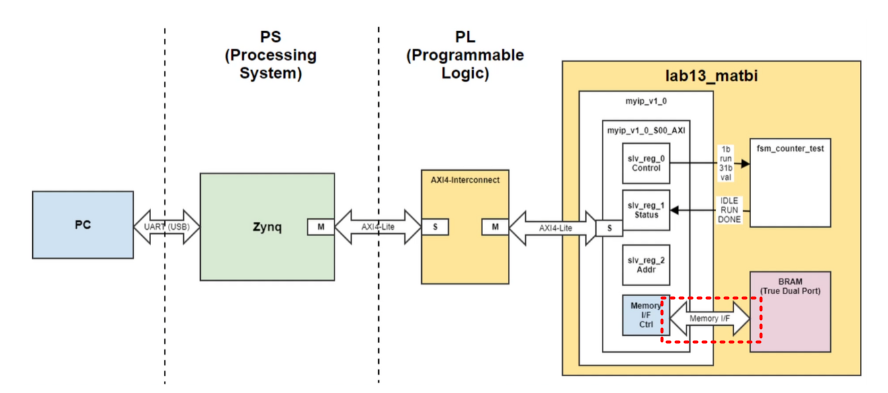

모식도상에서 연결해야할 지점은

이 빨간 네모박스 지점으로 추측된다.

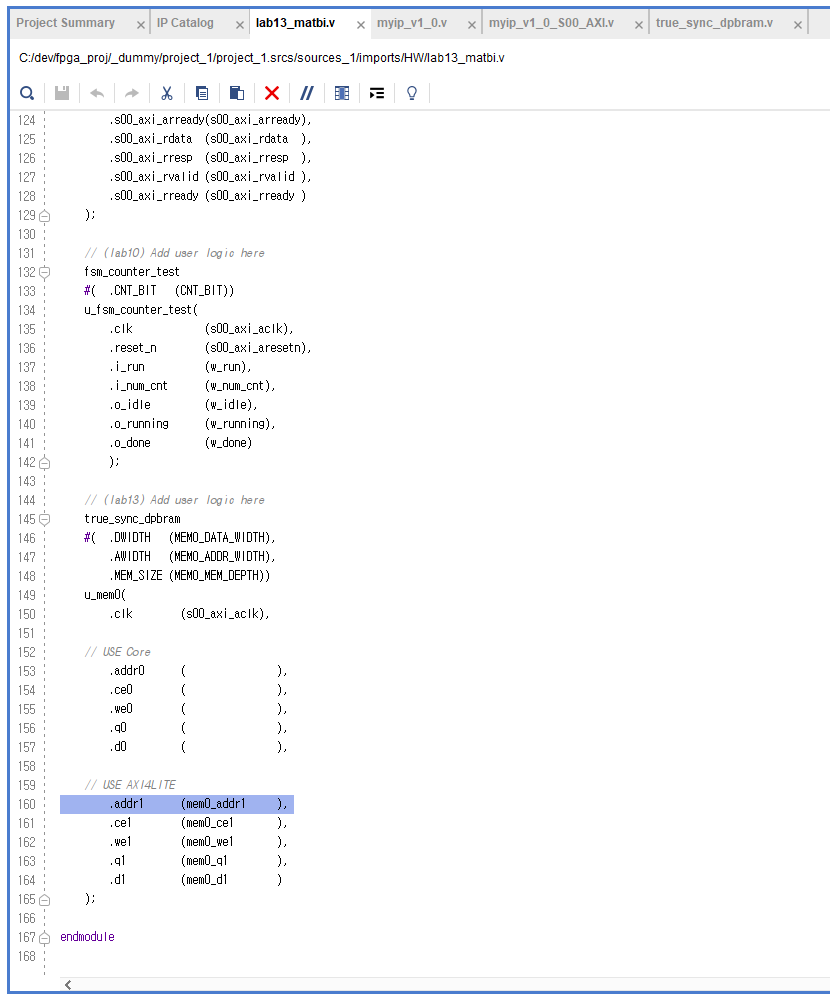

코드상에서 찾아보면 이 지점으로 추측된다.

① 하지만 .v가 아닌 .xci 파일을 여기 addr에다가 wiring하는 방법에 대해서는 모르겠다.

② 그리고 내가 궁금한 신호는 addr이 아니고 '합성후'에 생기는 netlist상의 ADDRARDADDR이다.

===

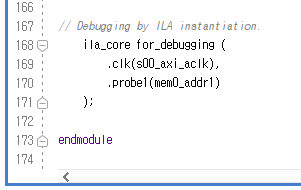

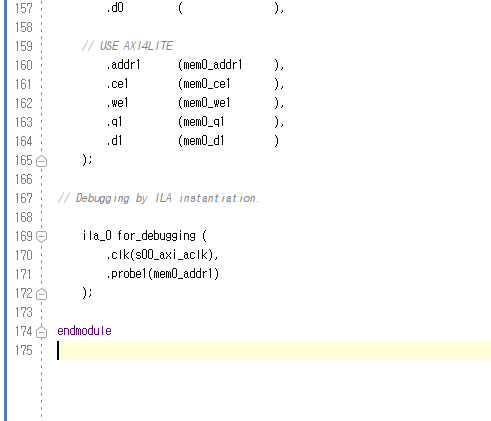

다음과 같이 ila를 instantation 및 wiring 해주면 된다.

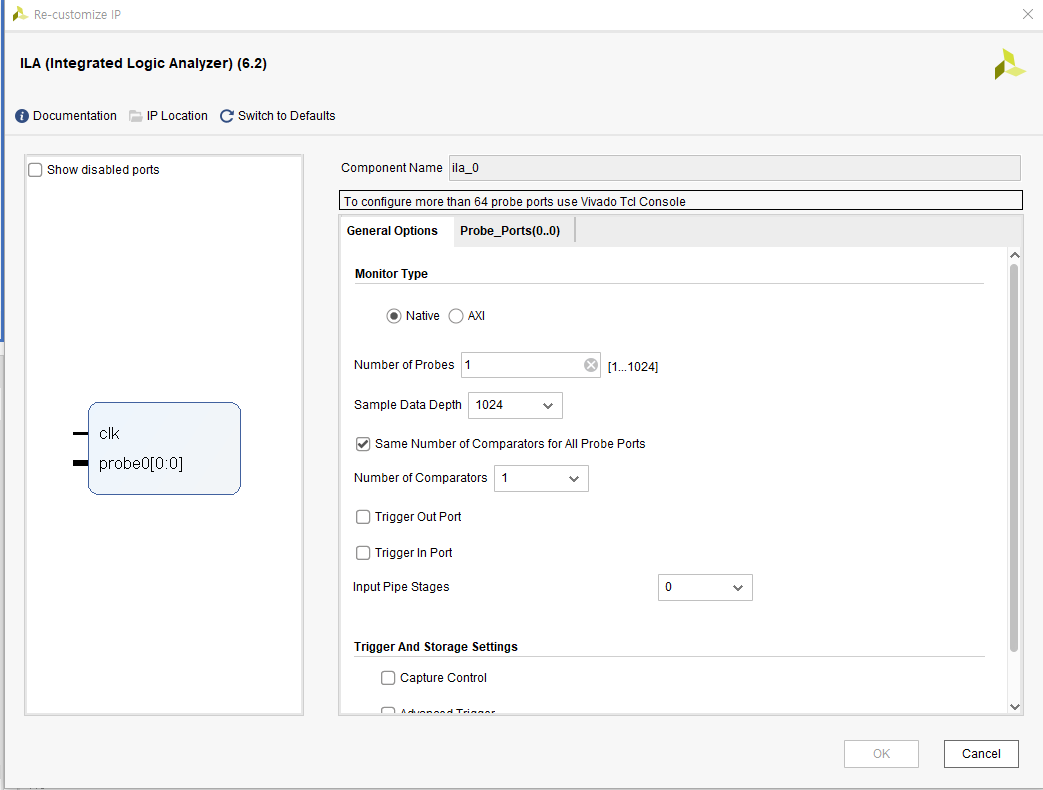

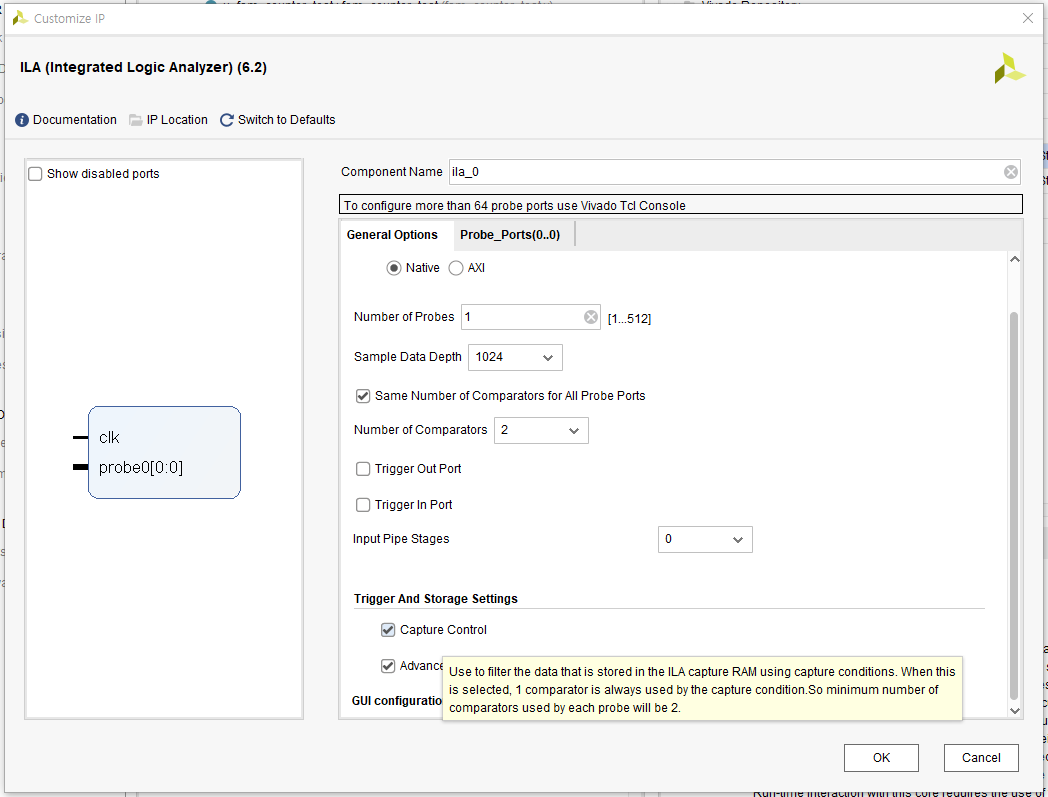

이때 ila를 다음과 같이 recustomize 해준다.

Data Depth는 32bits면 충분한데, 1024가 최소다.

probe 신호는 1개로 줄여 probe0만 사용한다.

ila 내부는 다음과 같이 되어있다.

(무의미해서 코드첨부 삭제)

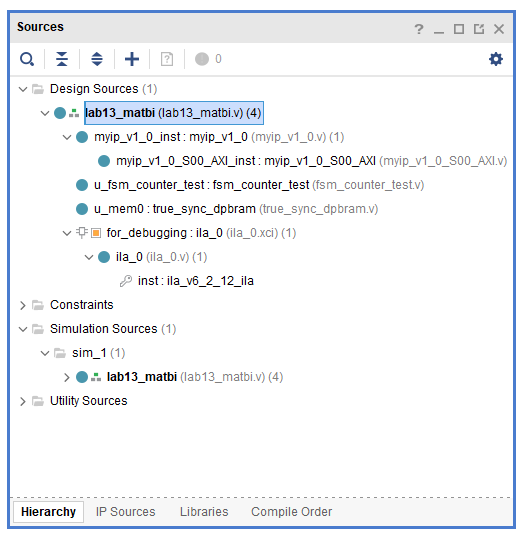

Hierachy도 잡힌것을 확인했다.

ip package를 만든다.

block design 구성해서

wrapper로 싸고

bitstream 만들고

export 한다.

그리고 vitis가서 실행한다.

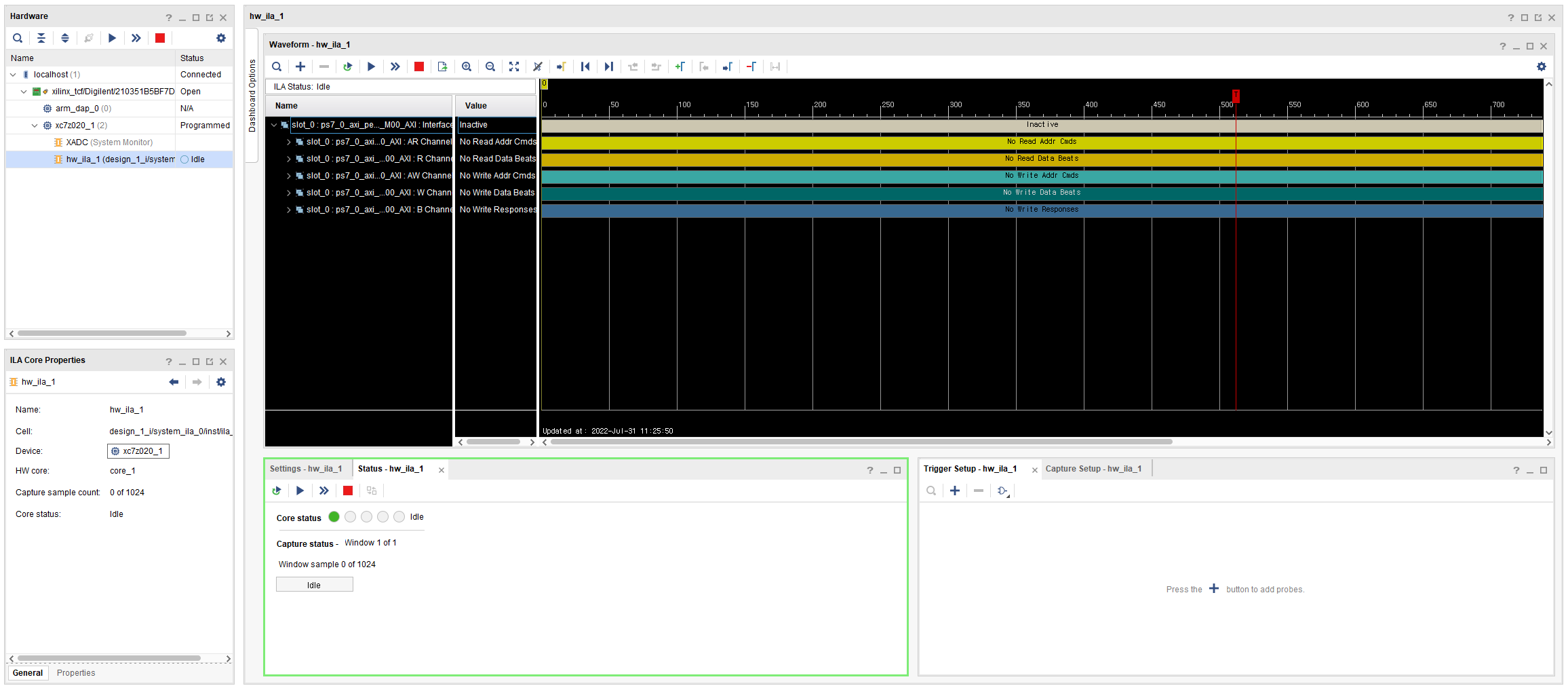

그리고 ila trigger 관찰한다.

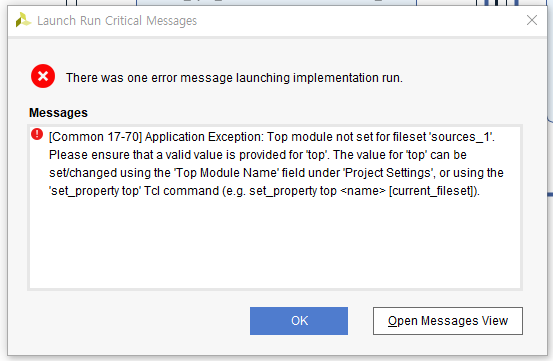

[bitstream 만드는 과정의 에러가 하나 떴는데 확인하고 넘어가자.

[Common 17-70] Application Exception: Top module not set for fileset 'sources_1'. Please ensure that a valid value is provided for 'top'. The value for 'top' can be set/changed using the 'Top Module Name' field under 'Project Settings', or using the 'set_property top' Tcl command (e.g. set_property top <name> [current_fileset]).

Wrapper로 싸지 않고

Bitstream을 만드려고 해서 생긴 문제다.

Error: [Common 17-70] Application Exception

support.xilinx.com

으악!

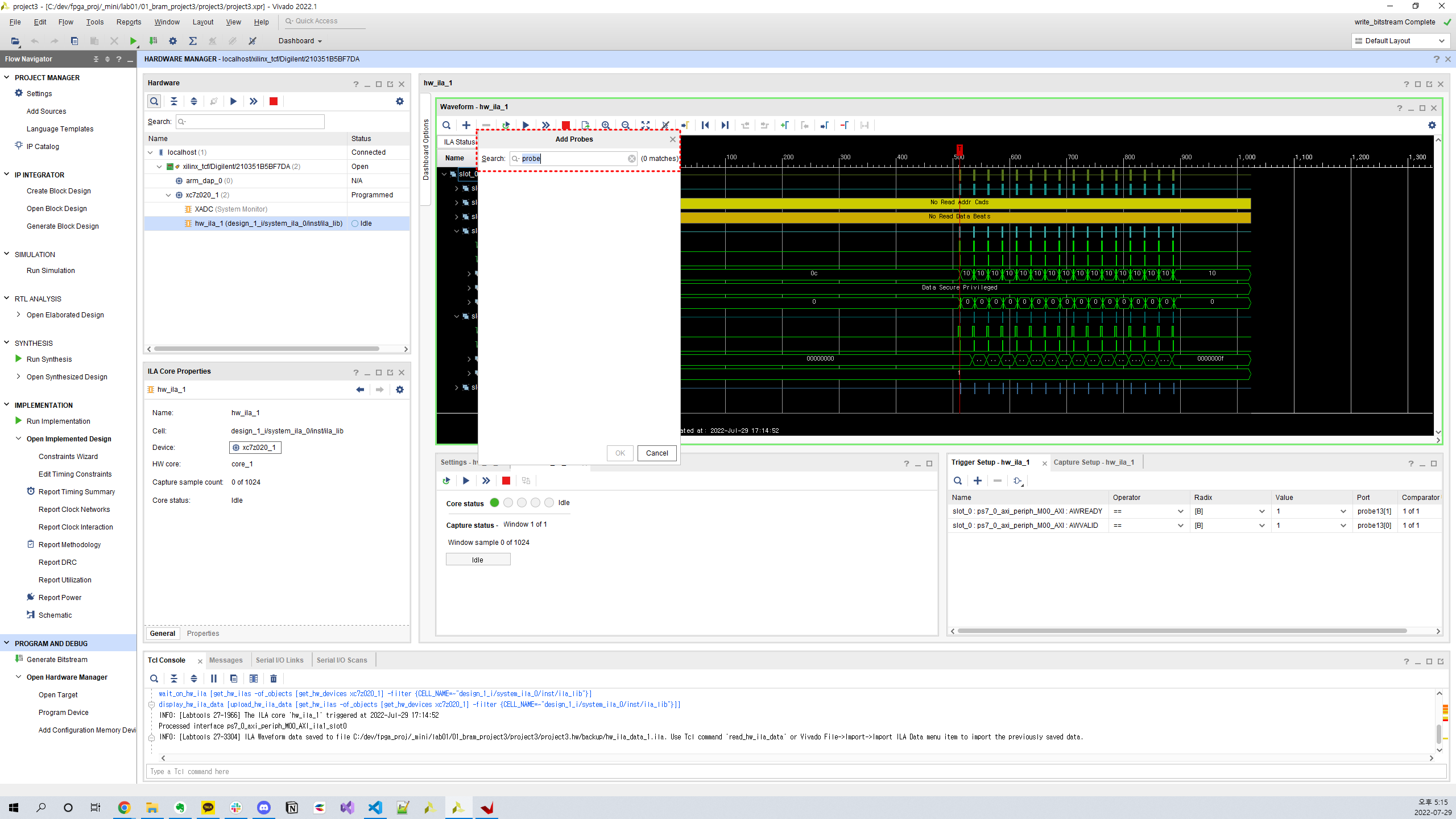

아직도 probe가 뜨지 않는다.

이상하다.

schematic으로 까본다.

for_debugging 모듈이 정상적으로 생긴것을 확인할 수 있다.

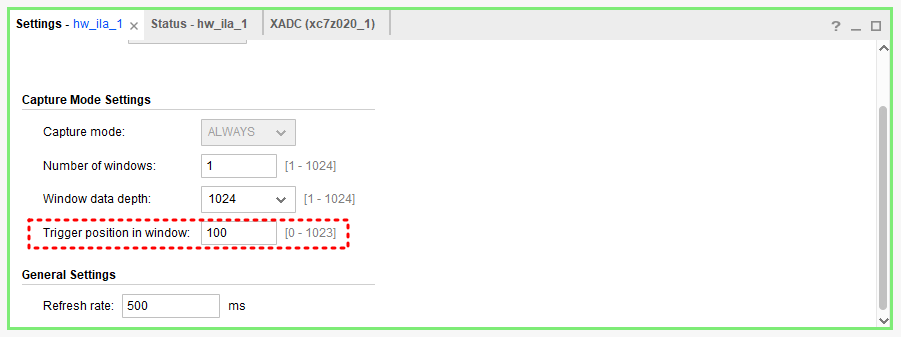

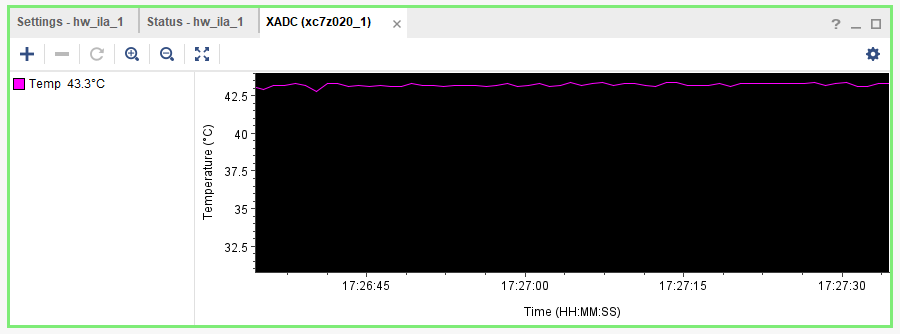

(Hardware Manager를 만지작거리다가

- Trigger 시점을 조절하는 방법

- XADC 보드의 온도 등을 표출하는 System Monitor를 대시보드에서 확인하는 방법

이 두가지에 대해서 짜잘하게 익혔다.)

=====

다시 project를 생성해서

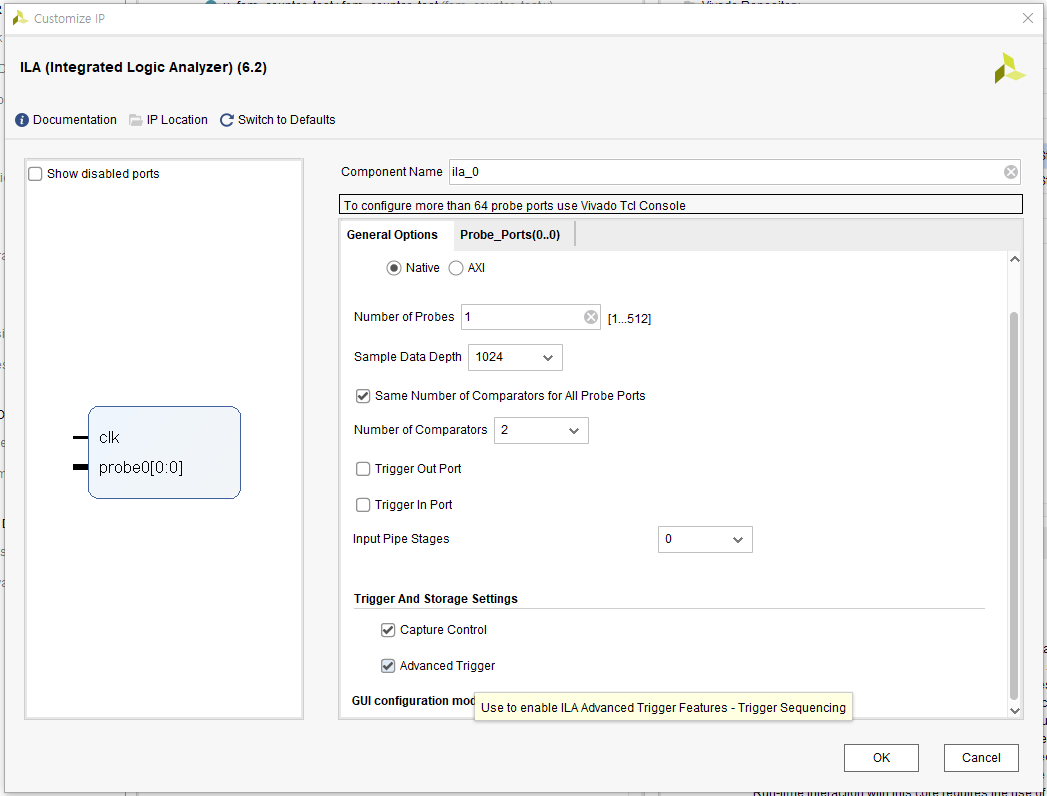

두가지 옵션을 수정해본다.

하나는 capture control 이고

하나는 advanced trigger 이다.

우선 capture control을 쓰기 위해서는

probe가 1개가 아니라 2개가 필요하다.

추가적인 학습이 필요해보이므로

(또한 condition에 대한 capture라서 굳이 필요 없어보이기는 한다.)

우선 advanced control만 켜두고

ila trigger에서 조회되는지 확인해보자.

(wrapper로 싸는 이유에 대해서는 추가적인 공부거리가 있다.)

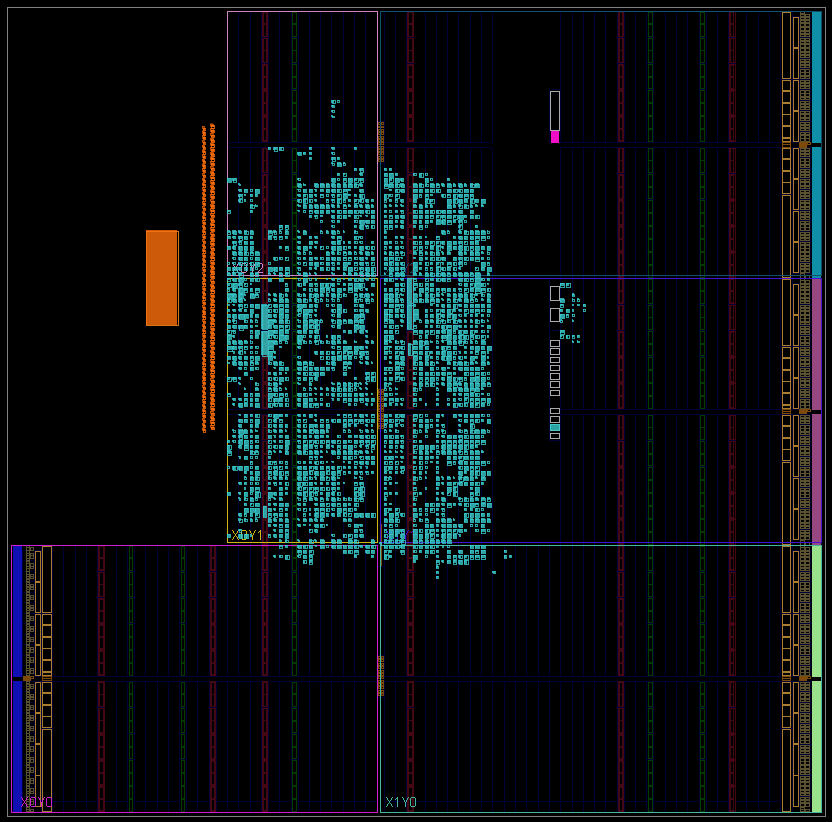

우선 비트스트림 단계에서는 기존보다 훨씬 많은 리소스가 쓰이는것이 가시적으로 보인다.

그리고 vitis로 옮겨서 실행했는데

probe 신호도 조회되지 않고

trigger도 기존과 같은 정상작동을 하지 않는다.

어떤 문제가 있는걸까

음 우선 이 시점에서 다시 한번 질문도 올려둔다.

https://www.inflearn.com/questions/609713

Probe by ILA Instantiation - 인프런 | 질문 & 답변

안녕하세요. 지난 질문의 연장선상에서 질문을 드립니다. 요약하면, 말씀주신 답변대로 ILA Instantation을 시도중입니다. https://www.inflearn.com/questions/602972 Instantation 시키기 위하여, 두...

www.inflearn.com

으윽 좋은 답변을 받지 못했다.

이거 너무 실무적인 영역이라서 어떻게 풀어야 할지 모르겠는데 ...

'적극적 생각 > FPGA' 카테고리의 다른 글

| 0802 / HW Accelerator (가속기)설계 비밀? 우리가 HW 를 공부해야 하는 이유 (0) | 2022.08.02 |

|---|---|

| design_1_wrapper가 필요한 이유 (0) | 2022.07.31 |

| 질문 요약 (0) | 2022.07.29 |

| FPGA를 통한 DDR3 SDRAM 구동 (0) | 2022.07.27 |

| xilinx 포지셔닝 (0) | 2022.07.27 |