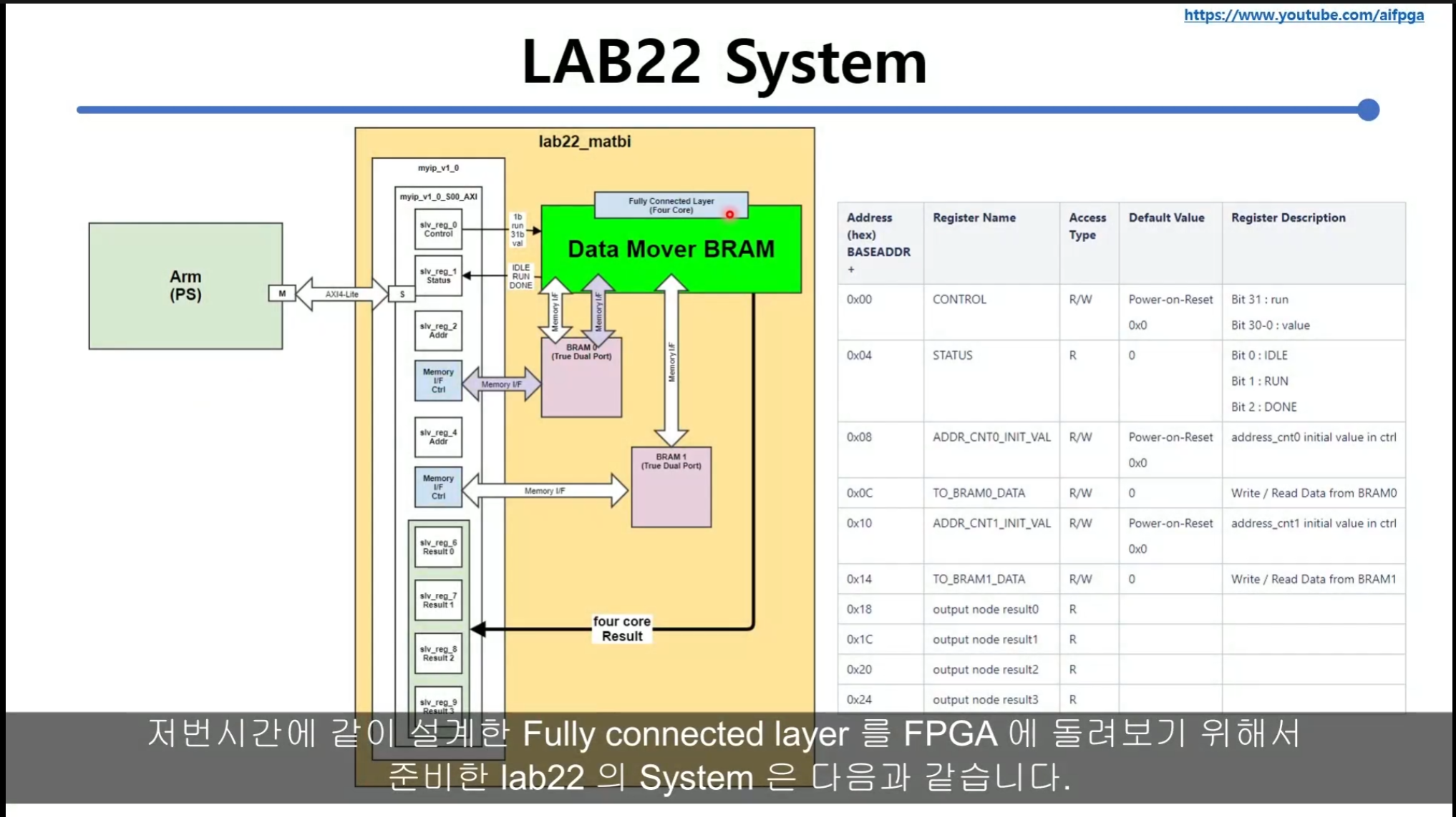

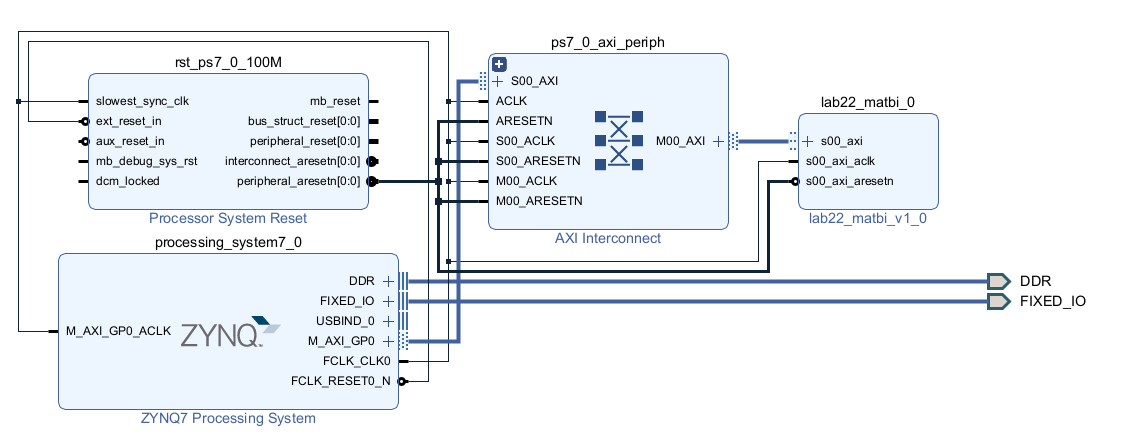

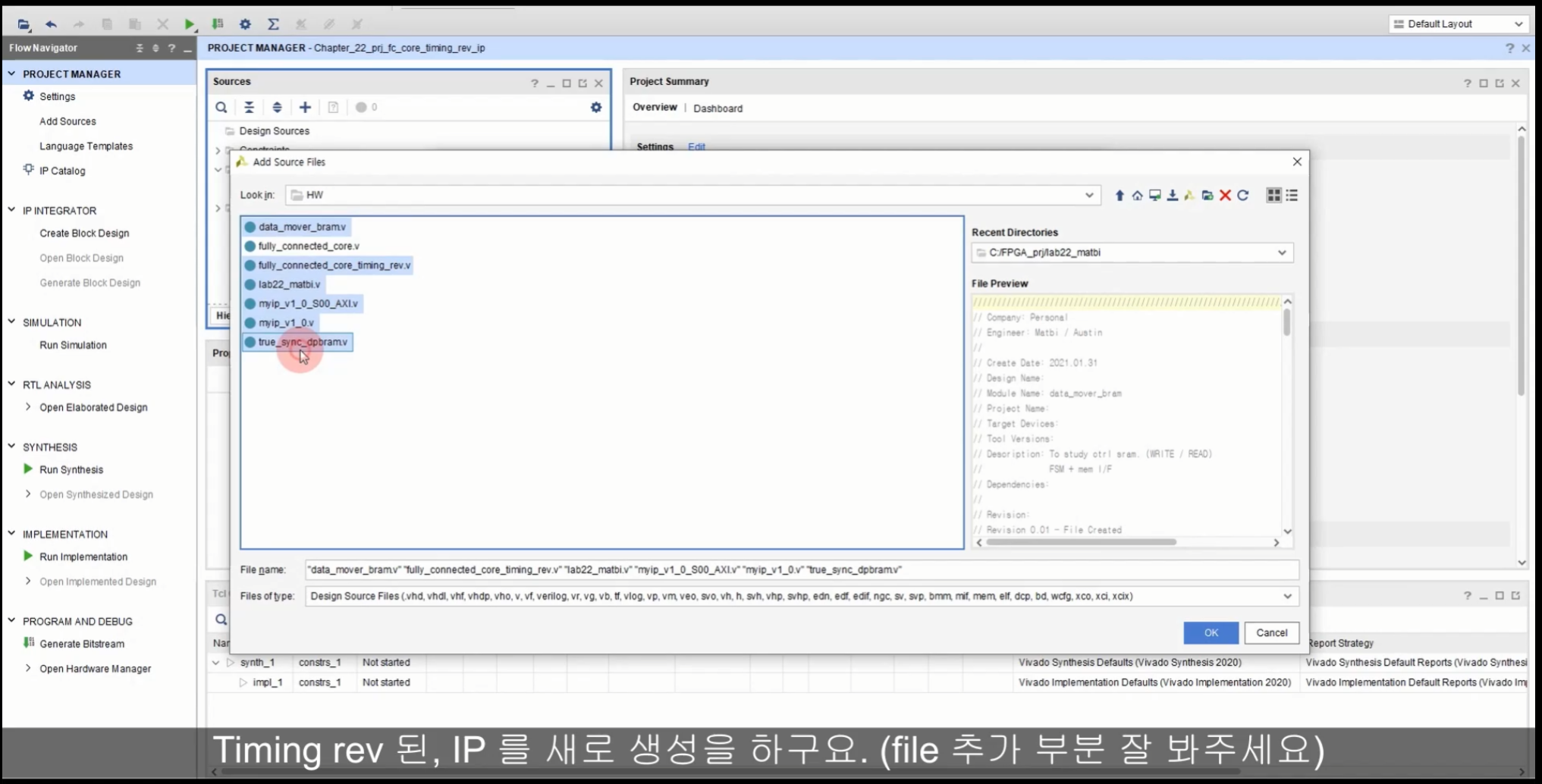

ip

hw = system

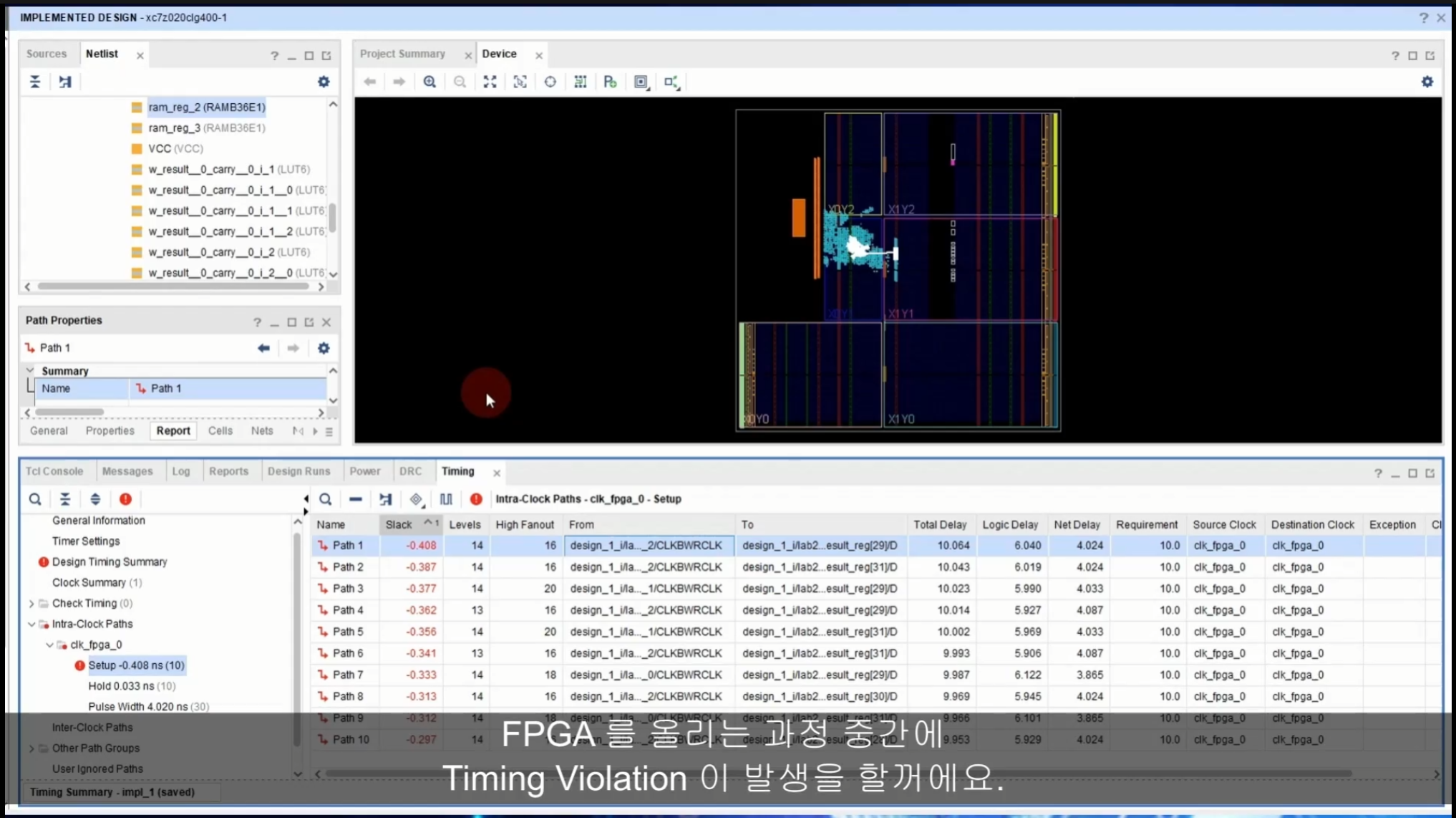

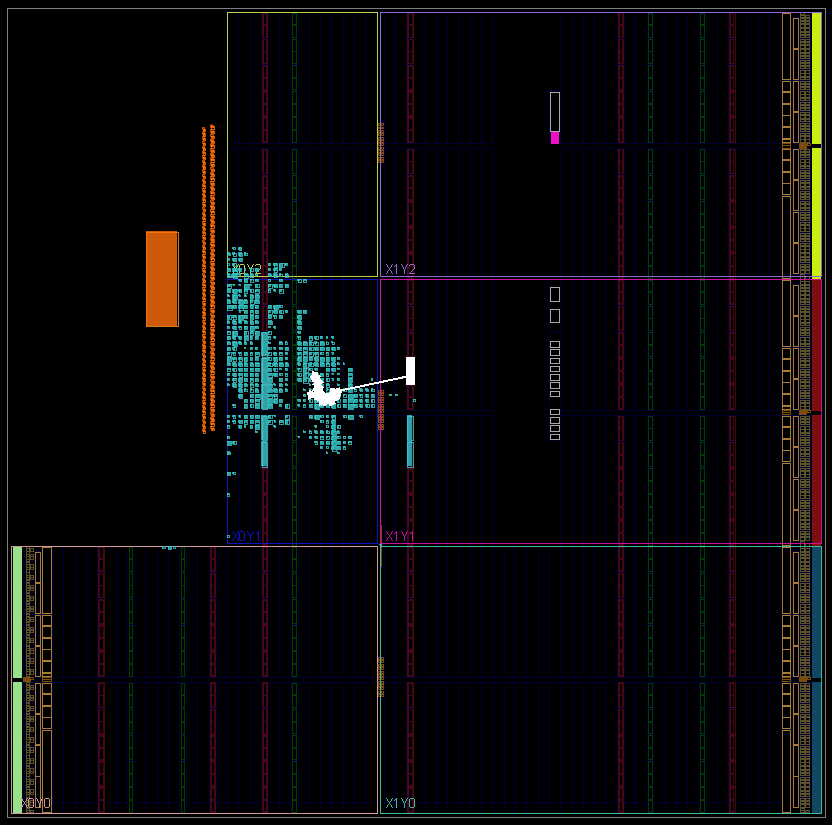

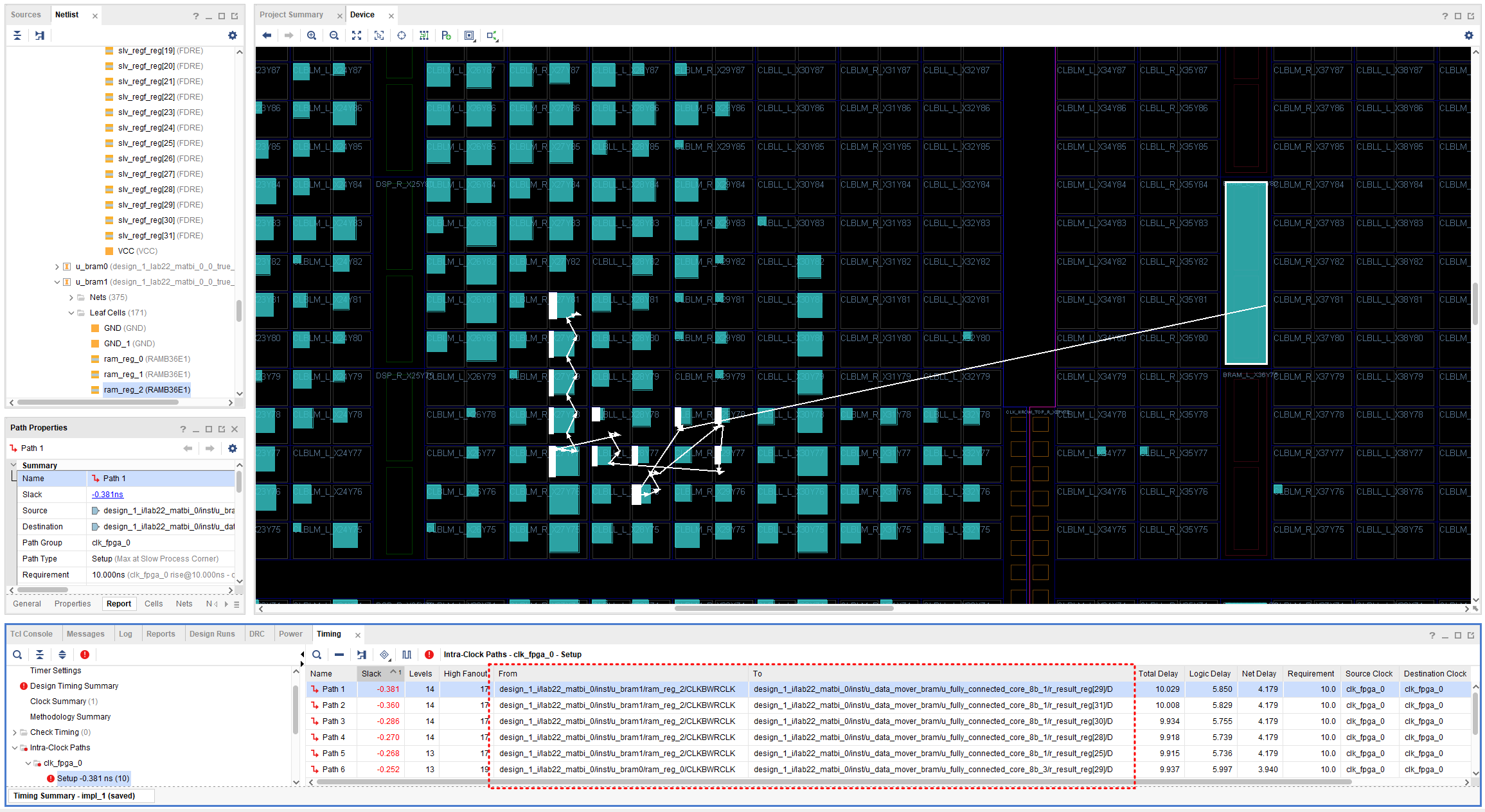

(timing diagram이 발생)

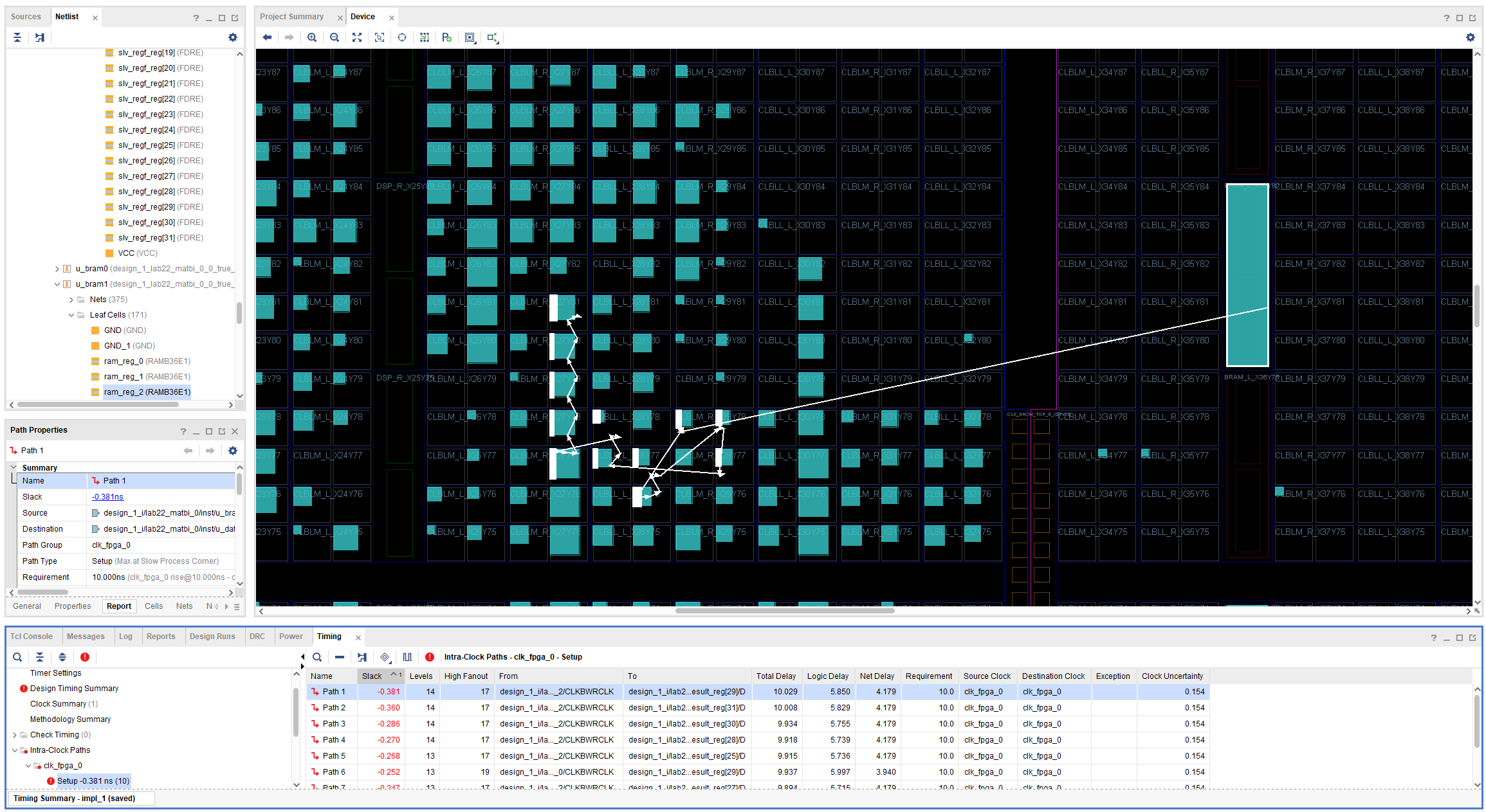

WNS : worst negative slack

TNS : total negative slack

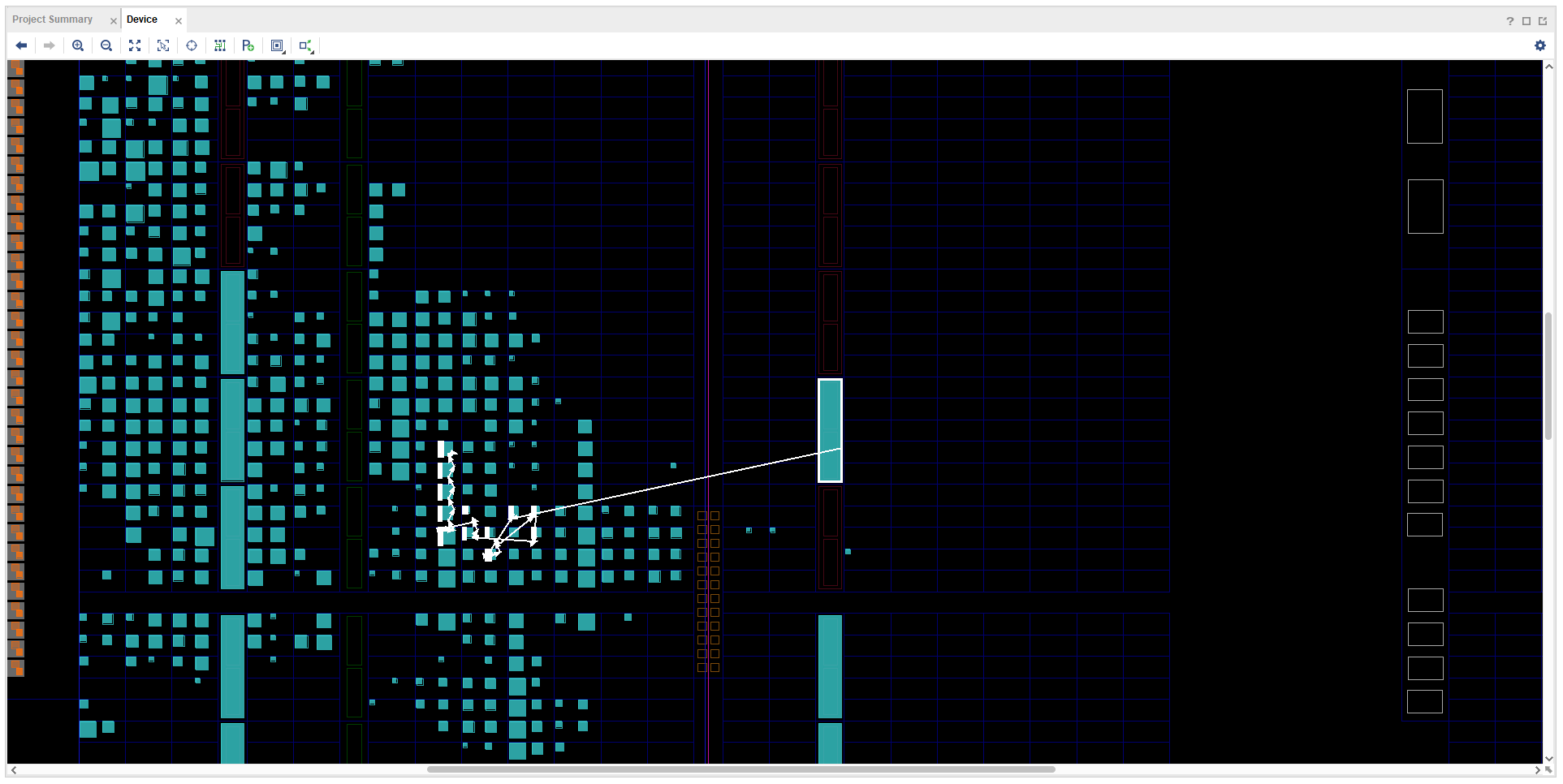

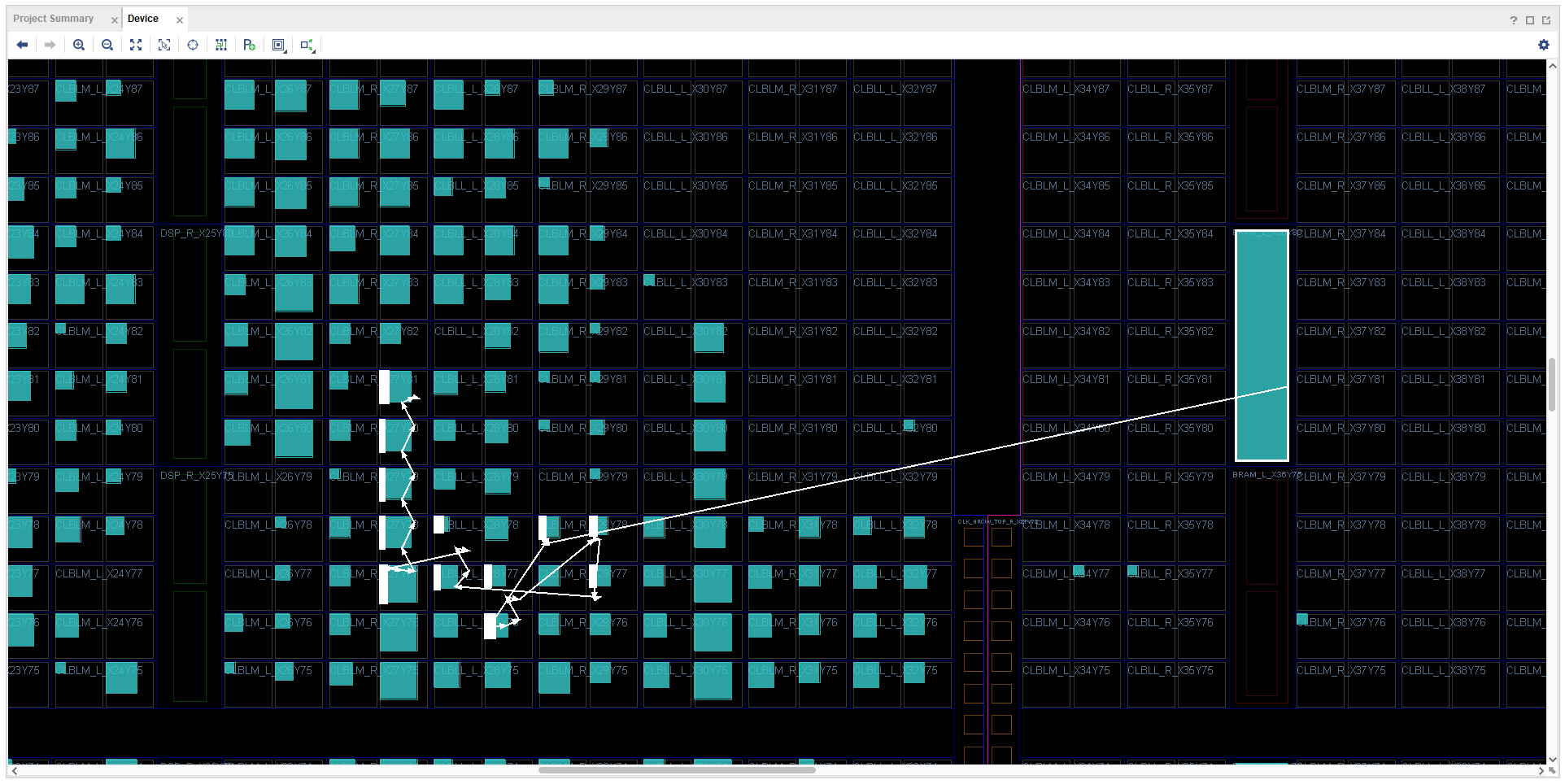

여기서 violation이 발생하고 있는 path를 눌러보면

실제 다이에서 리소스들이 place되고 그것들이 연결된것

다른 path들 눌러보면 다르게 동작하는 것을 알 수 있으며

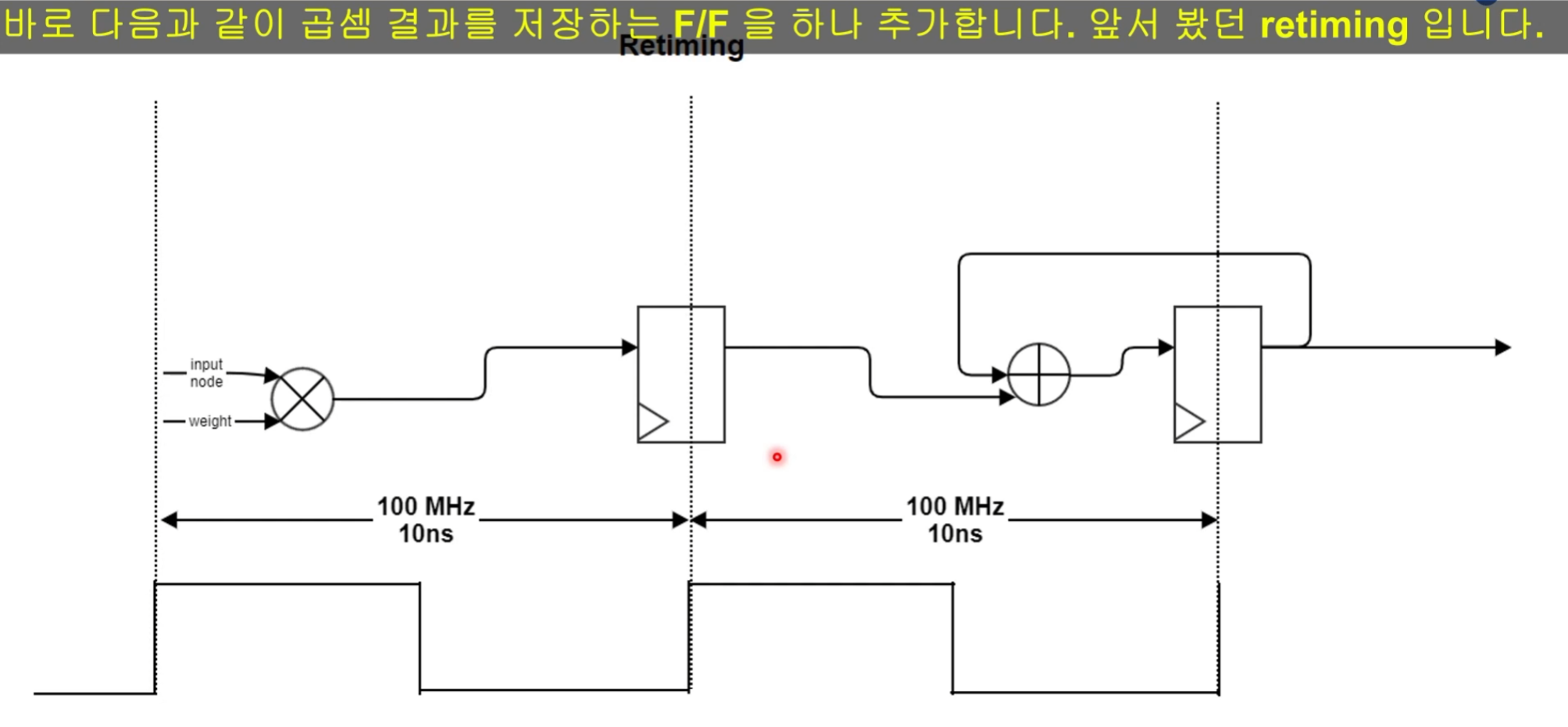

timing violation을 수정하기 위하여

가장 먼저 해야하는것은

critical path를 수정해주는 것이며

WNS가 가장 작은 것 즉 절대값이 가장 큰것에 대하여 수정을 해주어야 하며

수정을 계속 해주면서 timing closure 시켜서 timing met 을 해주어야 한다.

두가지 방법이 있음

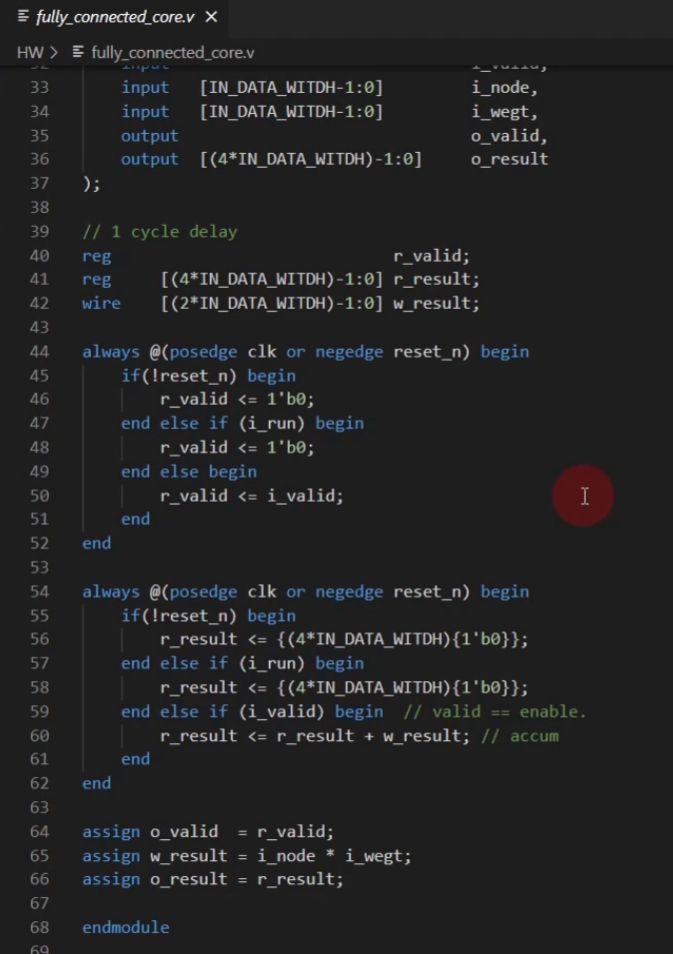

- 직접 verilog hdl을 수정하여 retiming 하는 것이고

- vivado tool이 갖고있는 option을 수정해 violation을 잡는 것이다.

From To를 보면

fully_connected_core에서 violation이 난 것을 확인할 수 있다.

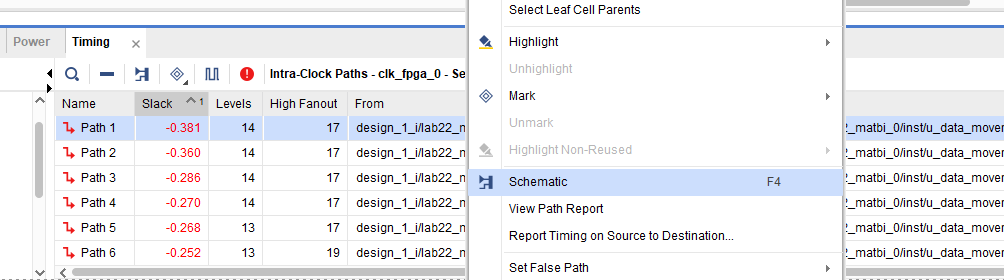

우클릭 Schematic

곱하고 더하는데 이렇게 많이 path를 거치고 있는 것이다.

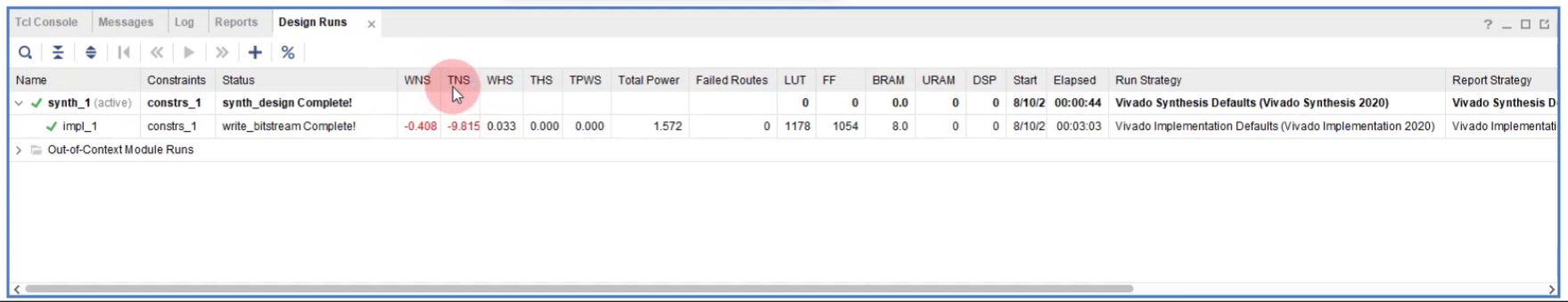

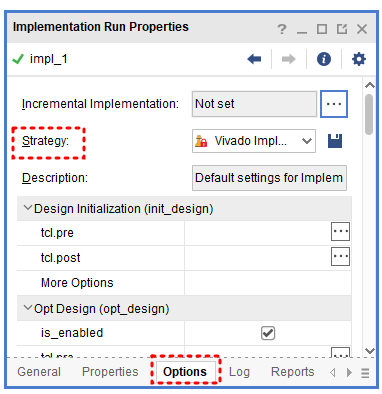

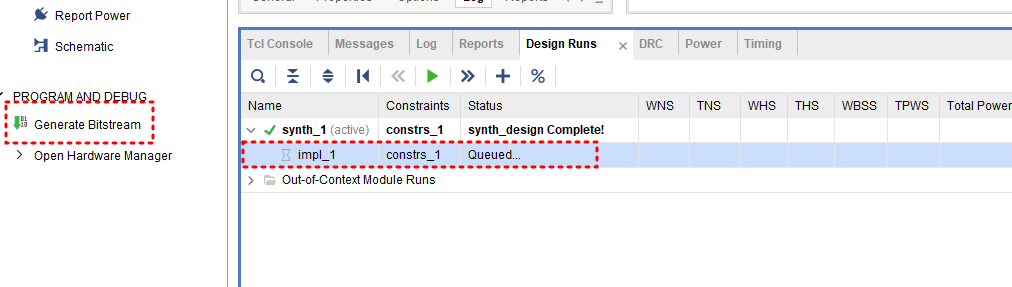

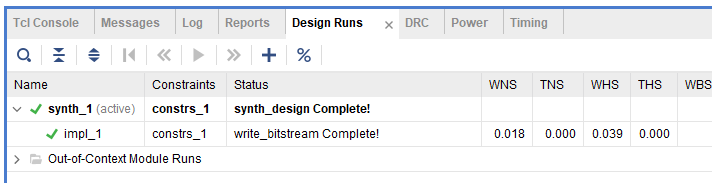

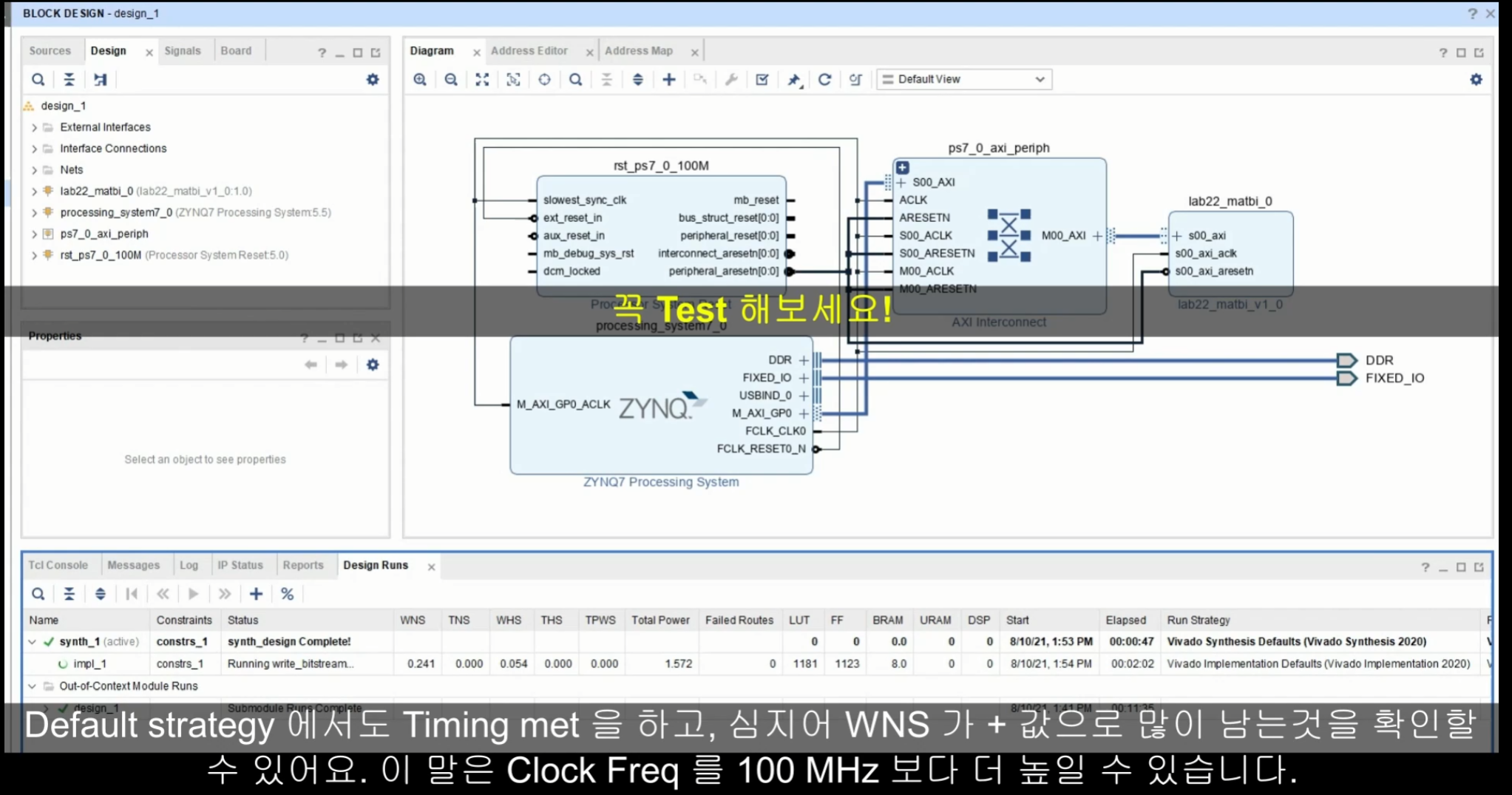

design runs에 가보면

implementation이 있는데

여기서 strategy를 변경할 수 있다.

퍼포먼스가 부족했다

퍼포먼스를 증가시키기위해

Performance_ExploreWithRemap을 사용해보자.

이 주황색 점이 out-of-date라는 의미다.

implementation에 대해 나와있는 UG904문서가 있음.

https://docs.xilinx.com/r/2020.2-English/ug904-vivado-implementation/Revision-History

Revision History - 2020.2 English

The following table shows the revision history for this document. Section Revision Summary 02/26/2021 Version 2020.2 General Updates General release updates. 08/25/2020 Version 2020.1 Using Remote Hosts and Compute Clusters Updated section.

docs.xilinx.com

여기서 strategy는 여기있음.

Directives Used by opt_design and place_design in Implementation Strategies - 2020.2 English

Performance_Explore Explore Explore Performance_ExplorePostRoutePhysOpt Explore Explore Performance_ExploreWithRemap ExploreWithRemap Explore Performance_WLBlockPlacement Default WLDrivenBlockPlacement Performance_WLBlockPlacementFanoutOpt Default WLDriven

docs.xilinx.com

ASIC에서는 congestion이

FPGA에서는 performance와 congestion이 문제가 되는 경우가 많음.

이 strategy만 바꾸어주었음에도 불구하고

timing closure가 이루어졌다.

(원래 기본으로 사용하는 strategy option이 아주아주 효율적인것은 아니라는 이야기이다.)

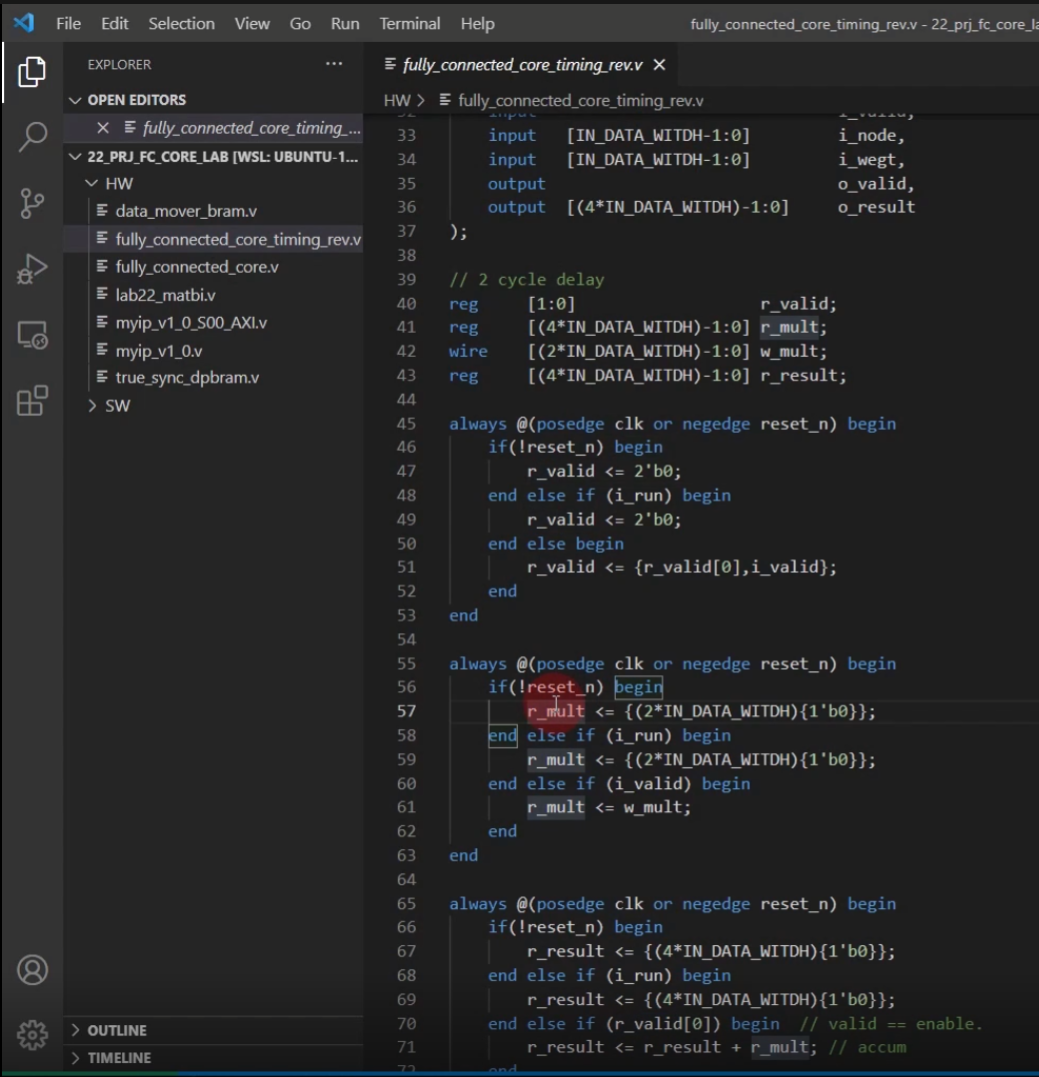

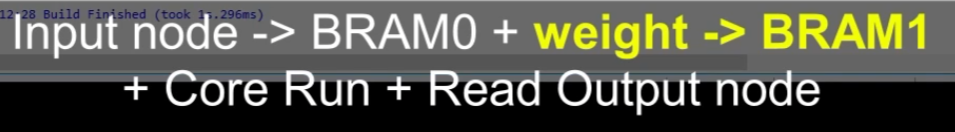

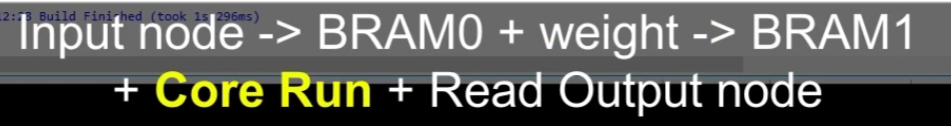

1cycle delay를

2cycle delay로 수정한다.

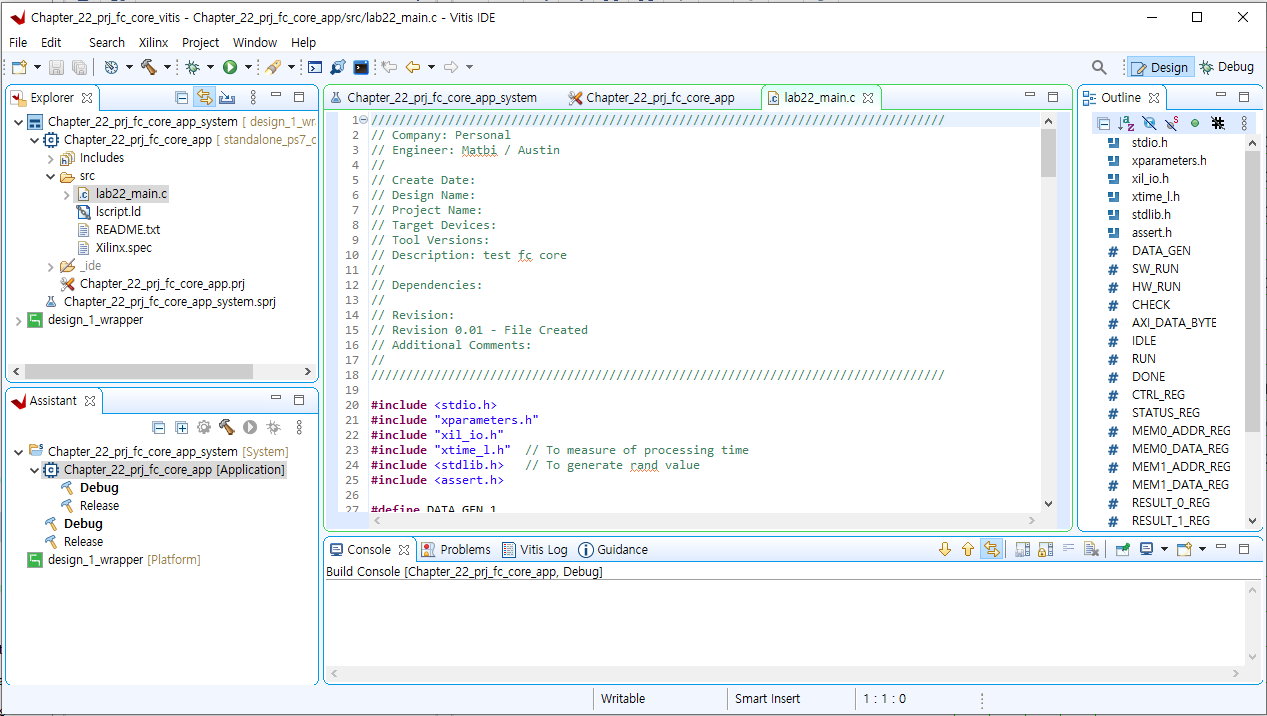

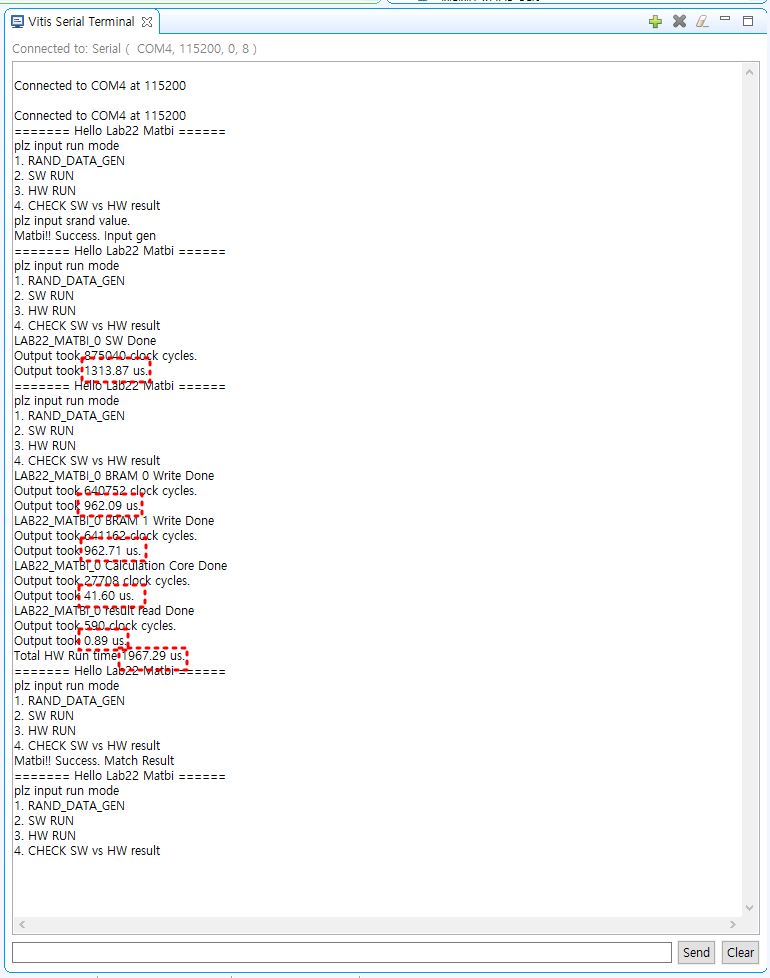

vitis

스택과 힙사이즈를 조절해주어야 함을 잊지 말자.

'적극적 생각 > FPGA' 카테고리의 다른 글

| ★ [FPGA 학습 리소스] vivado-based workshops (0) | 2022.08.02 |

|---|---|

| CPU와 가속기를 응용해서 만들 수 있는 플젝구조 (0) | 2022.08.02 |

| 0802 / Fully Connected Layer 가속기 Core 설계 (2) (0) | 2022.08.02 |

| 생각해보니 HW 올리기전에 TB단에서 검증 더 해줘야 한다. (0) | 2022.08.02 |

| 0802 / Fully Connected Layer 가속기 Core 설계 (1) (0) | 2022.08.02 |