① BRAM 개념

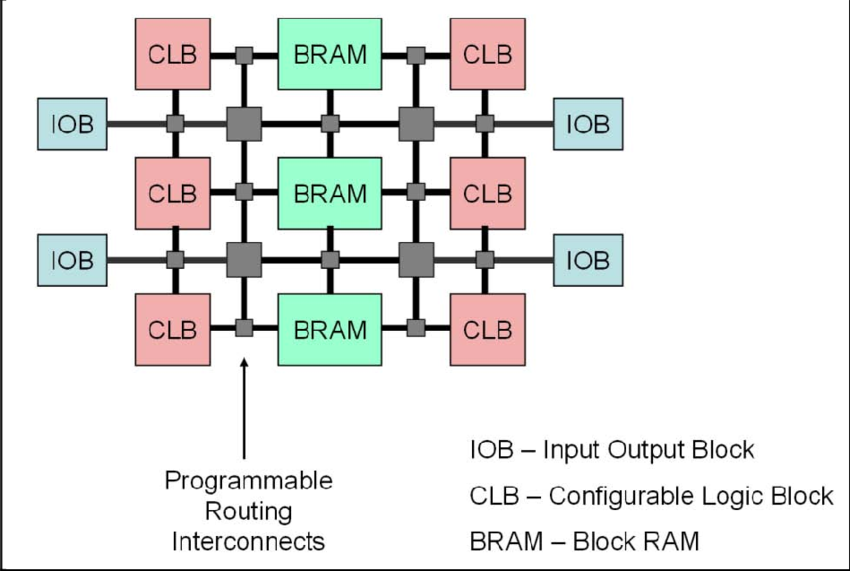

FPGA 보드 내부에는 BRAM 이라는 모듈이 존재한다.

BRAM은 Block Random Access Memory의 약자이다.

FPGA에서 [1]FF, [2]LUTs, [3]DSPs, [4]BRAM은 특히 중요하게 여겨진다.

Embedded memory 또는 EBR=Embedded Block RAM 등으로도 불린다.

기본적으로 하나의 BRAM은 Dual Port이며, 36Kb 이다.

자 그래서 내가 갖고있는 Zybo Z7-20 보드에 얼마만큼의 BRAM Resource가 있는지 Detail을 보자.

이 문서는 Zynq-7000 DataSheet이다. PL 영역을 구성하는 요소들에 대한 설명과, BRAM이 등장한다.

36Kb True Dual-Port 이고, 18Kb 2개로 쪼개서 사용할 수도 있고, 72Kb wide로 사용할 수도 있단다.

https://www.mouser.com/datasheet/2/903/ds190-Zynq-7000-Overview-1595492.pdf

이는 Zynq-7000 패밀리에서 36Kb True Dual-Ports BRAM을 사용했음을 의미하며

630Kb/36Kb = 17.5개의 리소스가 있음을 알 수 있다.

(왜 18개가 아니라 17.5개지????) : https://www.inflearn.com/questions/600889

Zybo Z7-20 & BRAM Resource - 인프런 | 질문 & 답변

BRAM에 대해 공부중이었는데 질문이 있어 드립니다. (BRAM 강의에서 다뤄진 내용이지만, 능동 공부 범위라서 이건 강의 내용은 아닌데, 이런 내용을 질문드려도 될까요?) Zybo Z7-20에는 몇개의 BR

www.inflearn.com

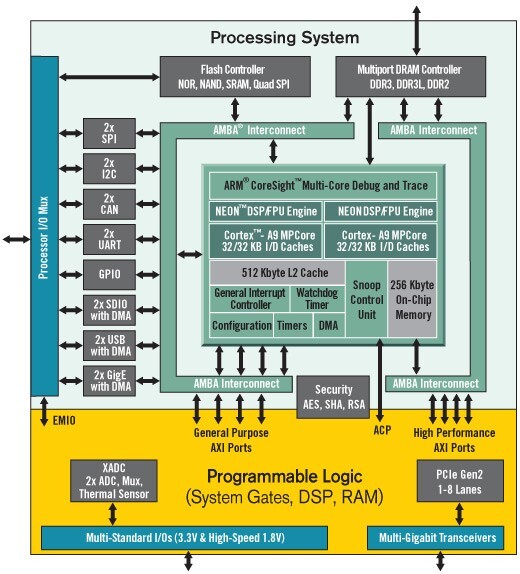

Zybo Z7-20의 PS영역과 PL영역은 다음과 같이 나뉘고,

지금 저 BRAM은 PL영역에 있음을 다시한번 상기하자.

우리는 다음과 같이 PS와 PL을 구성해 설계를 할것이다.

② AXI4-LITE 개념

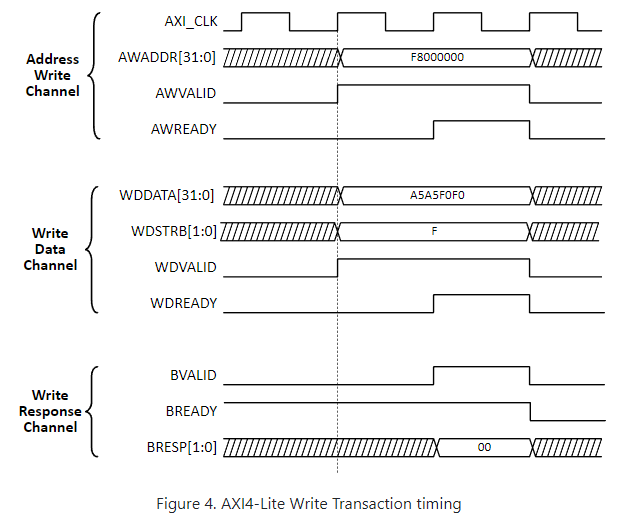

AXI4는 R/W에 최적화되어있는 (다중채널)버스이다.

AXI4-Lite는 Burst 기능이 없는 라이트버전이다.

머리에 박아두어야 할 [1] Channels [2] Write [3] Read 는 다음과 같다.

[1] Channels

- Write Address

- Write Data

- Write Reponse

- Read Address

- Read Data

[2] Write

- Write Address = Addr Cmd

- Write Data = Data Beat

- Write Reponse = Write Response

1. The master drives the Write Address (0xF8000000) and Write Data (0xA5A5F0F0) on the write channels, and drives AWVALID and WDVALID strobes to tell the slave the address and data are valid (Note: the master also drives 0b1111 on the WDSTRB signal to indicate all four bytes are valid);

2. The slave asserts AWREADY and WDREADY signals to indicate it can sample the data;

3. When the AWVALID/WREADY and WDVALID/WDREADY strobes are asserted at the same time, the handshake is complete, and all strobes are deasserted;

4. The slave drives “00” on BRESP and asserts the BVALID strobe to indicate the transfer was successful, and the next rising edge completes the transaction.

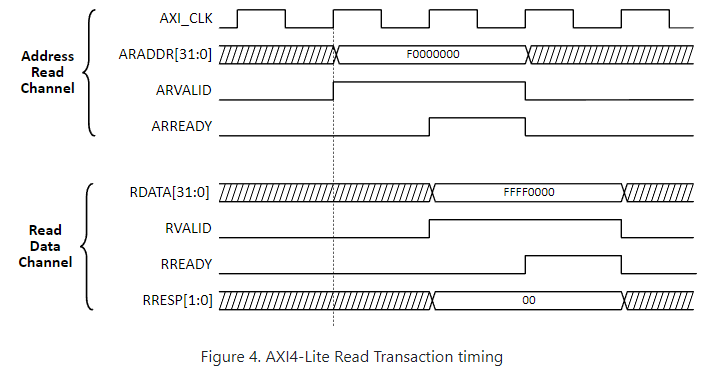

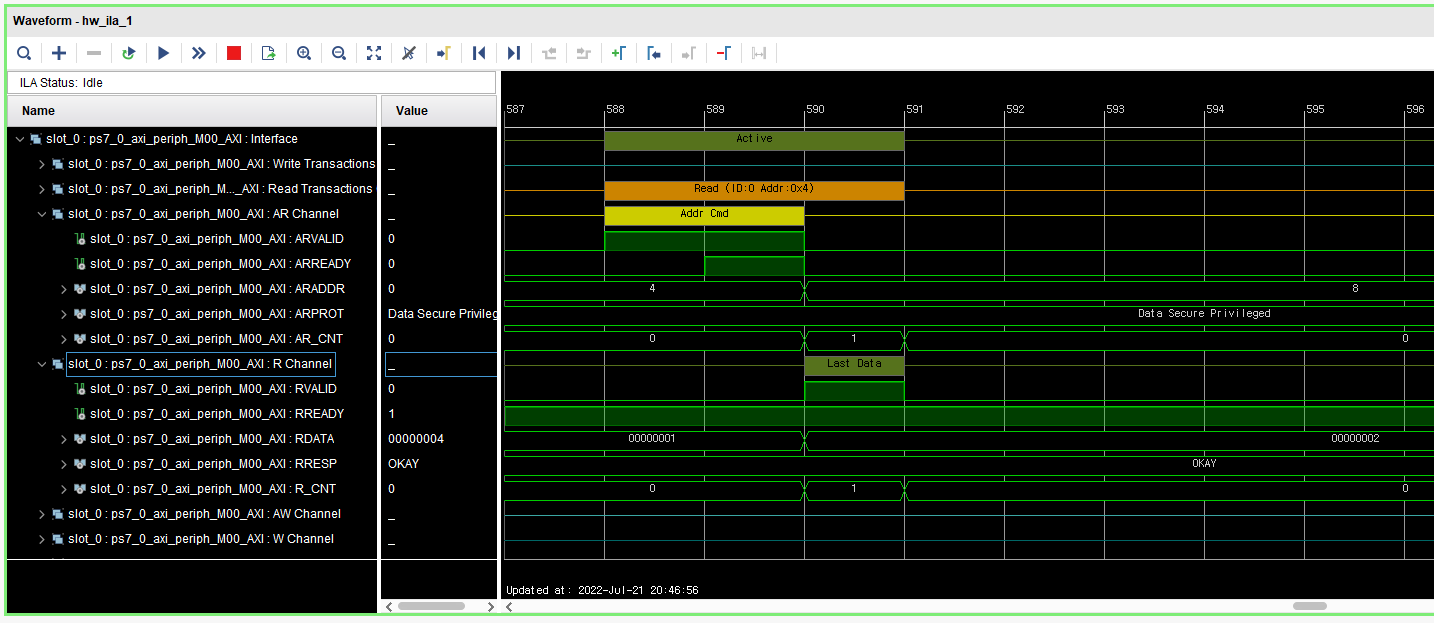

[3] Read

- Read Address = Addr Cmd

- Read Data = Last Data

1. The master drives the Read Address (0xF0000000) channel and asserts ARVALID to tell the slave the address is valid;

2. The slave asserts ARREADY to indicate it can sample the address. When ARVALID and ARREADY are both asserted, the slave has the address, the handshake is complete, and the master and slave deassert ARVALID and ARREADY, respectively;

3. The slave drives the Read Data (0xFFFF0000) channel and asserts RVALID to tell the master the data is ready, and the master drives RREADY to indicate it is ready to sample the data;

4. When RREADY and RVALID are both asserted, the transaction is complete and the strobes are deasserted;

5. The slave drives “00” on the RRESP signals in the Read Data channel to indicate data was received successfully (or other codes as indicated).

③ AXI 추가개념

다음 개념들에 대해 추가적으로 더 짚고 넘어가자.

[1] Strobe

[2] Burst

[3] AHB

[4] Outstanding

[1] Strobe

Strobe 신호는 Parallel 통신에서 Data의 유효성을 상대편 디바이스에 알려주는 역할을 한다.

ex. 내가 Write를 하기 위해 유효한 Data&Addr를 보낼거야. 내가 Read를 위해 유효한 Addr를 보낼거야.

[2] Burst

다량의 데이터를 W/R 하기 위하여, Addr를 Sequential하게 증가/감소 시키는 행위.

초기 Addr 한번 주고나서 쭉~ W/R한다.

[3] AHB = Advanced High performance Bus

AMBA 프로토콜에는 AHB, APB, AXI 등이 있다. (장치별 전송속도 및 특성을 고려해 선택한다.)

AXI는 SoC의 발전에 따라, AHB를 대체하기 위하여 개선되어 나온 프로토콜이다. (2003)

AHB는 과거 ASB에 비하여, Addr,Control,Data라인이 모두 분리되어있는 것을 모두 공유하게끔 했다.

하지만 그럼에도 불구하고, Latency가 발생하거나 하는 특정한 상태에서, 비효율적인 버스점유 상황이 발생한다.

그렇기 때문에, AXI는 그러한 버스점유 상황을 막기 위하여 Channel이라는 개념을 도입하여 문제를 해결했다.

[4] Outstanding

위에서 AHB에 대한 간단한 개념을 이해하되, AHB와 AXI의 비교에 초점을 맞추어서 이해를 했다.

이때 AXI가 갖는 또다른 장점으로 MOR(Multiple Outstanding Request)이 지원된다라는 점이 있는데,

Outstanding은 상태이며, 내가 보낸 요청에 대한 확인 응답을 받지 못한 상태를 의미한다.

즉 Single Outstanding Request만 지원되는 상황이라면, 계속 그 Request에 대해 붙잡고 있어야 하는데,

한번에 여러개의 Request를 미리 보내두고, Slave는 상황에 맞게 스스로 선택적으로 처리하고,

처리가 완료된 확인 응답을 받음에 따라, Outstanding 상태를 하나씩 해제하면 된다.

AXI는 이게 되고, AHB는 이게 안된다. (그 이외의 장점들이 많이 있지만 당장 AHB를 다룰 필요 없어 패스)

④

⑤

⑥

⑦

⑧

⑨

⑩

---

참고자료

BRAM

https://www.fpgakey.com/tutorial/section44

FPGA Architecture - Designing with Xilinx FPGAs Using Vivado - FPGAkey

FPGA Architecture Overview The primary function of the FPGA is to implement programmable logic which can be used by end customers to create new hardware devices. FPGAs are built around an array of programmable logic blocks embedded in a sea of programmable

www.fpgakey.com

https://www.reddit.com/r/FPGA/comments/eri97t/beginner_explanation_of_fpga_memory_uses/

Beginner explanation of FPGA memory uses

I don't really understand how memory allocation in FPGAs works. Based on documentation, I believe there are 2 types of RAM in most FPGAs, Block...

www.reddit.com

https://digilent.com/reference/programmable-logic/zybo-z7/reference-manual

Zybo Z7 Reference Manual - Digilent Reference

digilent.com

https://www.researchgate.net/figure/Xilinx-FPGA-device-details_tbl1_265980194

AXI, AXI Lite

AXI버스란?

AXI(Advanced eXtensible Interface) : 다중 채널 버스로, 읽기/쓰기에 최적화 되어 있는 버스이다. AXI 버스와 AHB버스의 가장 다른 점은 채널의 도입이다. Read Address Channel Write Address Channel Read D..

wh00300.tistory.com

https://www.realdigital.org/doc/6cb4e88c145c960ad199be9fac5e9402

Welcome to Real Digital

The AXI4 Bus Overview of AXI4 bus operations The “advanced extensible interface” (AXI) bus is a high-performance, point-to-point, master-slave parallel bus used to connect on-chip peripheral circuits (or IP blocks) to processor cores. The AXI standard

www.realdigital.org

https://m.blog.naver.com/guile21c/50940353

SDRAM 의 모든것 7. 타이밍 분석(BURST 동작)

버스트 읽기 / 쓰기 동작의 설명에 앞서서 'BURST' 라는 말의 뜻을 먼저 새겨 보겠습니다. 어드레스를...

blog.naver.com

AHB

http://egloos.zum.com/donghyun53/v/4077209

AHB 프로토콜에 대한 간단한 tip - HTRANS 신호의 BUSY 상태가 필요한 이유

제 전공분야가 Network-on-Chip 임에도 불구하고 이 분야에 대해서 글을 쓰는건 블로그를 만들고 거의 6개월이 다 되어서네요. 우선 몸 풀기로 이 분야에 입문해서 AMBA 프로토콜 중의 AHB에 대해 공부

egloos.zum.com

http://egloos.zum.com/donghyun53/v/4087409

AHB 대비 AXI 프로토콜의 장점 몇 가지

지난 번 AHB 프로토콜에 대해서 간단히 글을 썼었는데, 이번엔 좀 더 글의 범위를 넓혀서 AHB 프로토콜과 비교하여 AXI 프로토콜이 가진 장점에 대해서 한 번 정리해 보려고 합니다. AXI 프로토콜은

egloos.zum.com

https://gc-na.github.io/ARM_AMBA_protocol/

AMBA protocol란? 암바 프로토콜 핵심 정리 AHB, ACE, APB, AXI, CHI 什么是 AMBA 协议? Amba 协议密钥汇总 AHB

What is AMBA protocol?

gc-na.github.io

ARM의 AMBA 종류

BUS란 CPU에서 메모리나 입출력 기기에 데이터를 송출하ㅓ나 반대로 메모리나 입출력 기기에서 CPU에 데이터를 읽어들일 때 필요한 전송로이다. CPU와 메모리 또는 입출력 기기 간에 어떤 곳으로도

wh00300.tistory.com

http://babyworm.net/archives/1274

AMBA 3.0 AXI protocol에 대한 잦은 질문

2주 전부터 몸 상태가 메롱메롱한데, 지난주에 그 상태로 IT-SoC 강좌를 하고 왔더니 평상시 보다 더 못한 강의를 하고 와서 멀리 누리꿈 스퀘어까지 찾아주신 분들께 죄송한 마음이 많습니다. 제

babyworm.net

What does it mean by "outstanding" transactions in AXI protocol or memory protocol?

Answer (1 of 3): Lets understand this with small example in real time. Assume that you have transferred money 500/- to you friend. Your friend will get 500/— amount and you will be acknowledged by bank through message right.?Sometimes we will receive mes

www.quora.com

'적극적 생각 > FPGA' 카테고리의 다른 글

| CPU 설계에 도움이 되는 URL 모음 (0) | 2022.07.21 |

|---|---|

| Zynq-7000 SoC Data Sheet: Overview (0) | 2022.07.21 |

| AXI BRAM Controller (0) | 2022.07.21 |

| (중요) 0721 - 섹션4 - AXI4Lite 이용해 BRAM에 RW (0) | 2022.07.21 |

| 모식도 작성툴, gliffy, drawio (0) | 2022.07.17 |