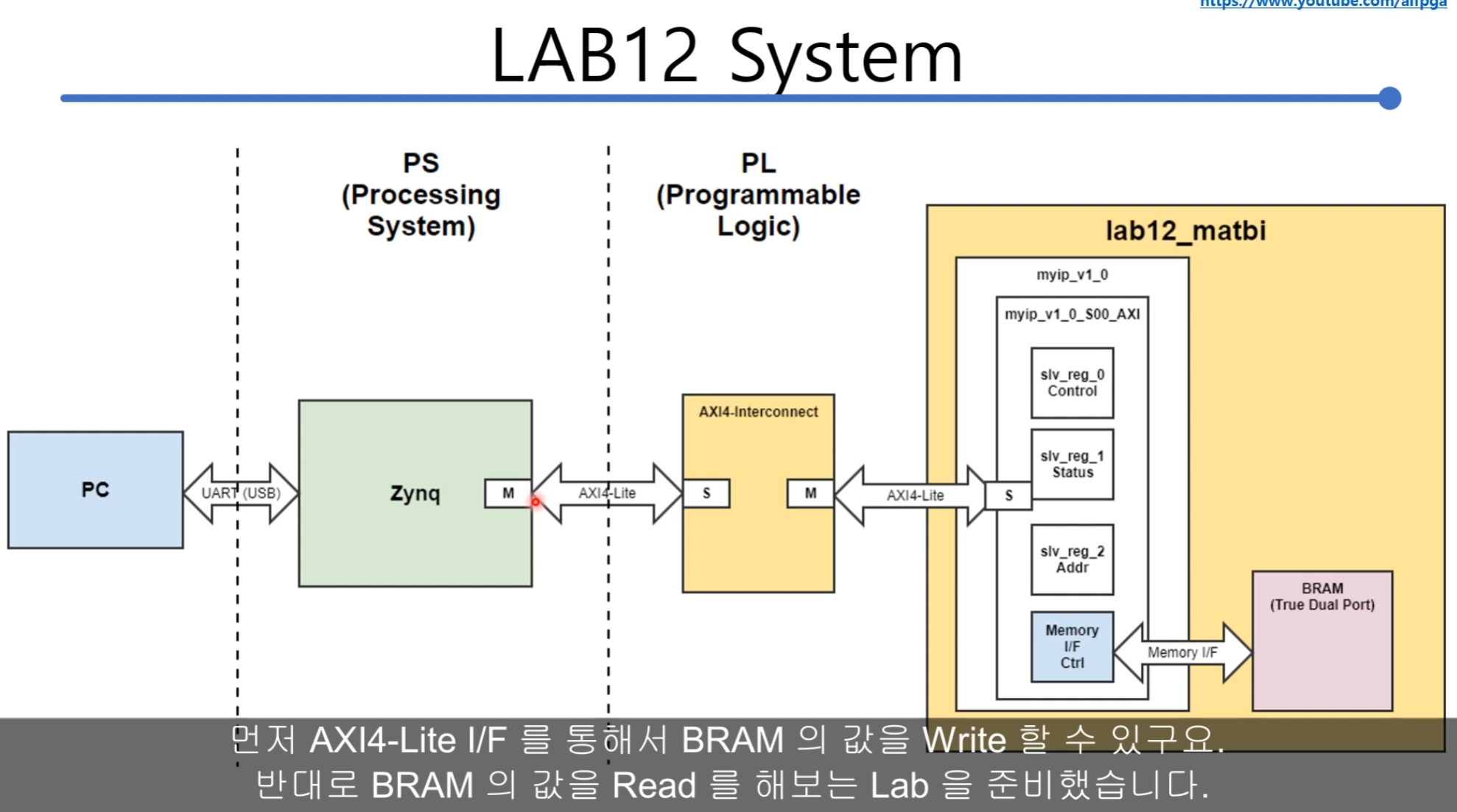

이론

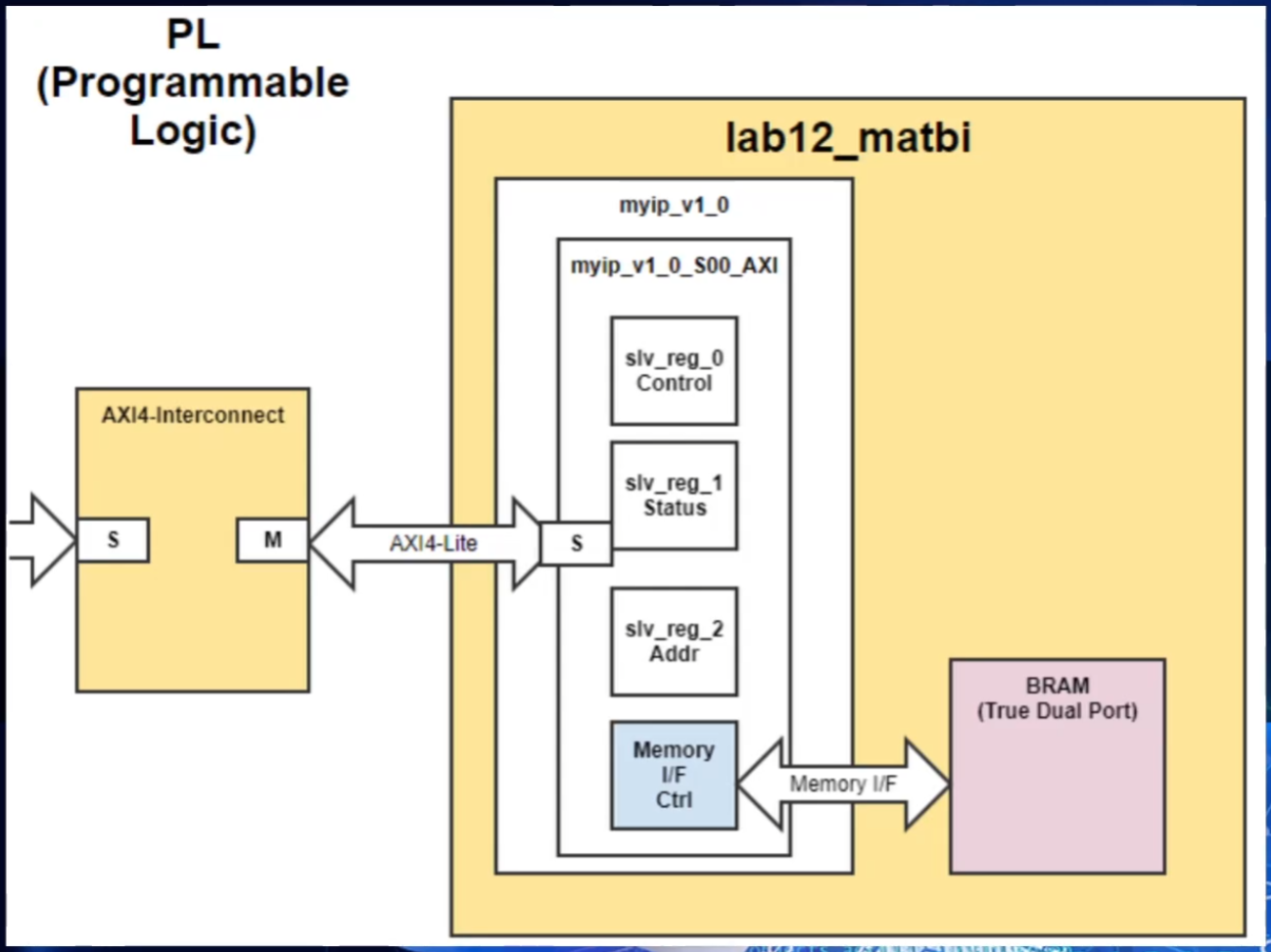

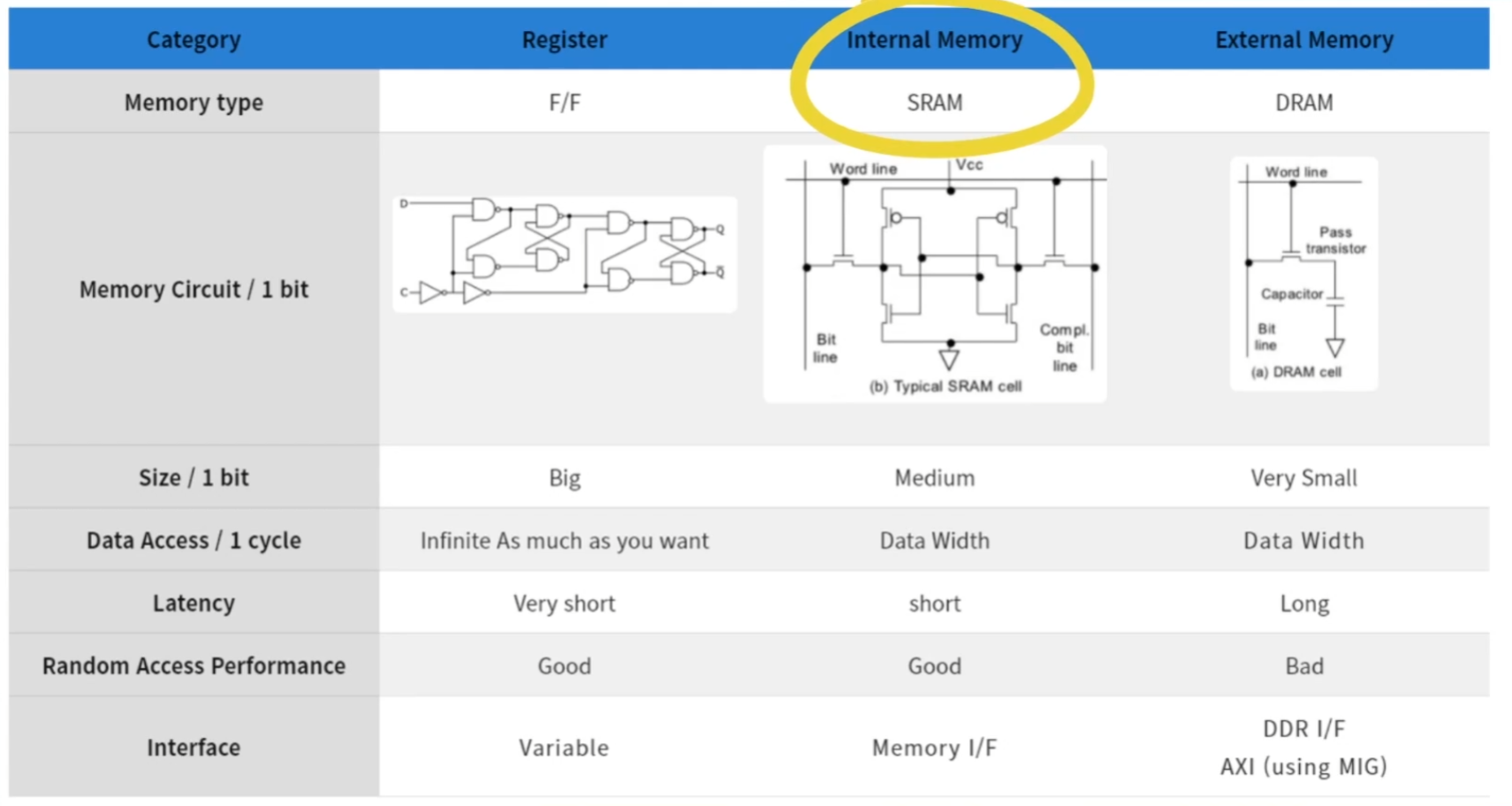

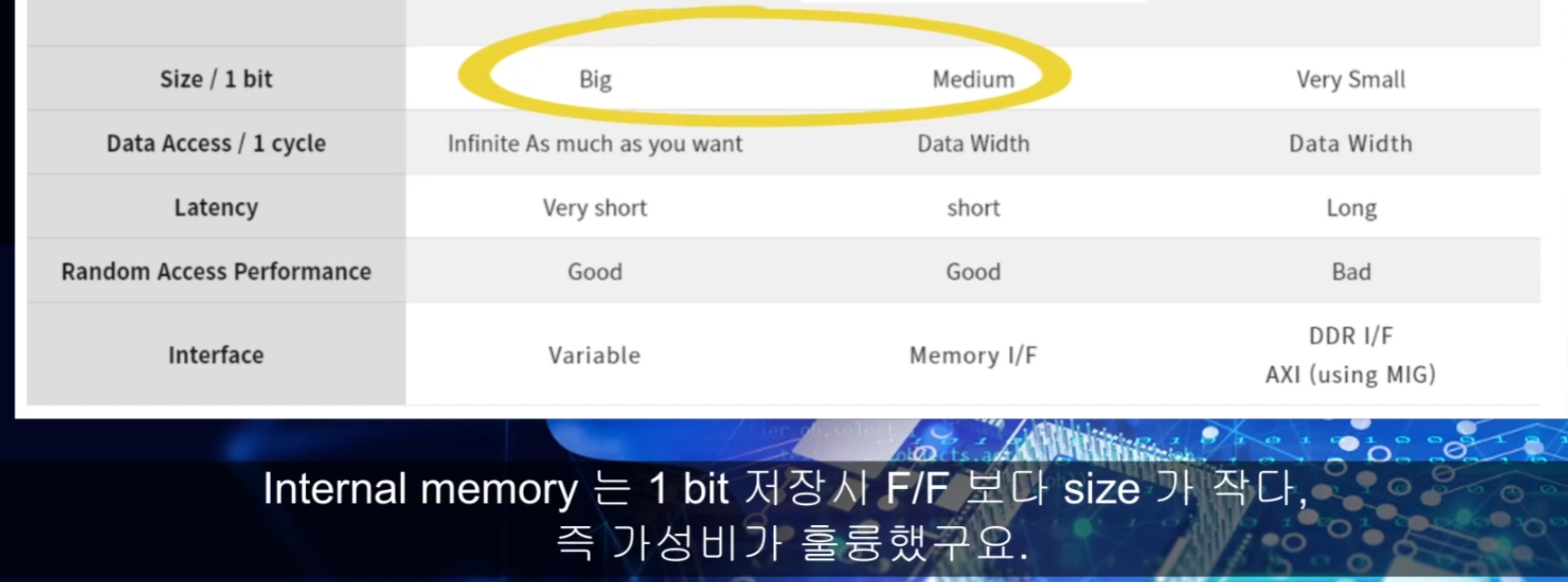

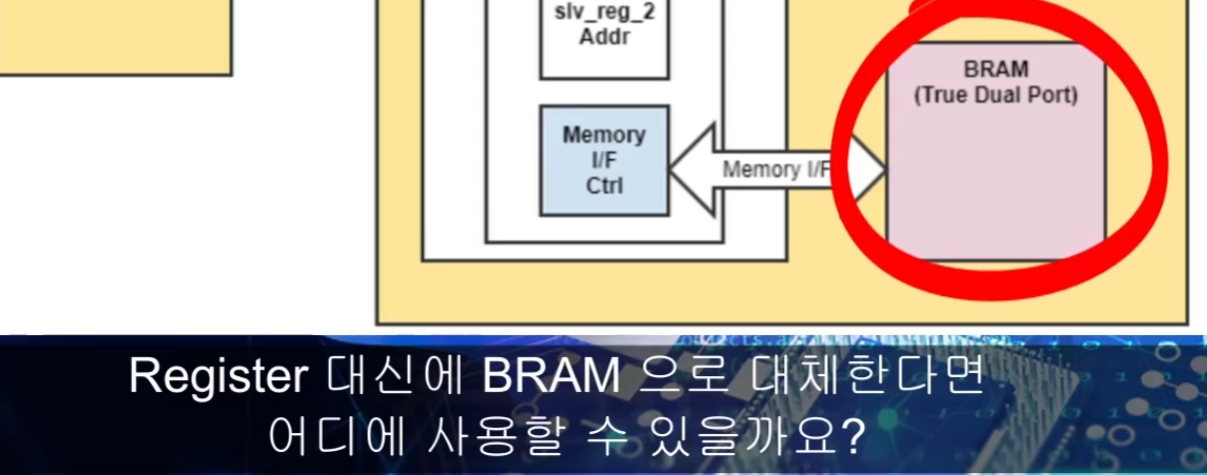

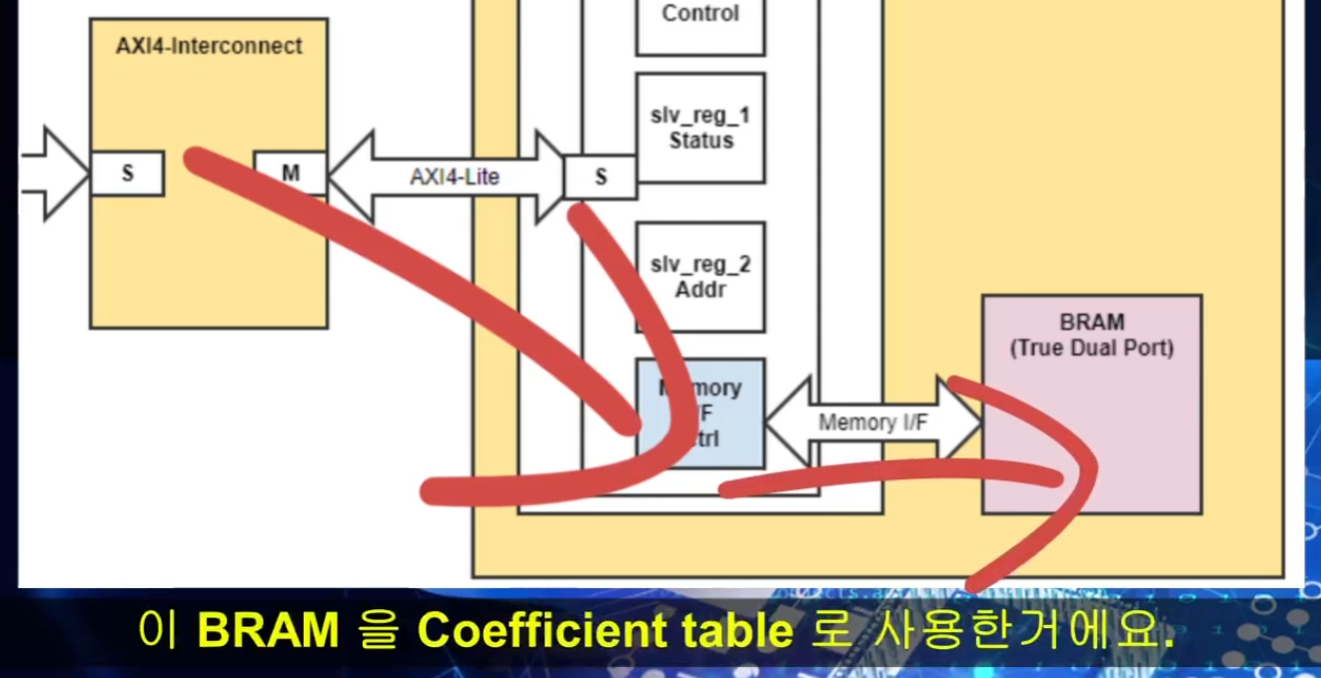

BRAM

지금까지는 Register에

---

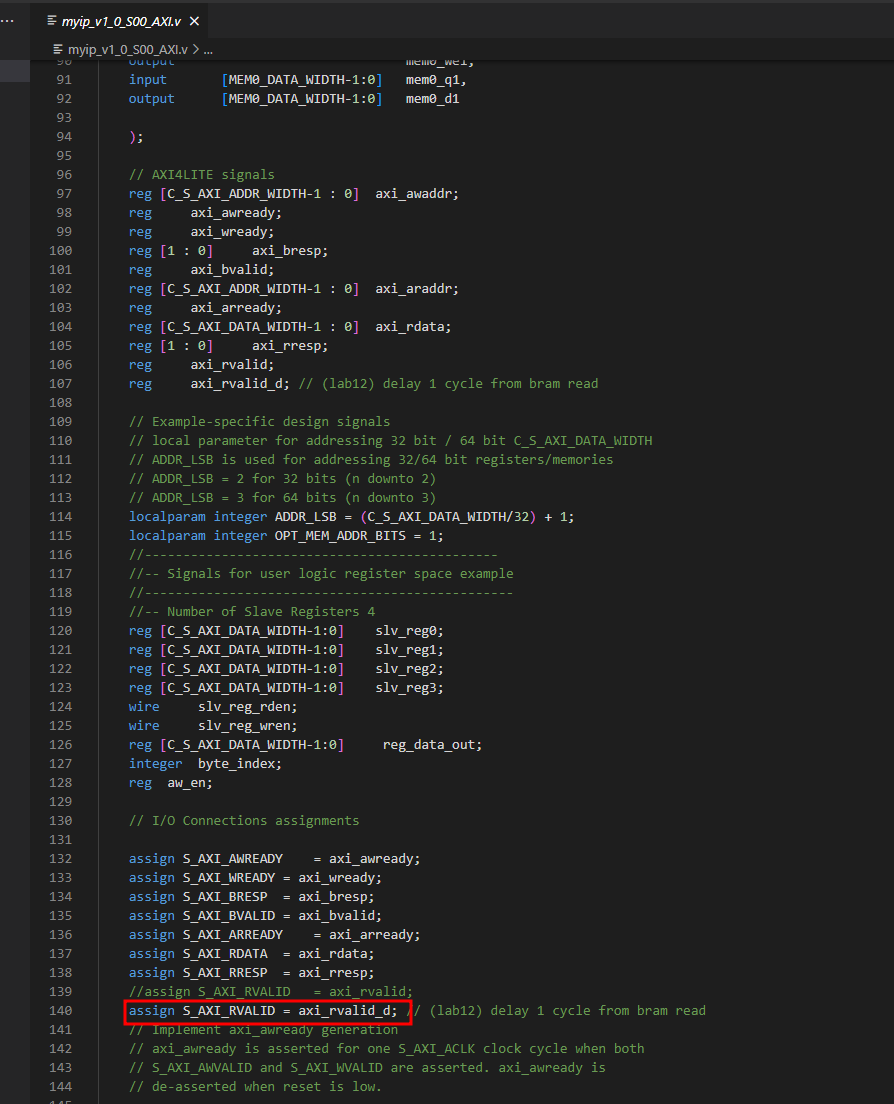

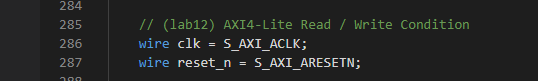

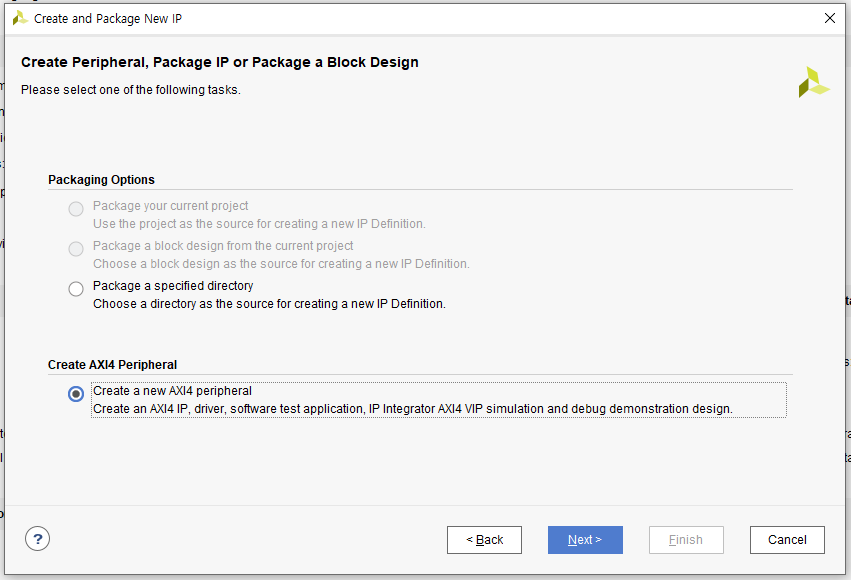

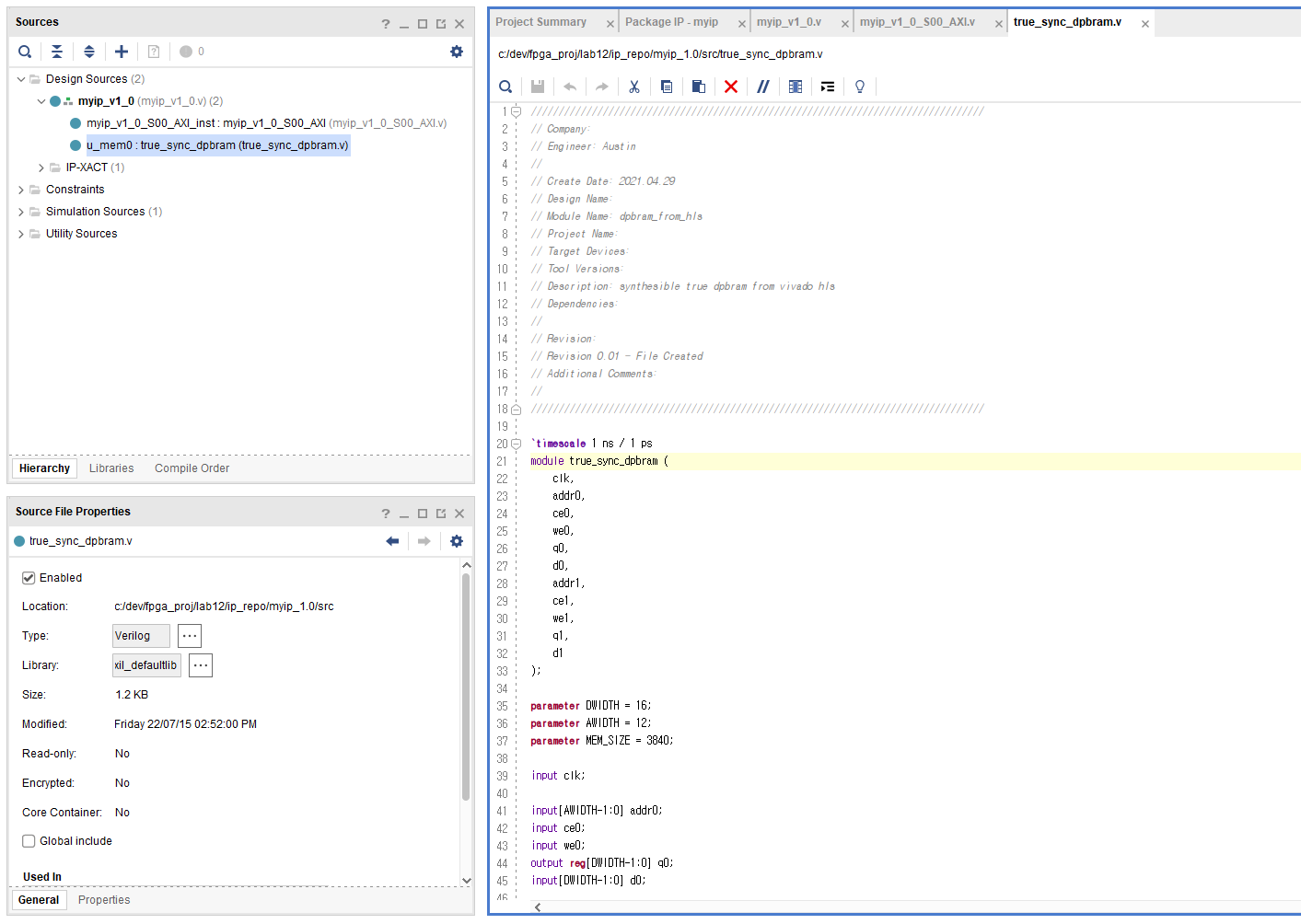

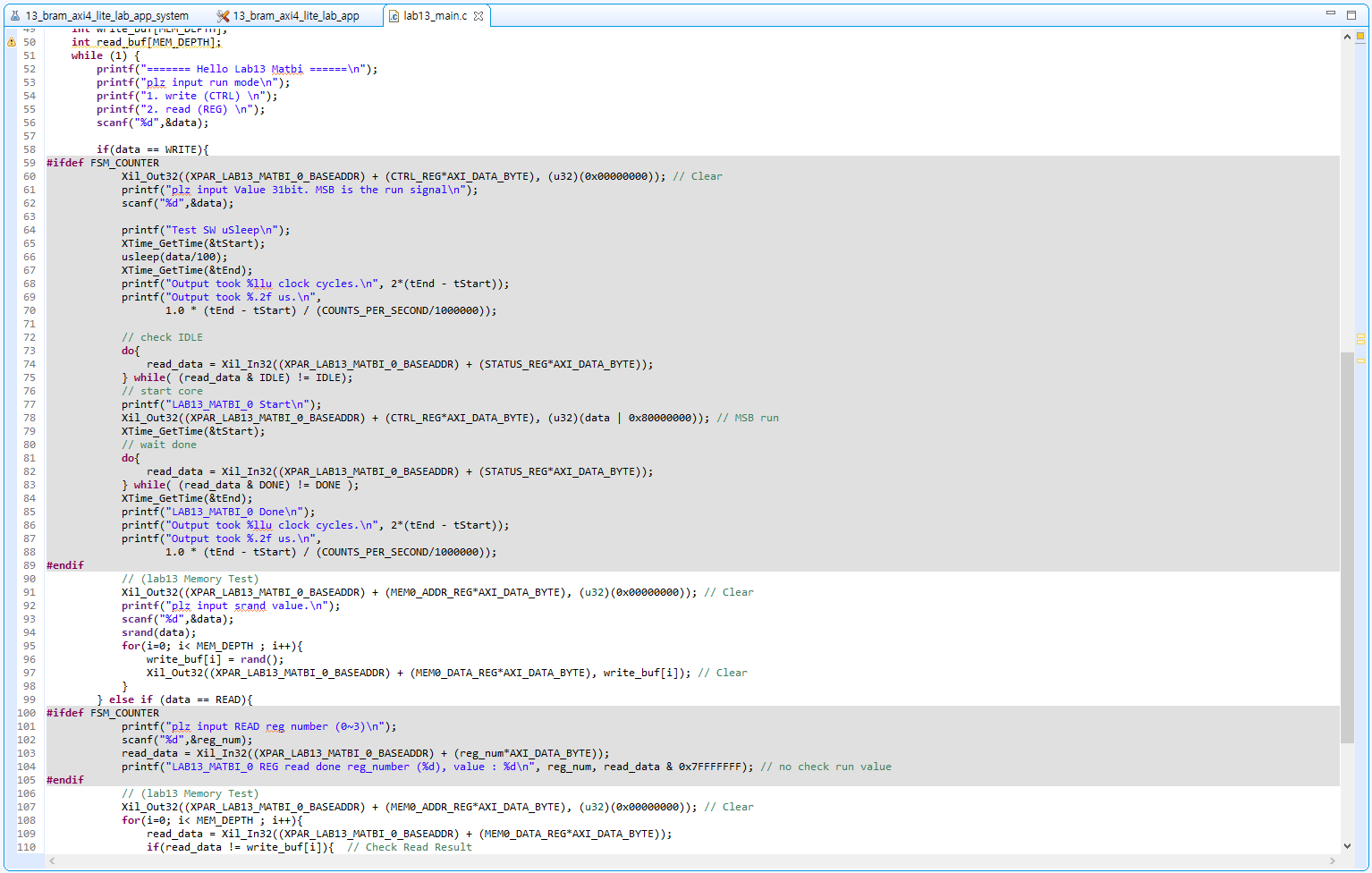

코드리뷰

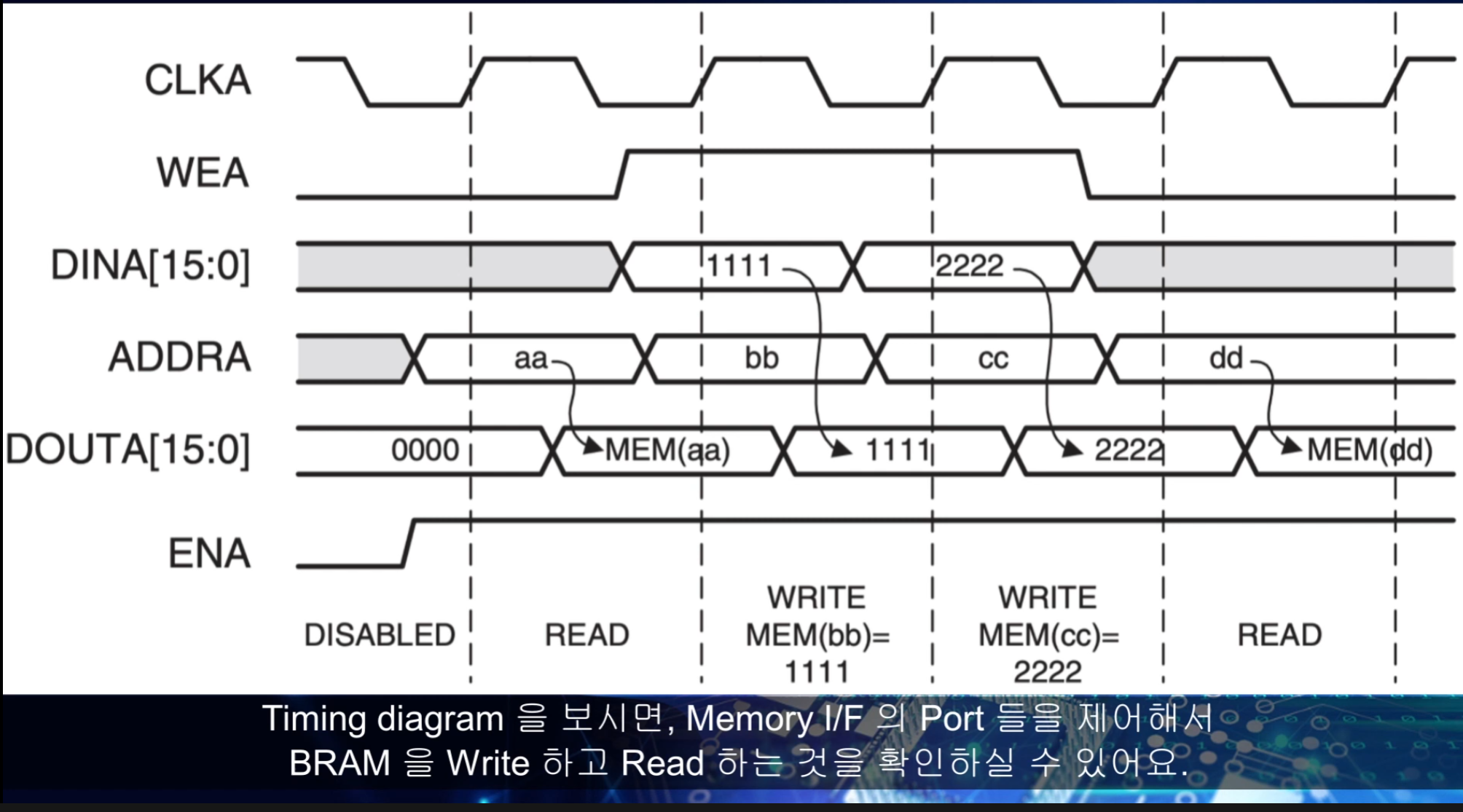

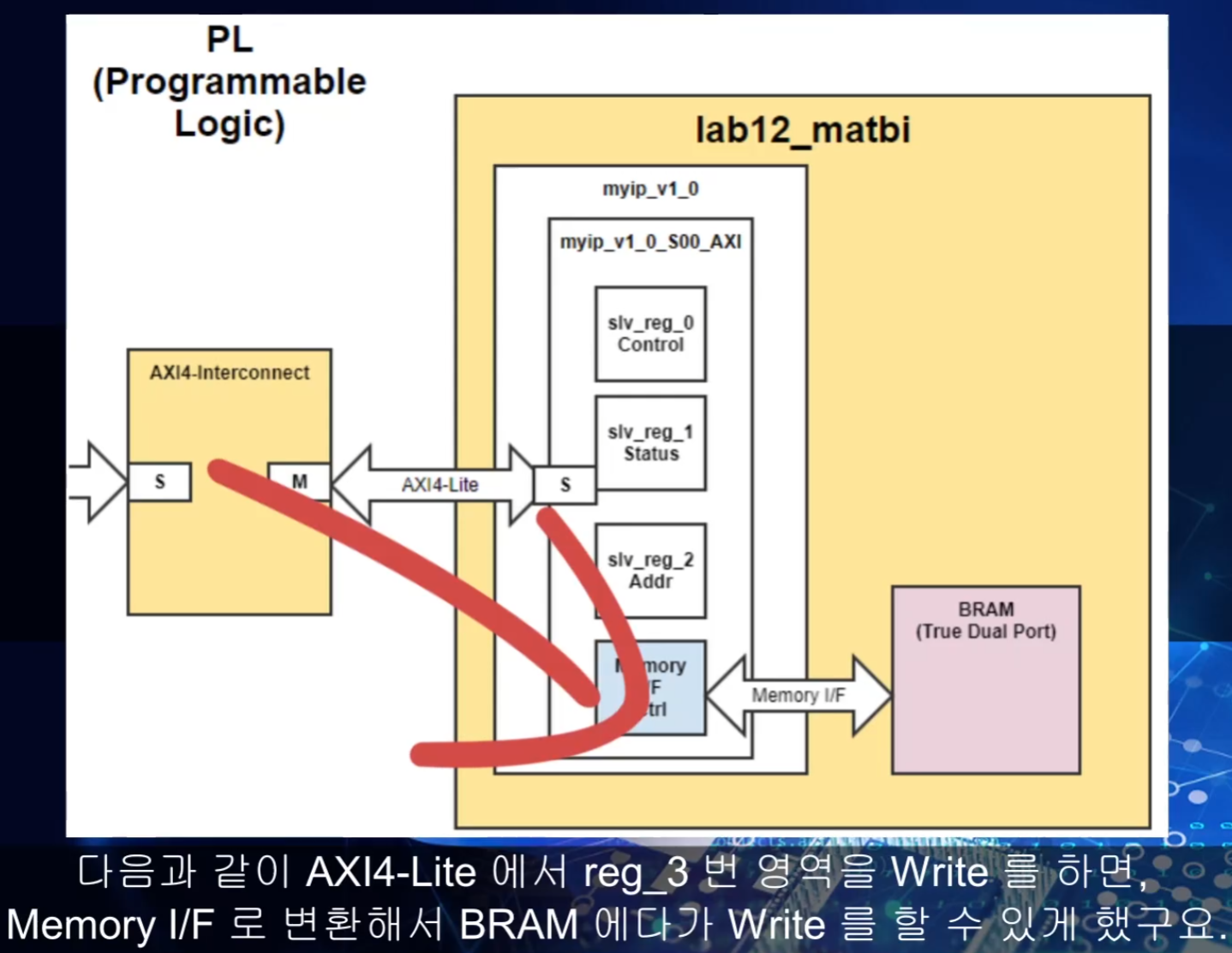

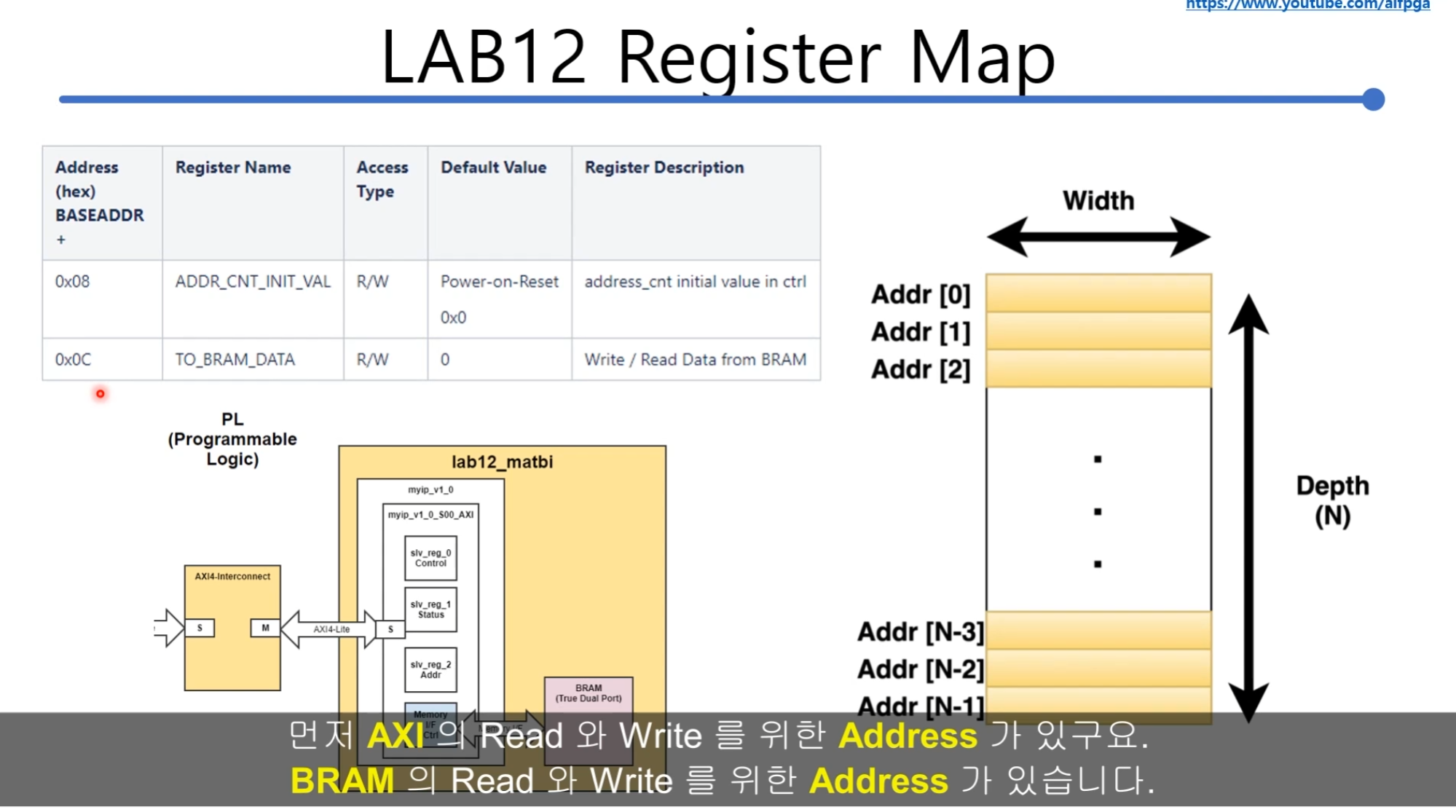

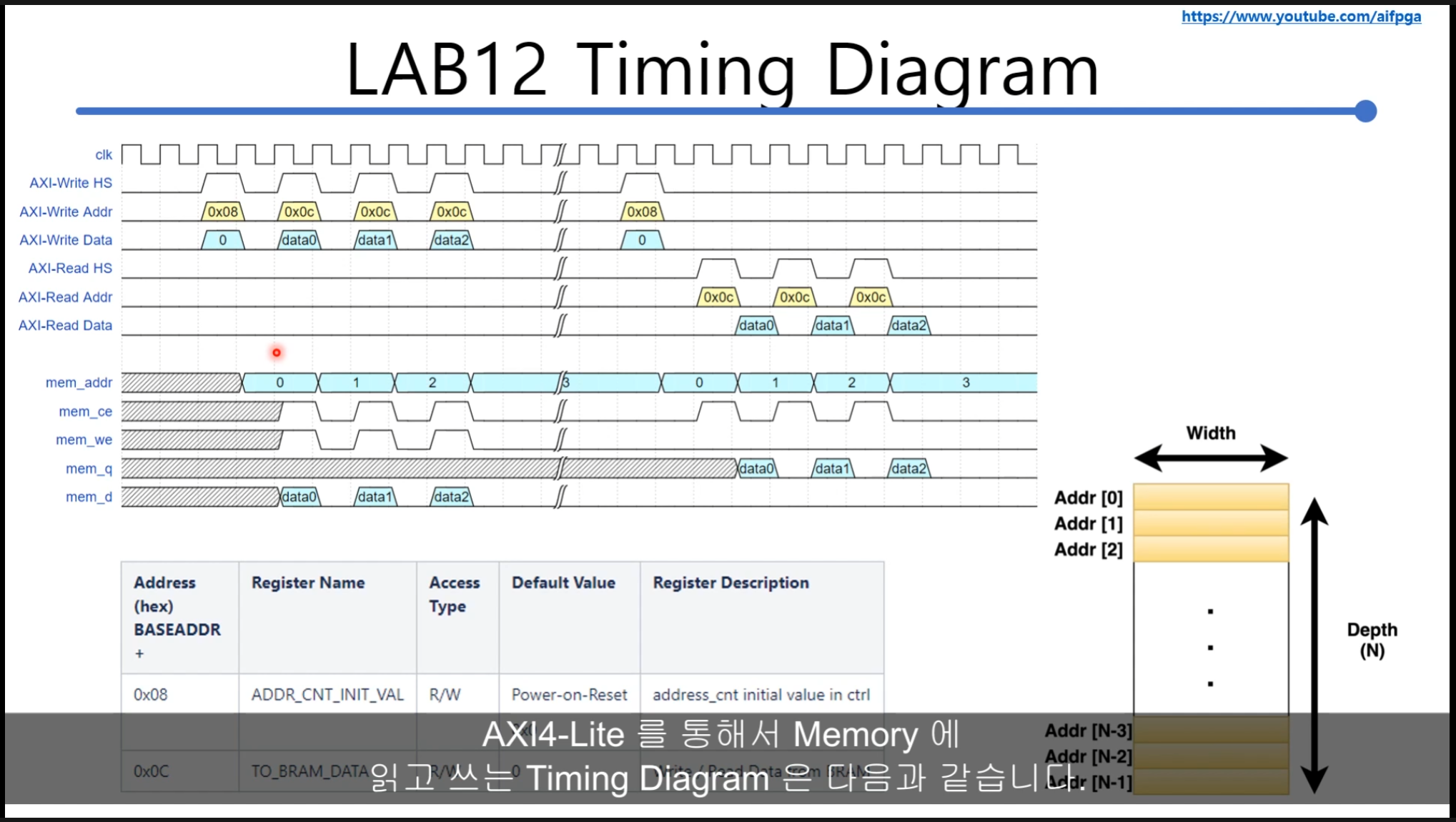

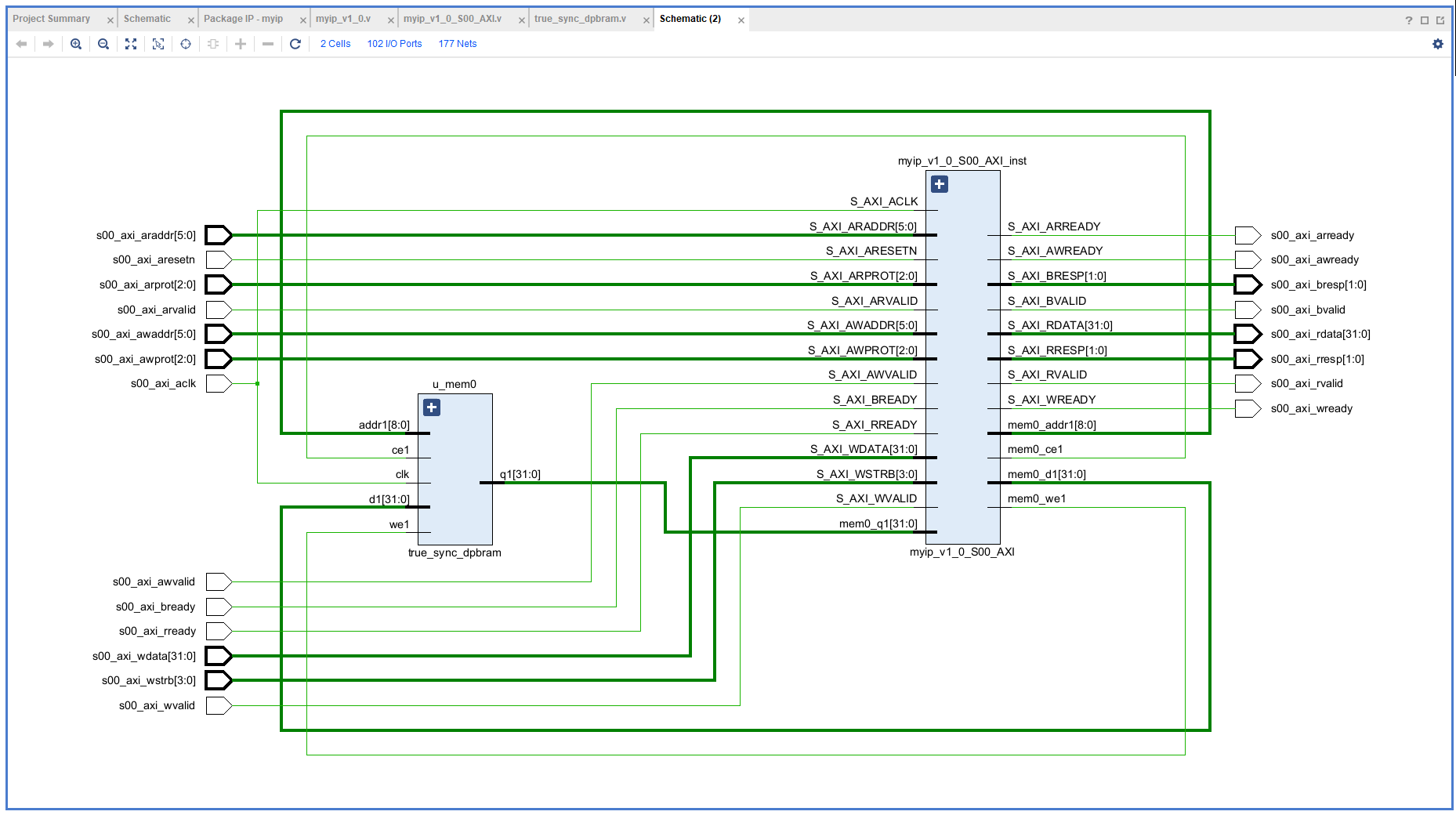

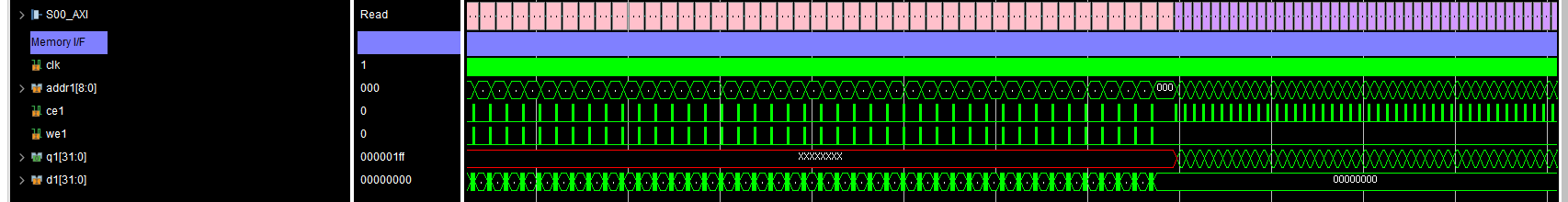

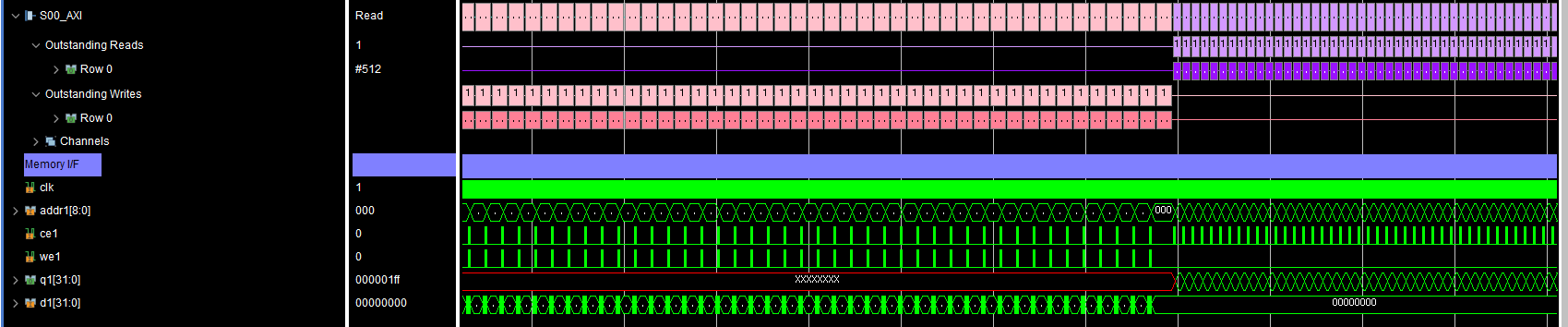

Write

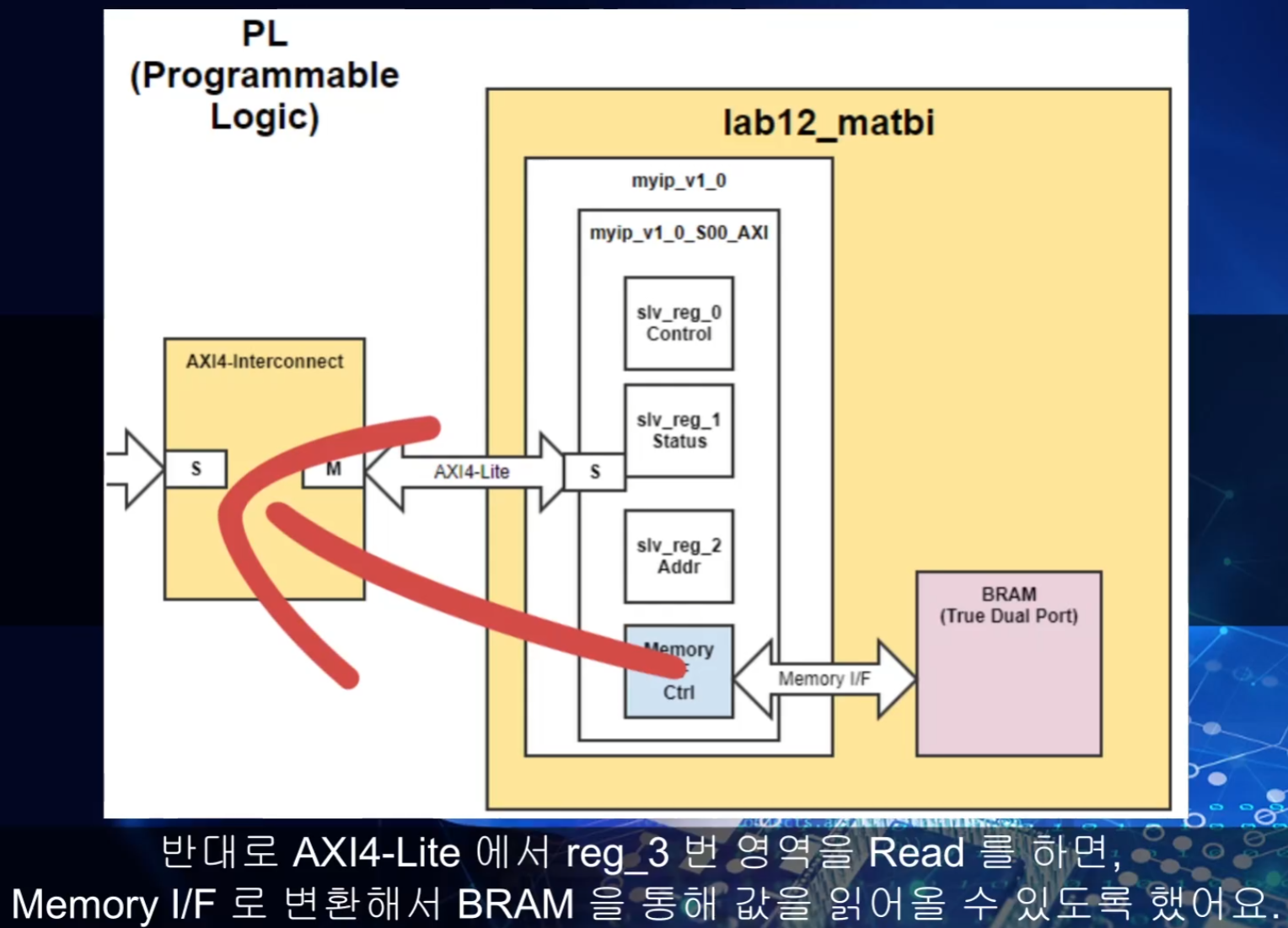

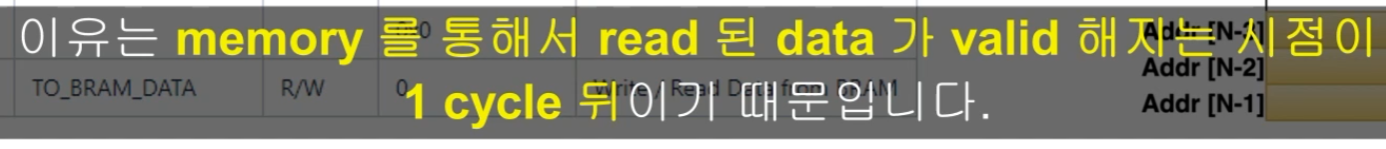

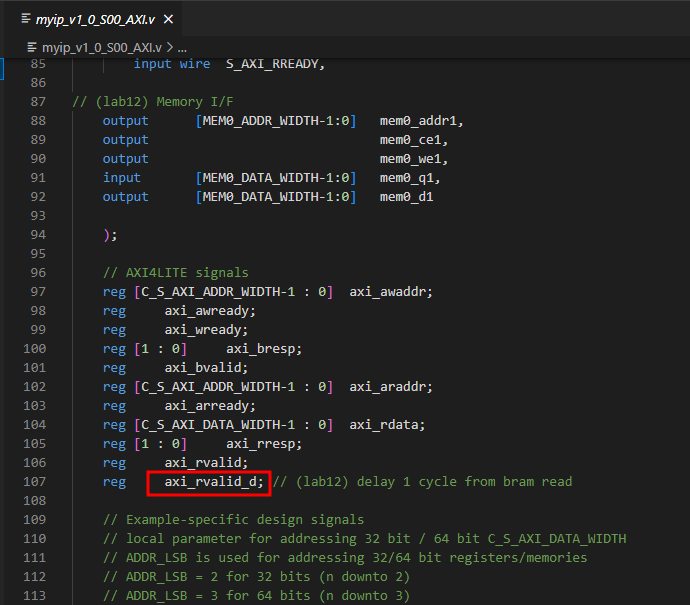

Read

Addr

---

실습

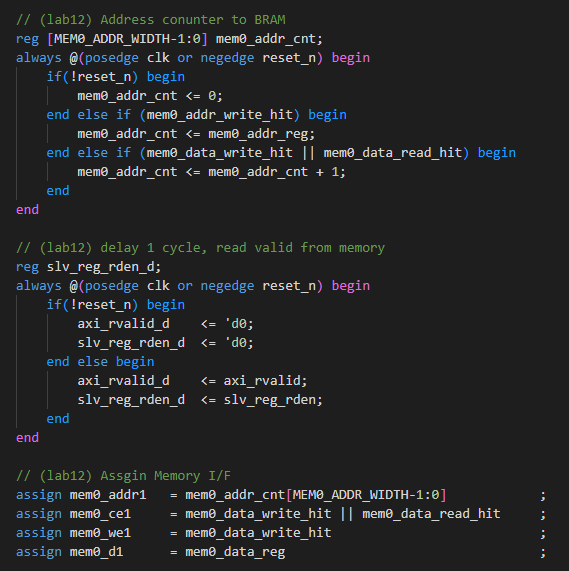

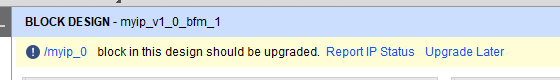

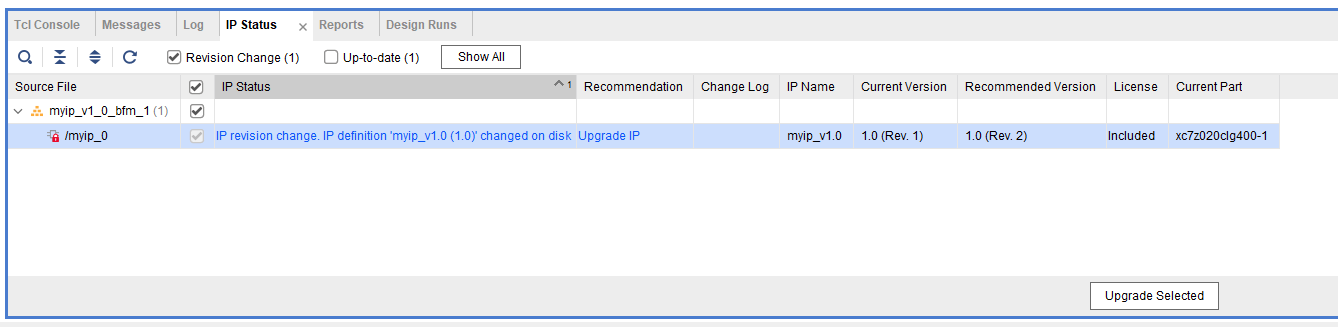

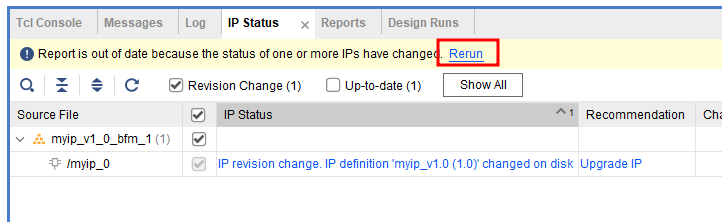

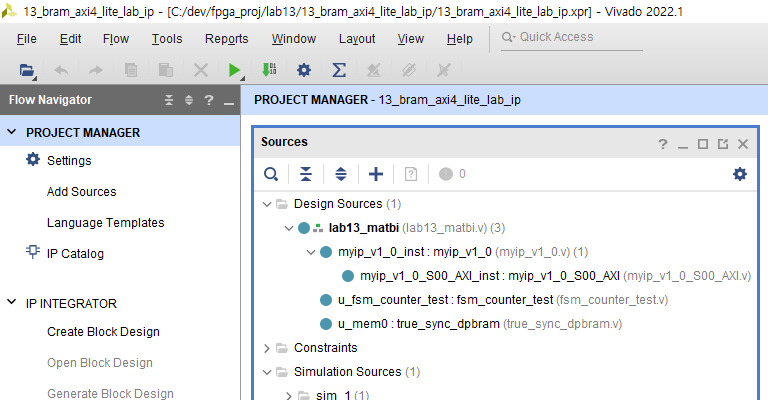

MYIP를 Replace할건데

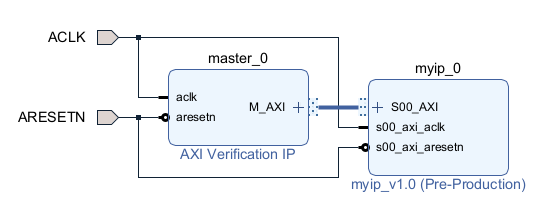

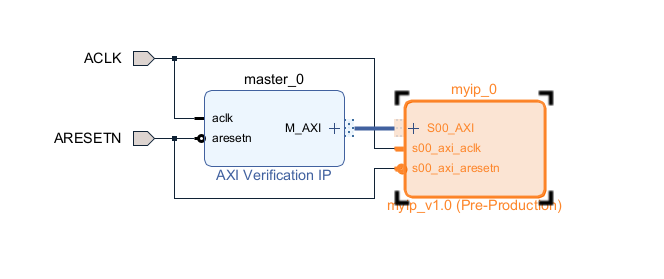

코드 수정시에도 VIP 모듈이 연결되어있는 것을 유념

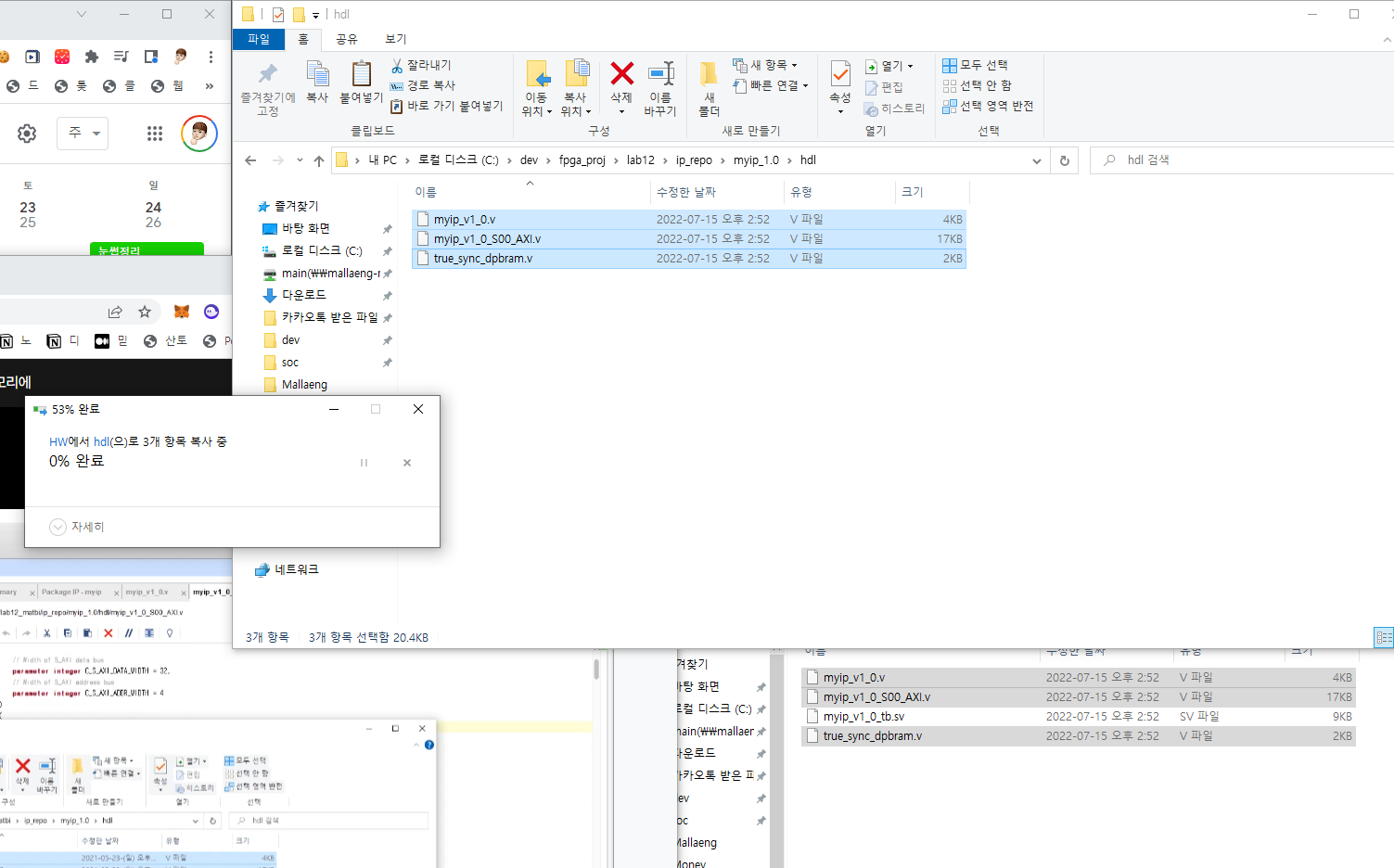

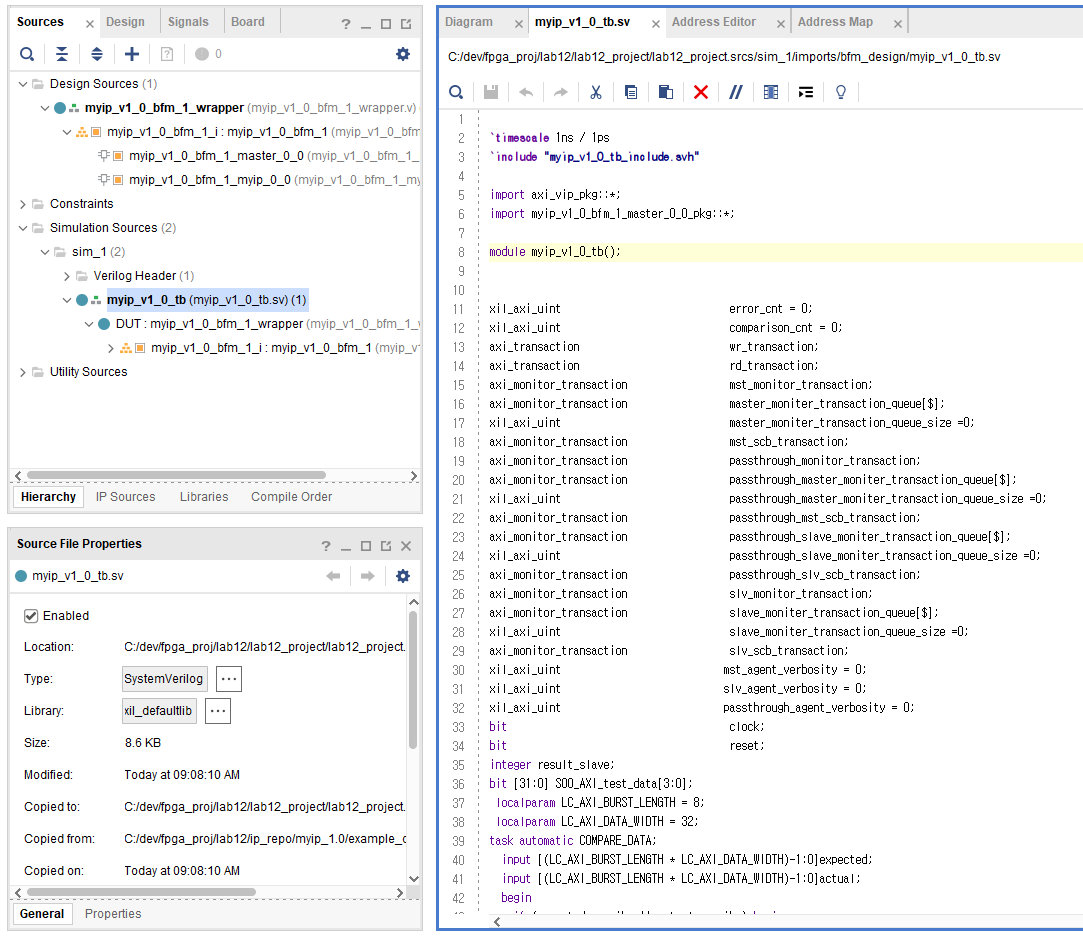

이쪽 파일을 실습 파일로 변경해줄건데

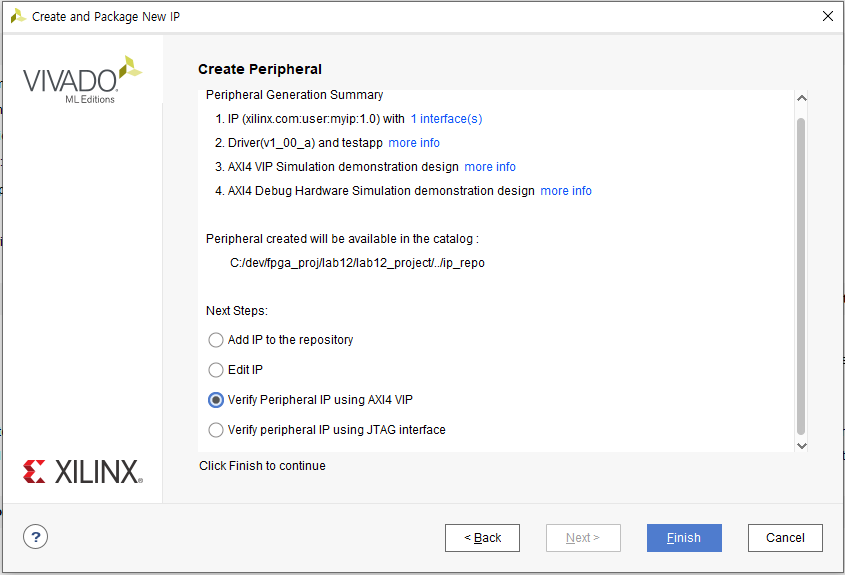

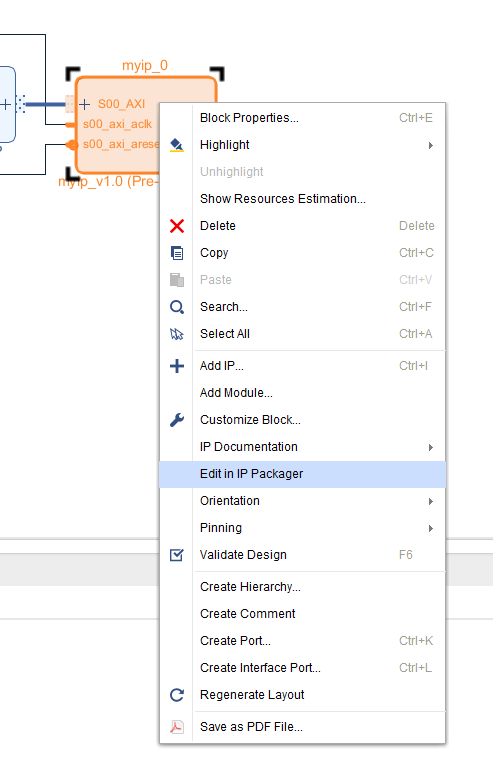

edit in ip_package를 통하면 ip_repo 폴더가 생기며, 이쪽을 이용한다.

C:\dev\fpga_proj\lab12\ip_repo\myip_1.0\hdl

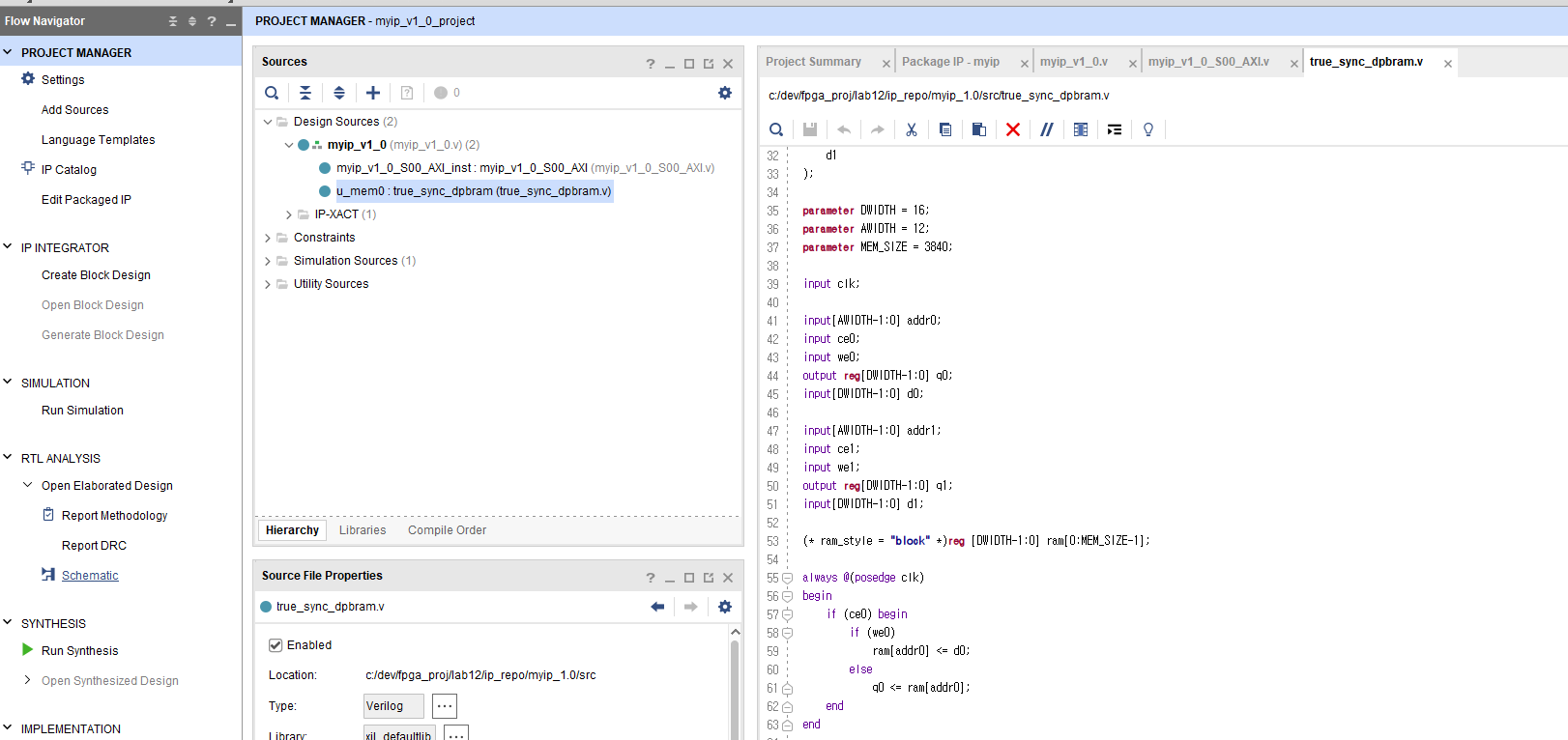

Schematic을 통한 구조관찰

그리고나서 지금까지 우리가 수정한 것에 따라

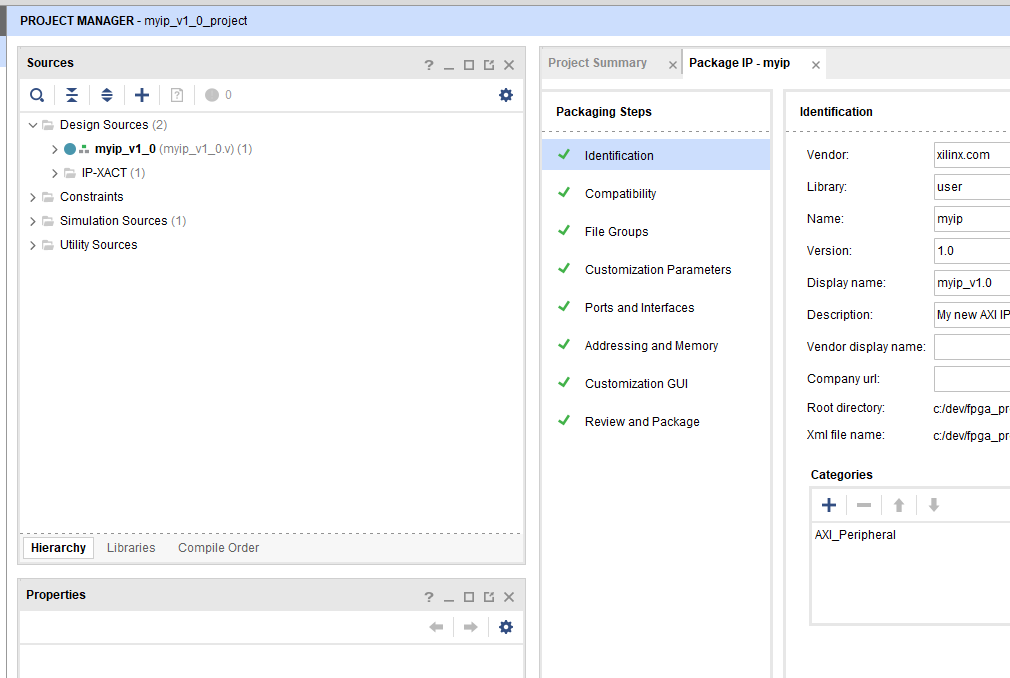

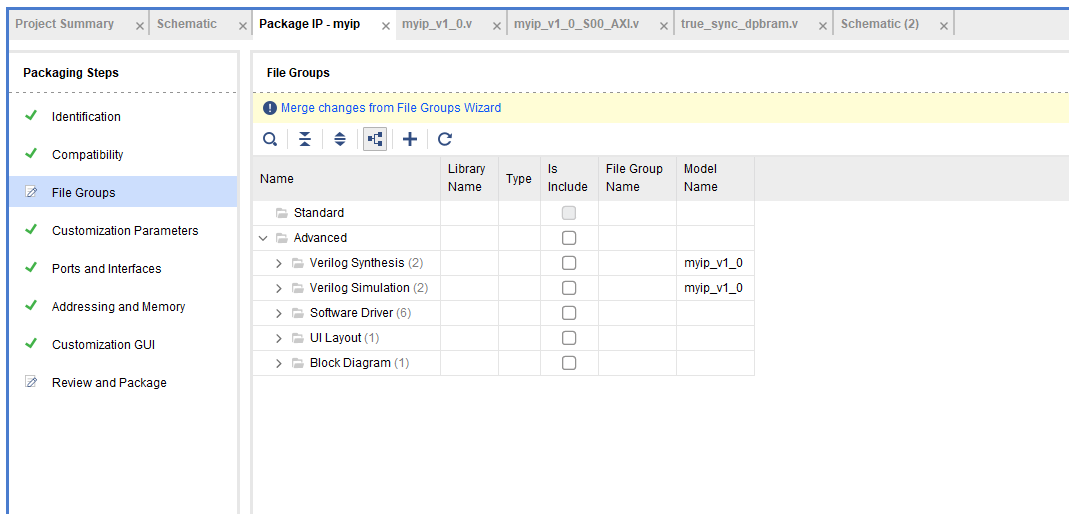

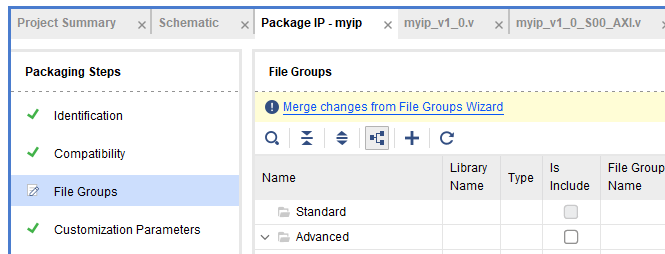

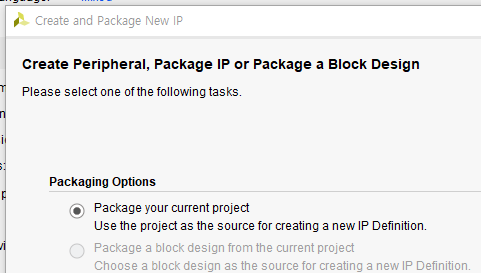

리패키징

그때 체크박스 안된부분 확인

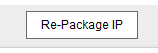

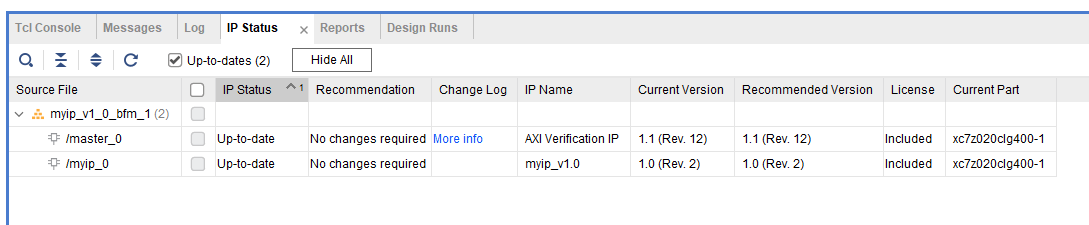

그럼 얘는 이제 repackage 되었다.

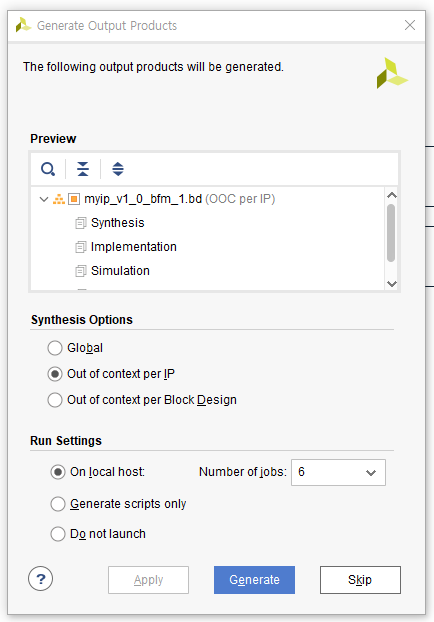

그럼 이때 뜨는 창은 합성여부를 물어보는건데

우리는 시뮬레이션만 할거니깐 skip

그리고 tb도 replace해준다.

이 부분은 시스템 베릴로그로 작성이 되어있으며

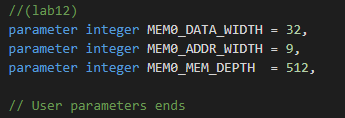

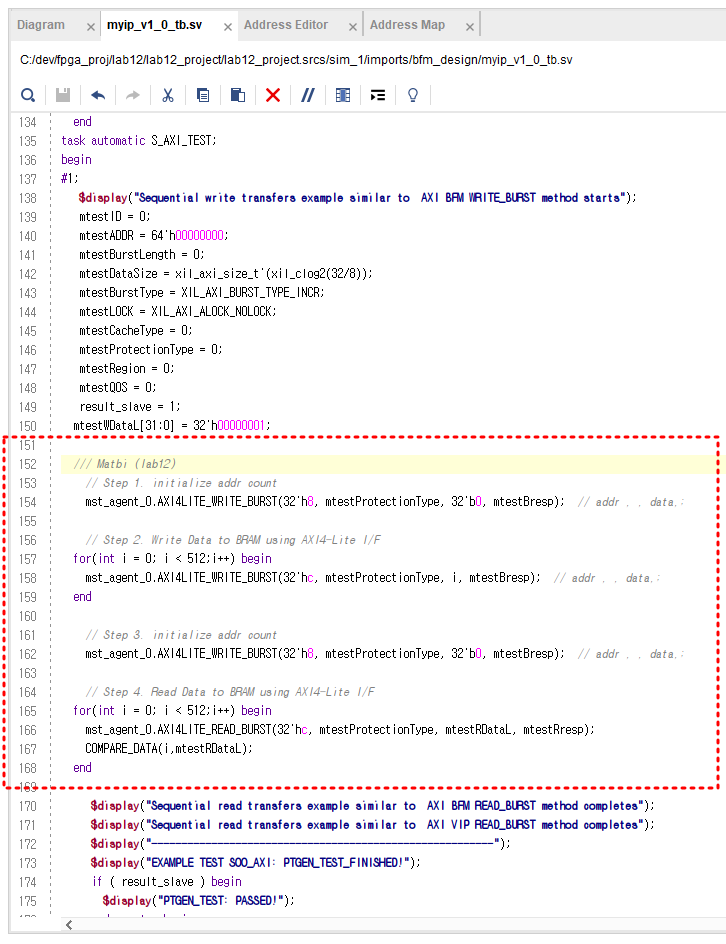

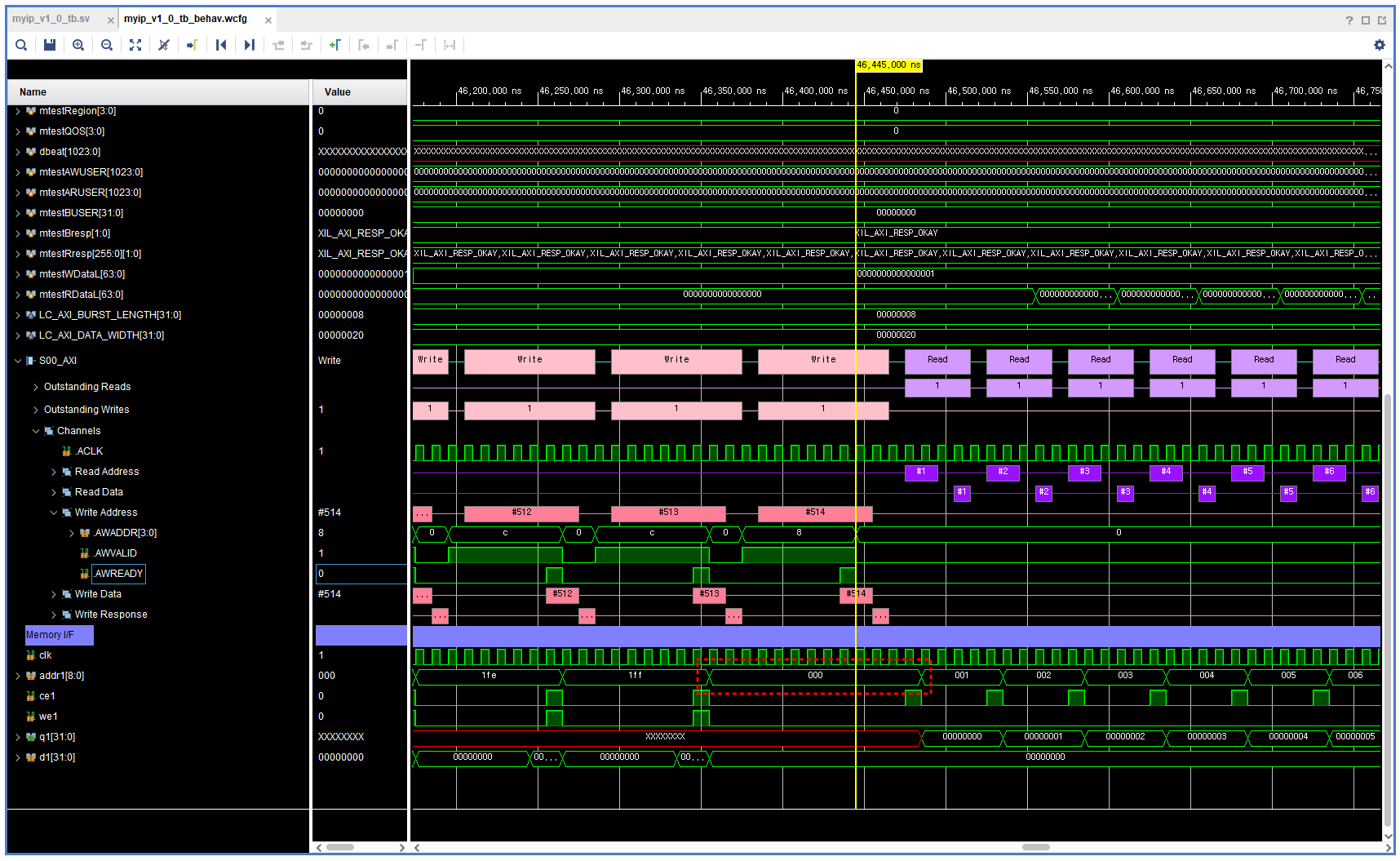

512번 읽고 쓰기

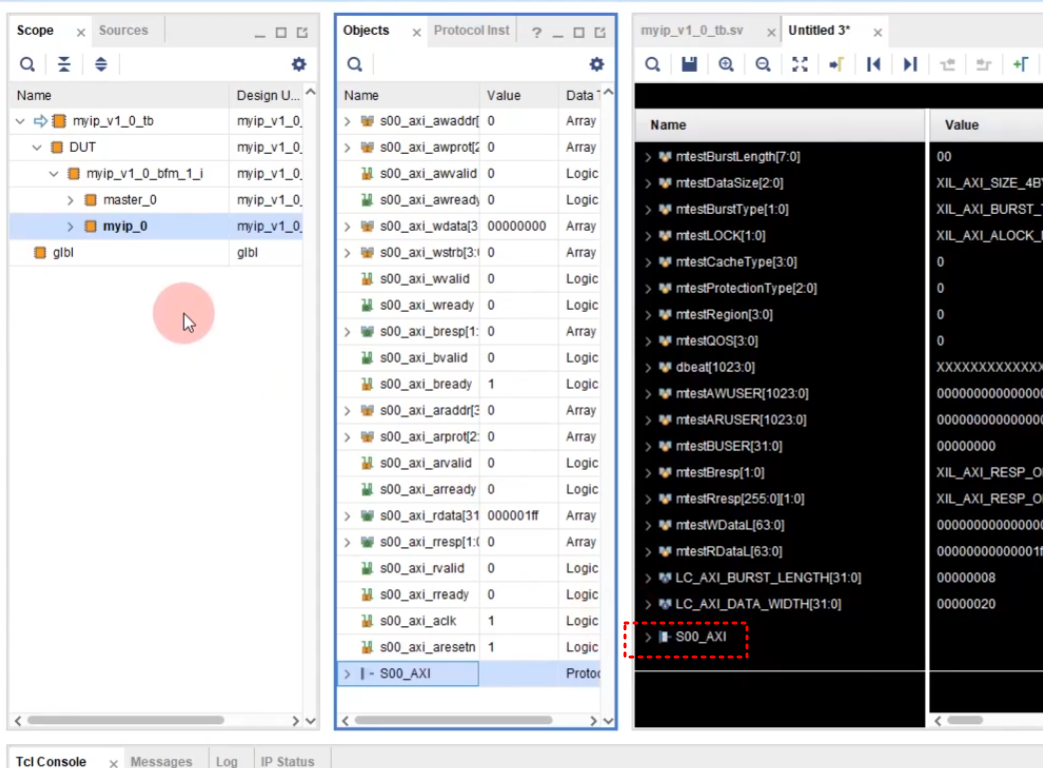

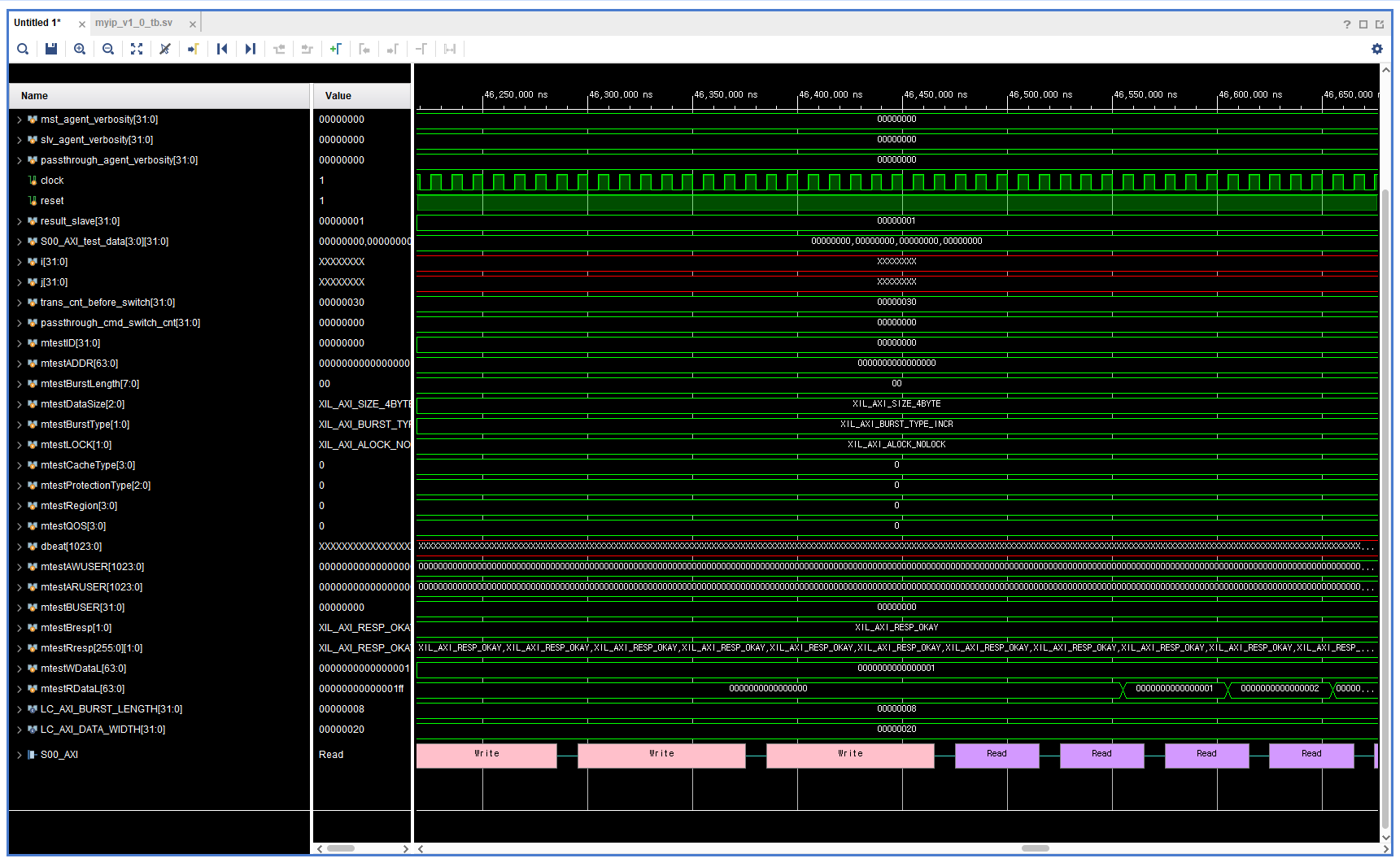

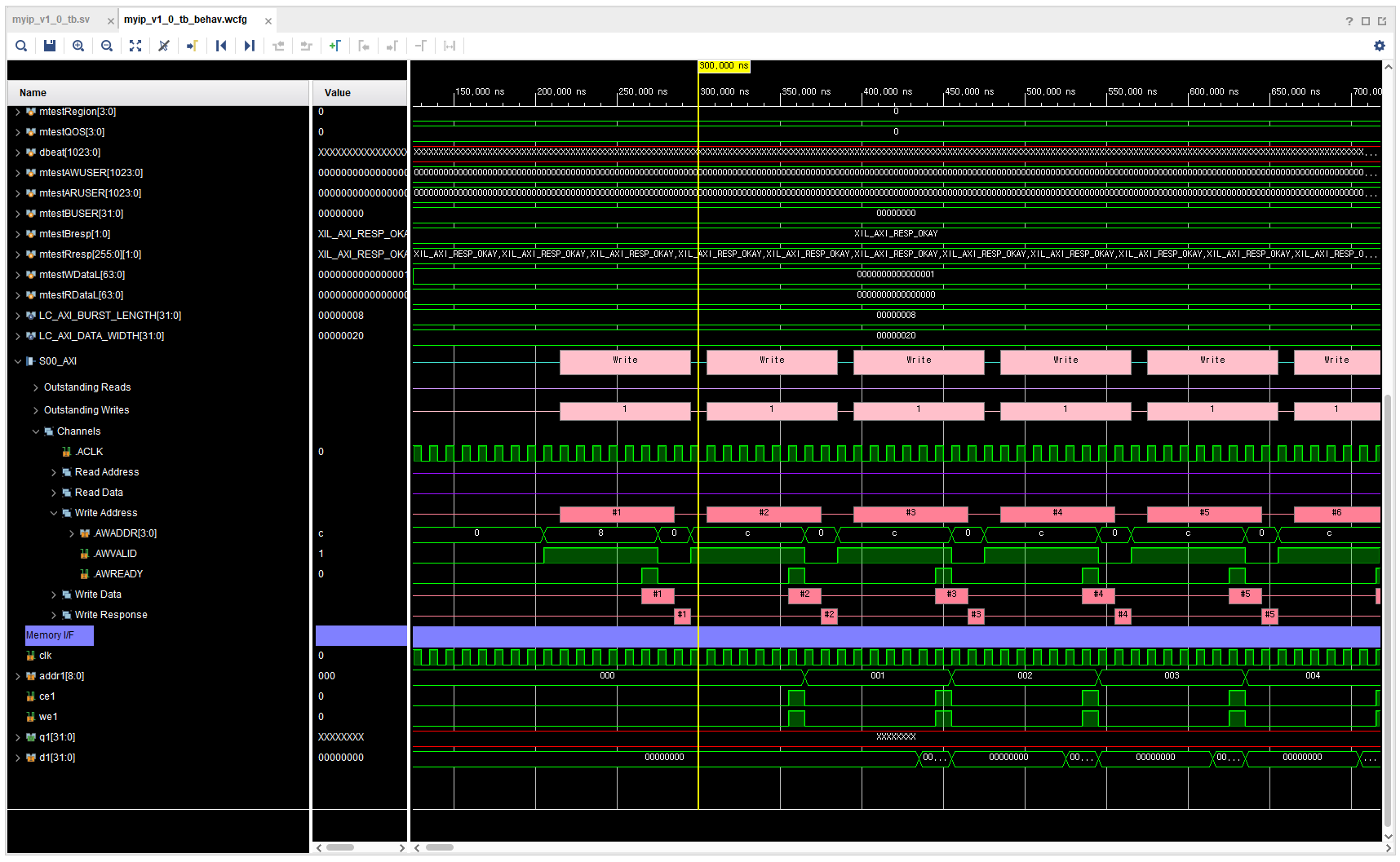

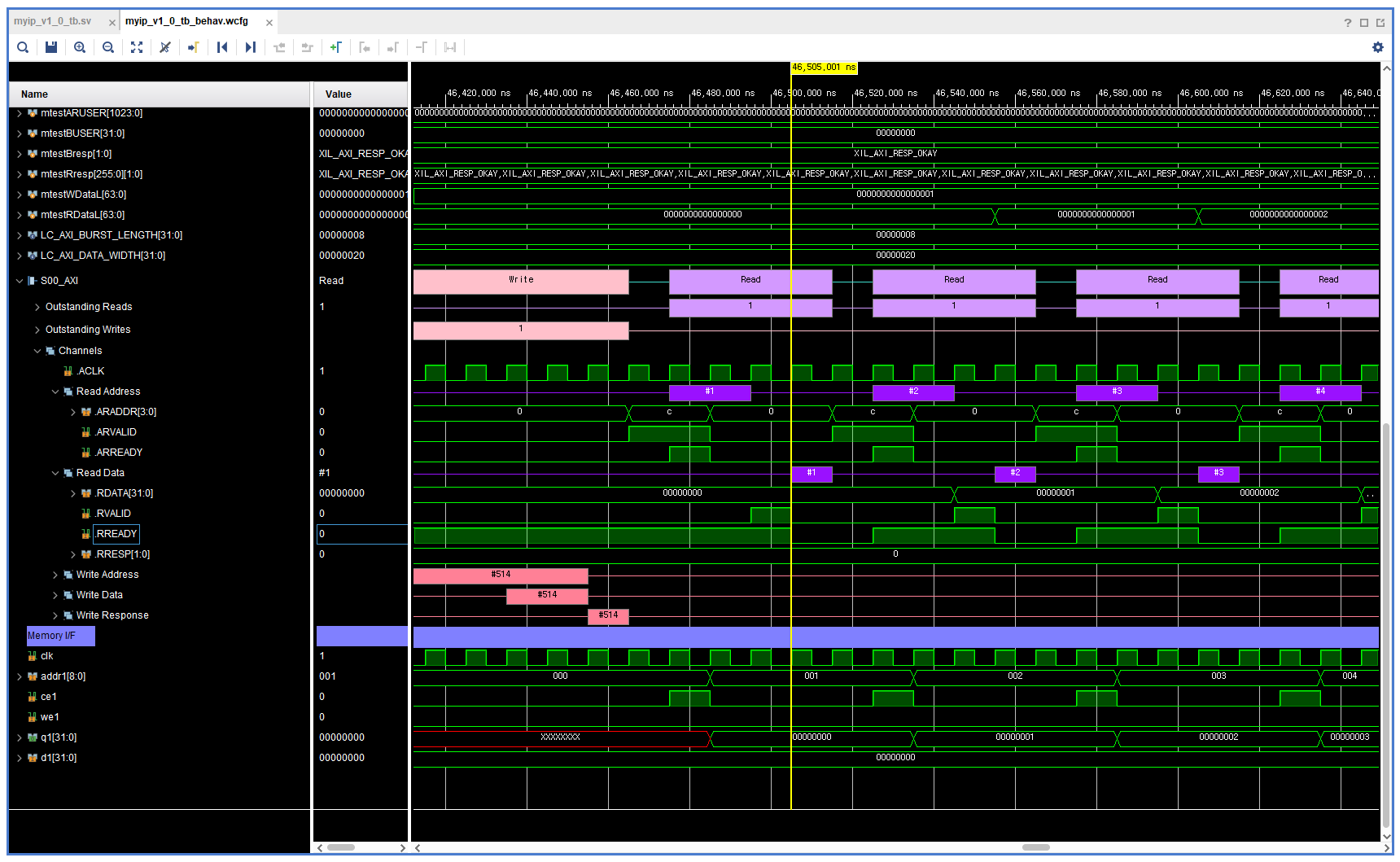

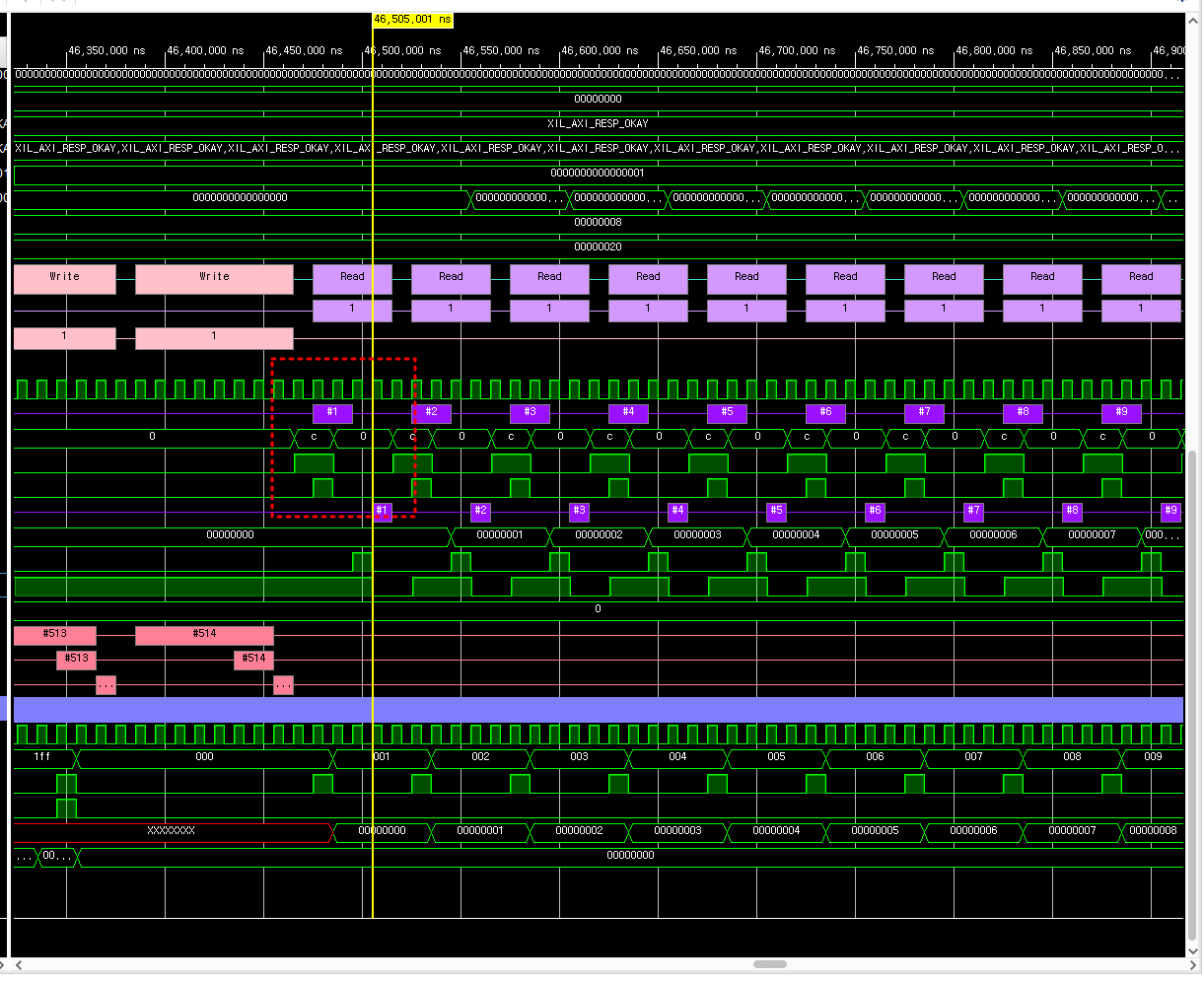

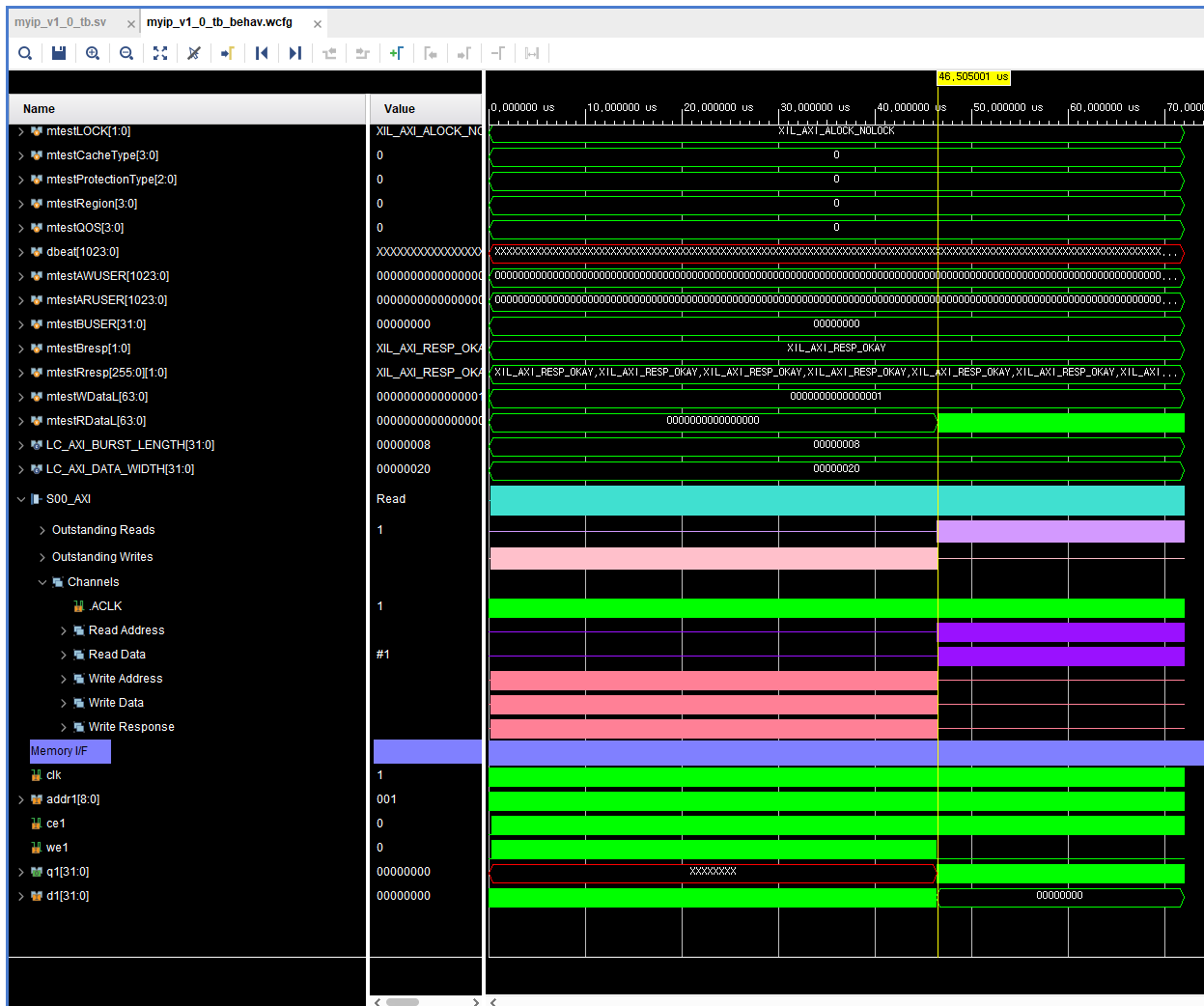

Run Simulation을 해보자.

어 왜 simulation이 안되지.

껏다켜니 된다.

(팁, divider 활용)

초기화를 포함한 Write의 초기부분

overflow로 다시 1로 돌아가는데

만약 overflow 되지 않았다면

addr counter를 직접 0으로 초기화를 해주었어야함.

Read의 초기

---

지금 한 것을 fpga에 올려서 동작을 확인한다.

---

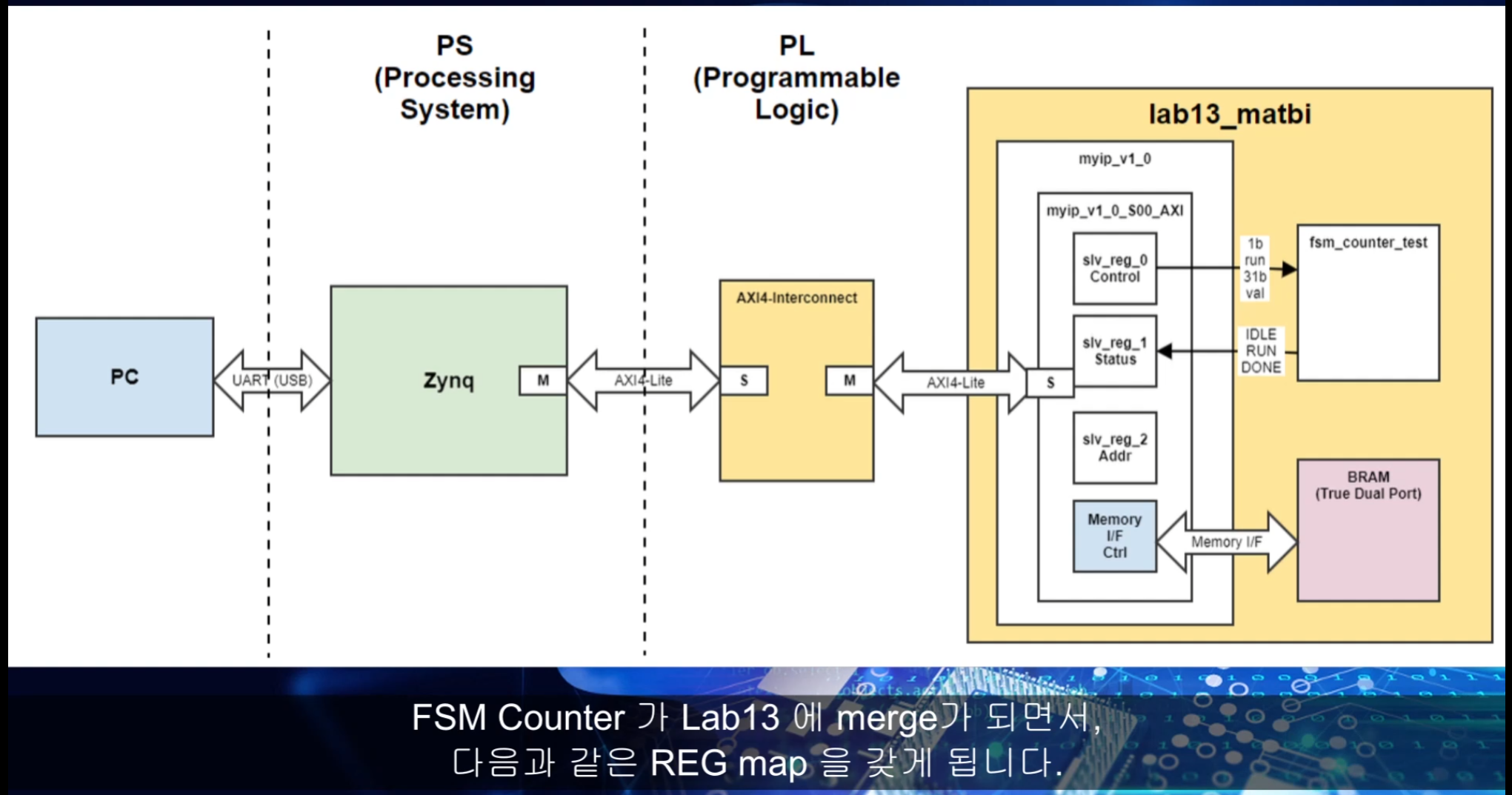

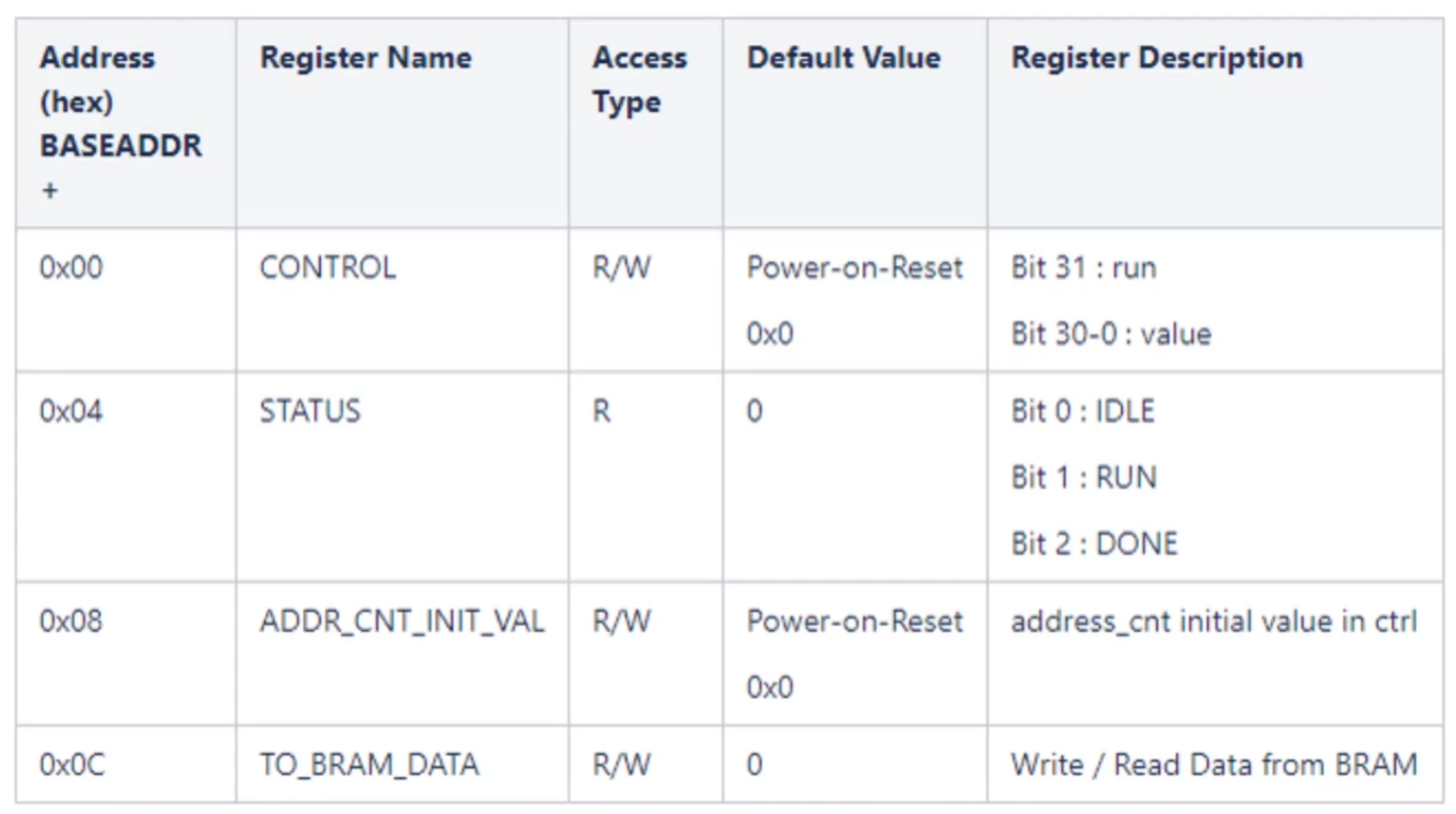

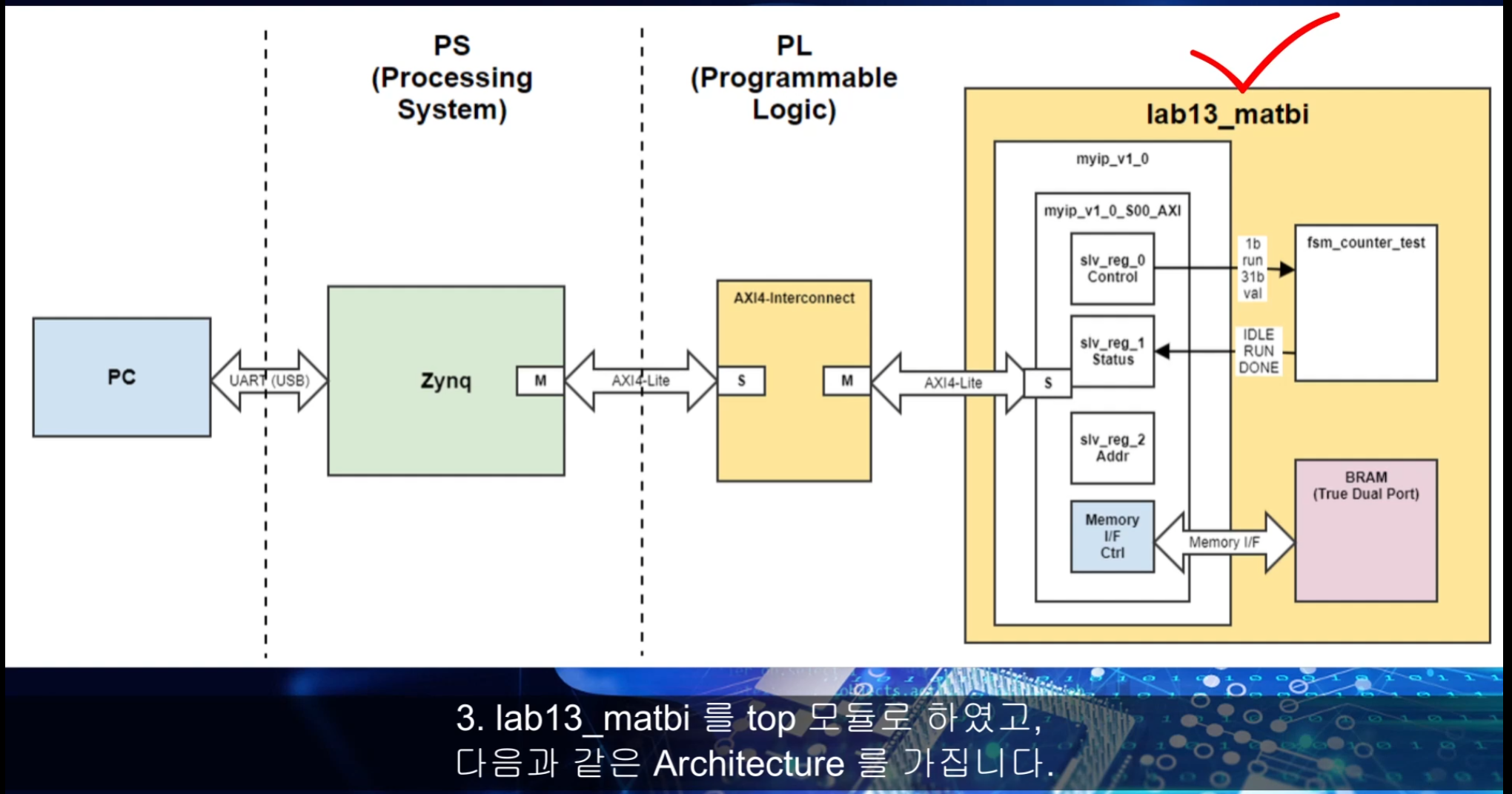

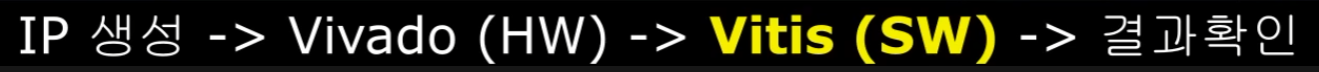

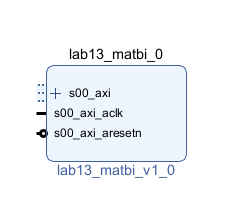

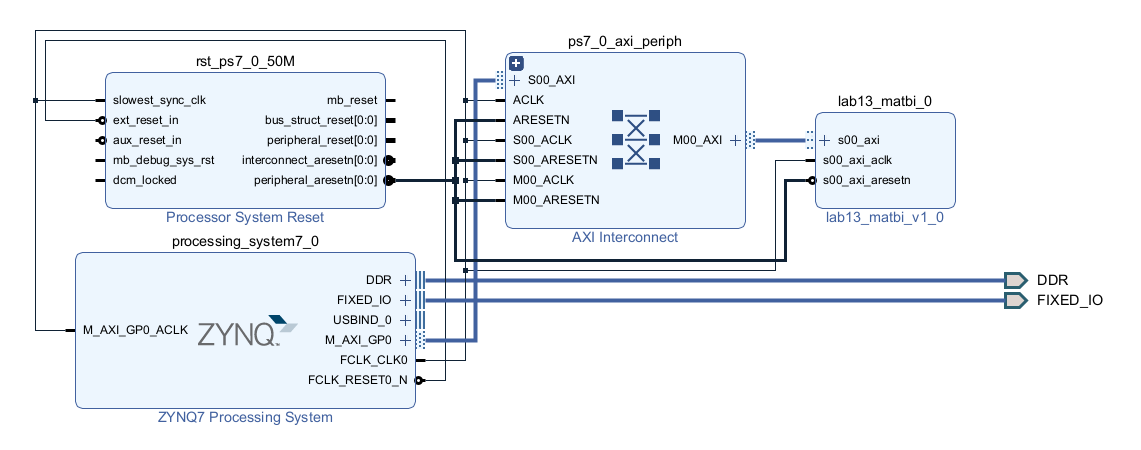

탑모듈이 생기면서 아키텍쳐 국소 변경

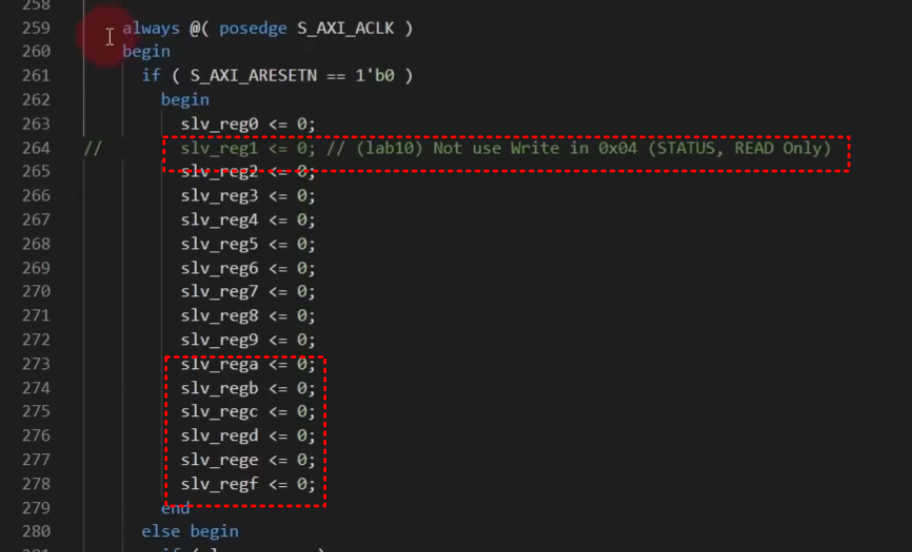

레지스터 16개로 늘리고

FSM Counter 추가

대부분 재활용

다만 naming & address는 일부변경

---

ip

project

ip

zynq

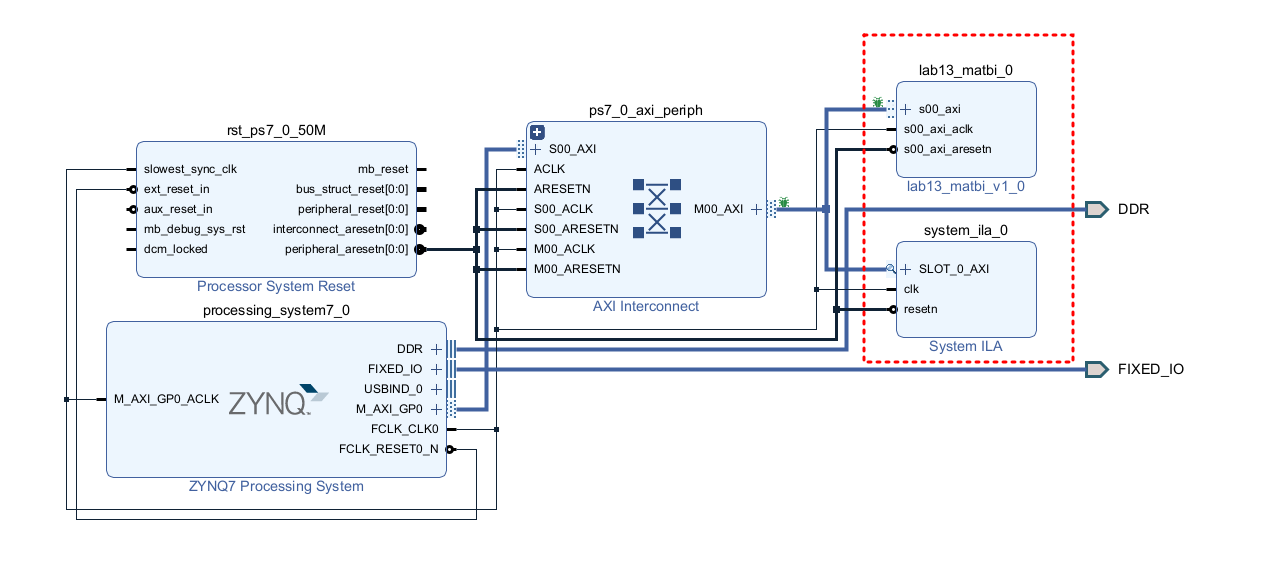

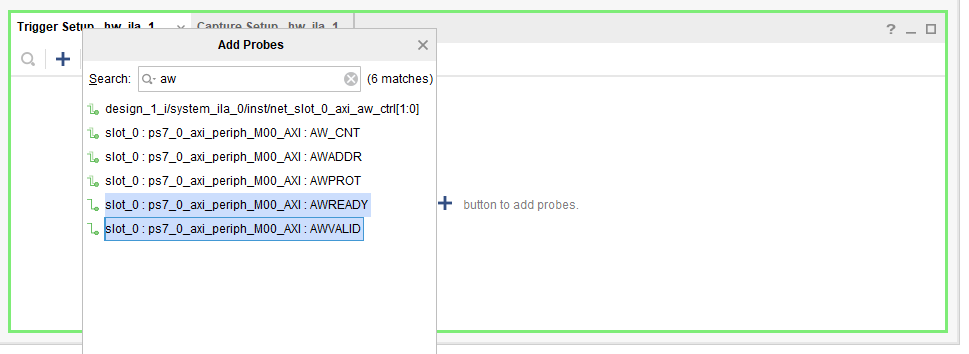

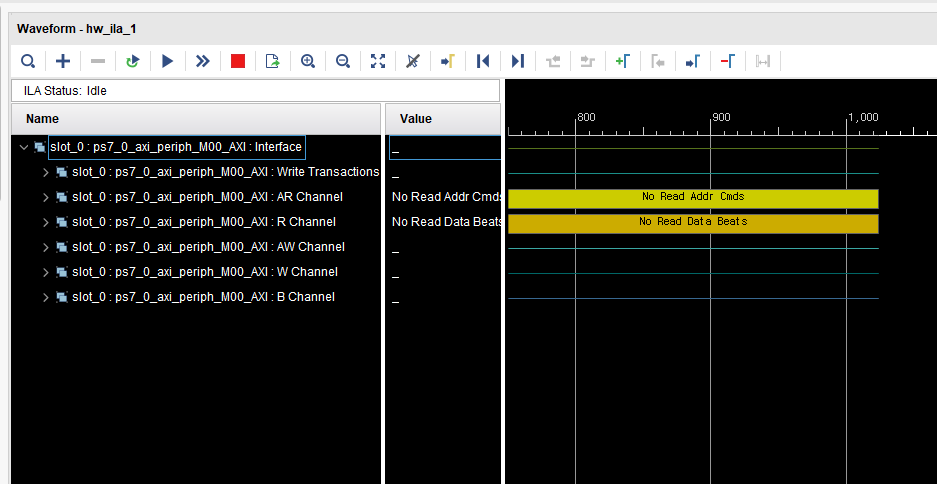

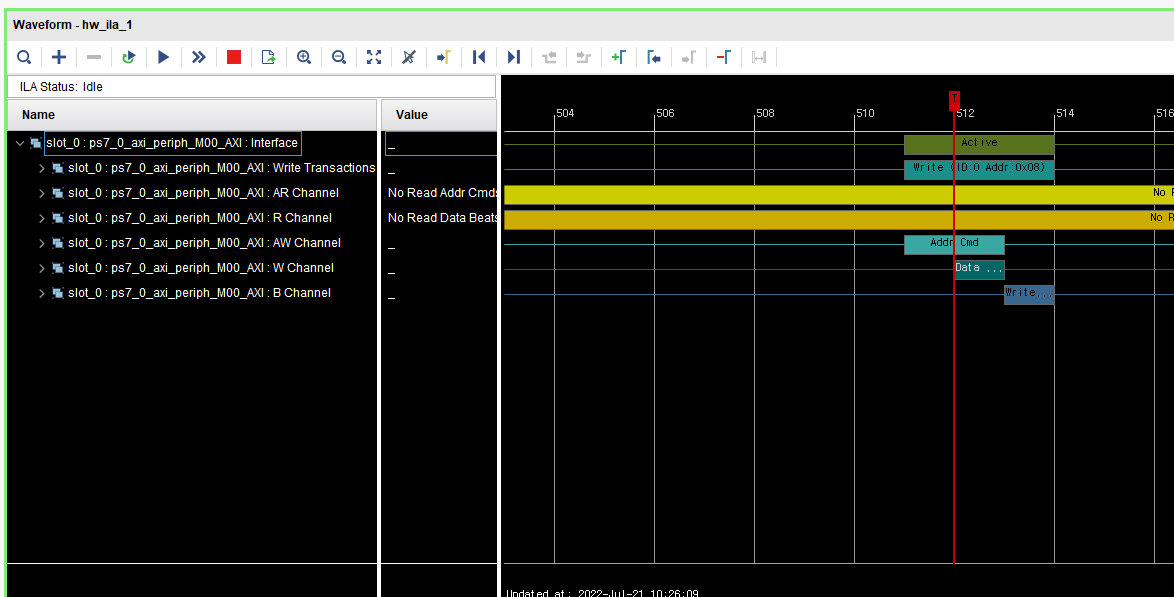

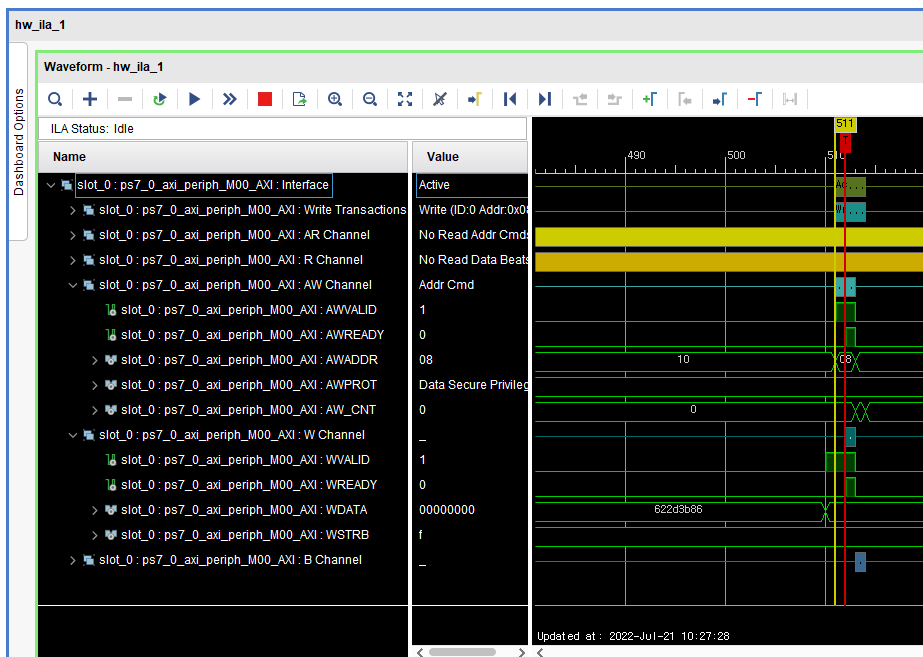

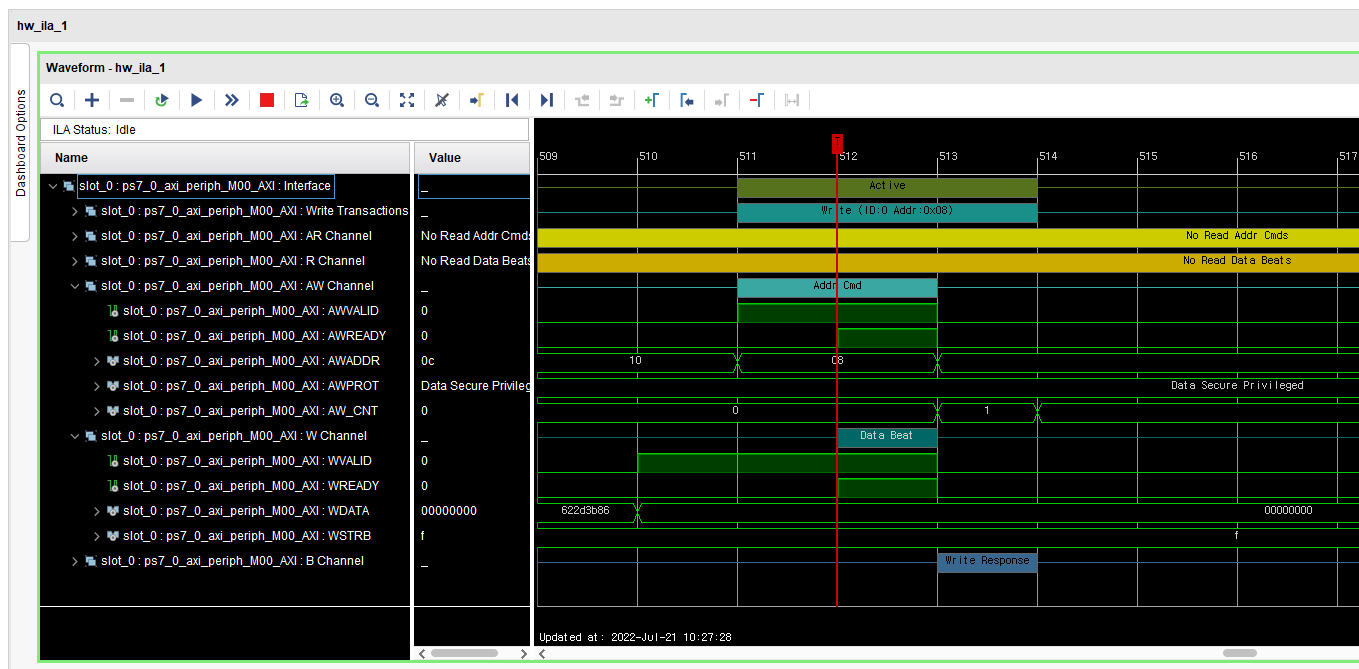

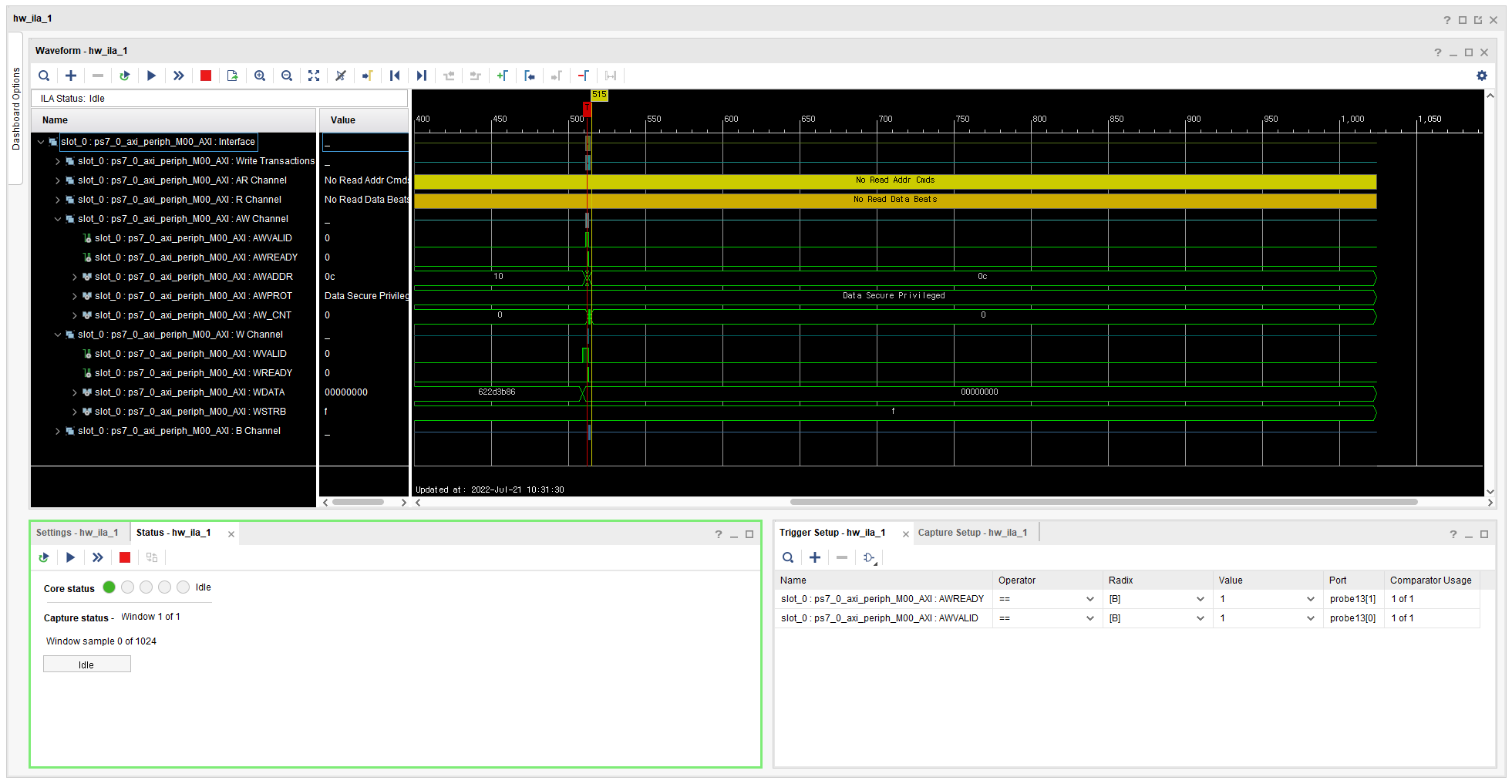

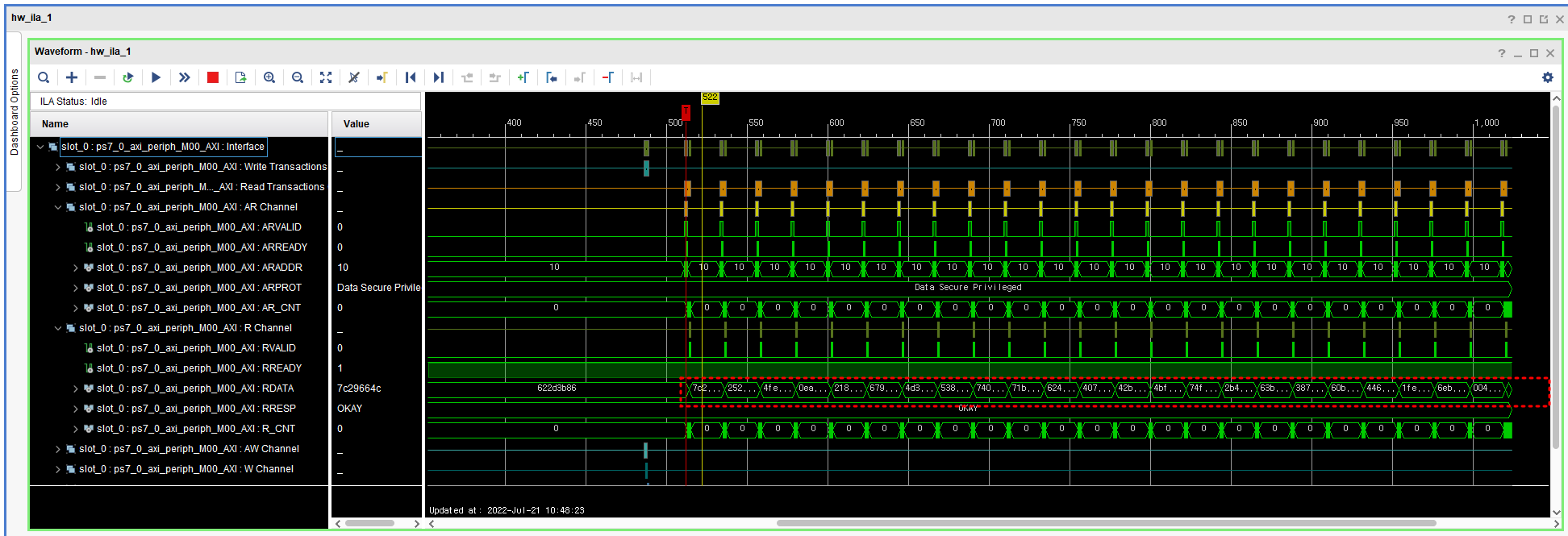

waveform을 dump받는 방법, ila를 추가하기

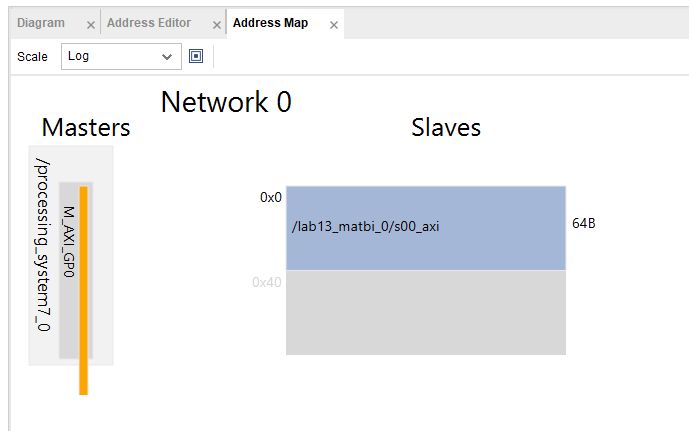

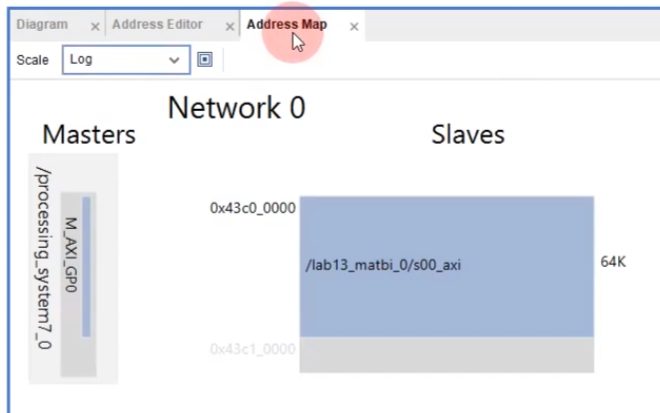

(0x0과 0x43c 주의)

wrapper

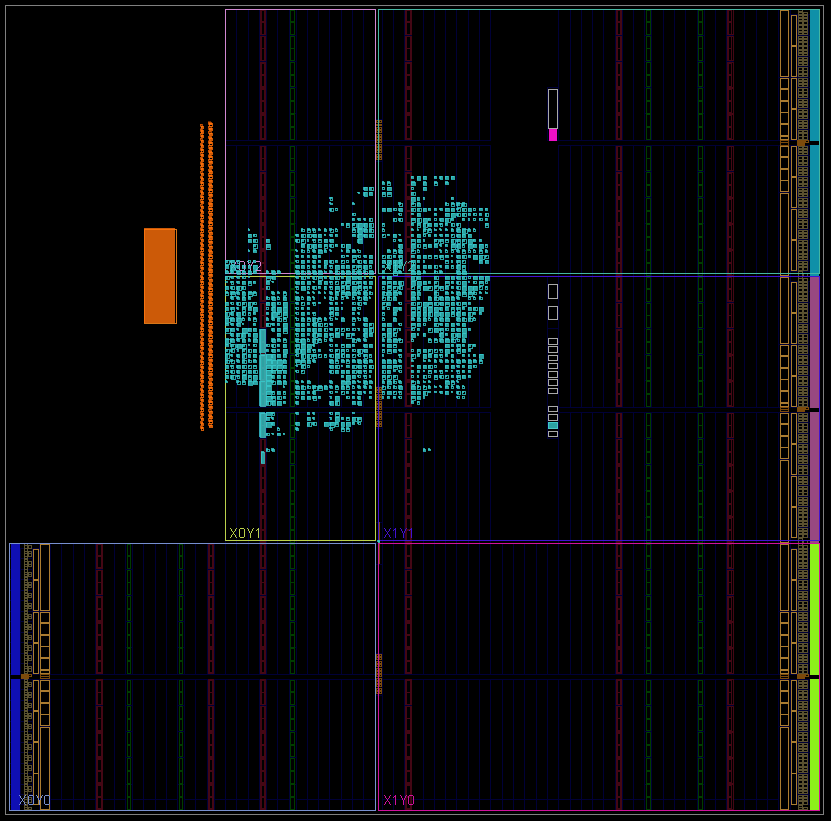

bitstream

확인해주는데, 다시한번 말하지만

지금 디자인은 워낙 간단해서

violation이 나오기 쉽지 않다.

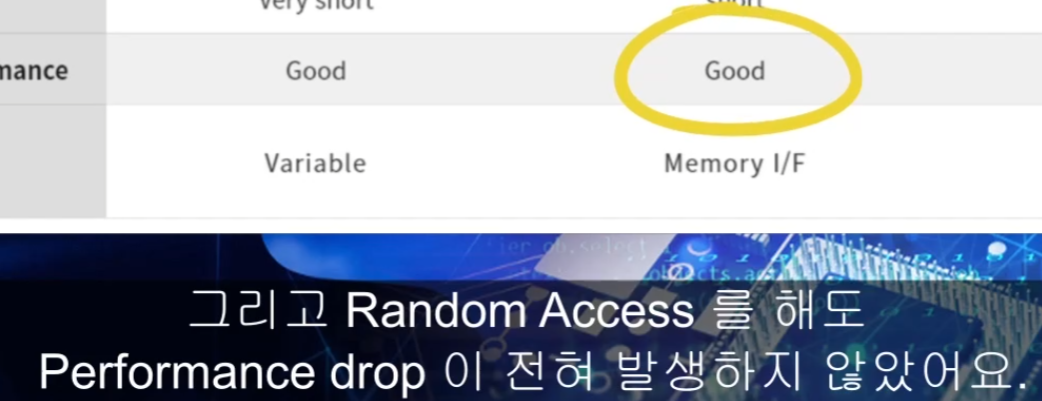

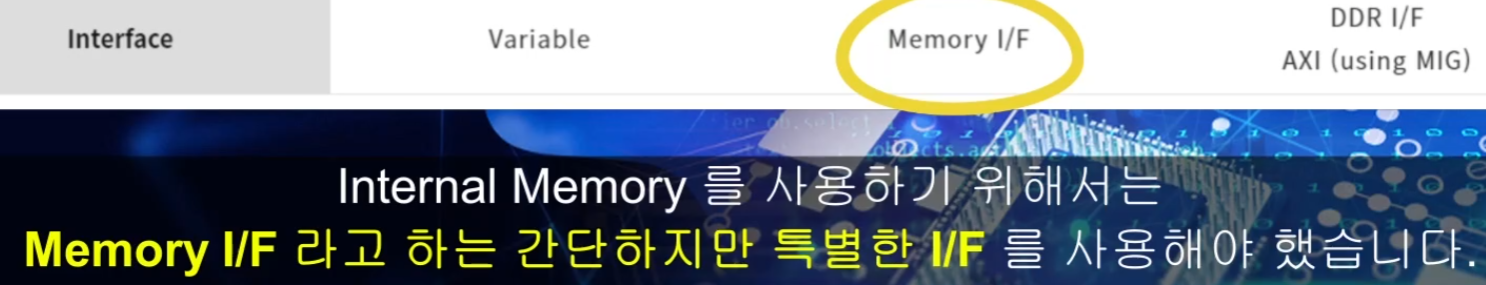

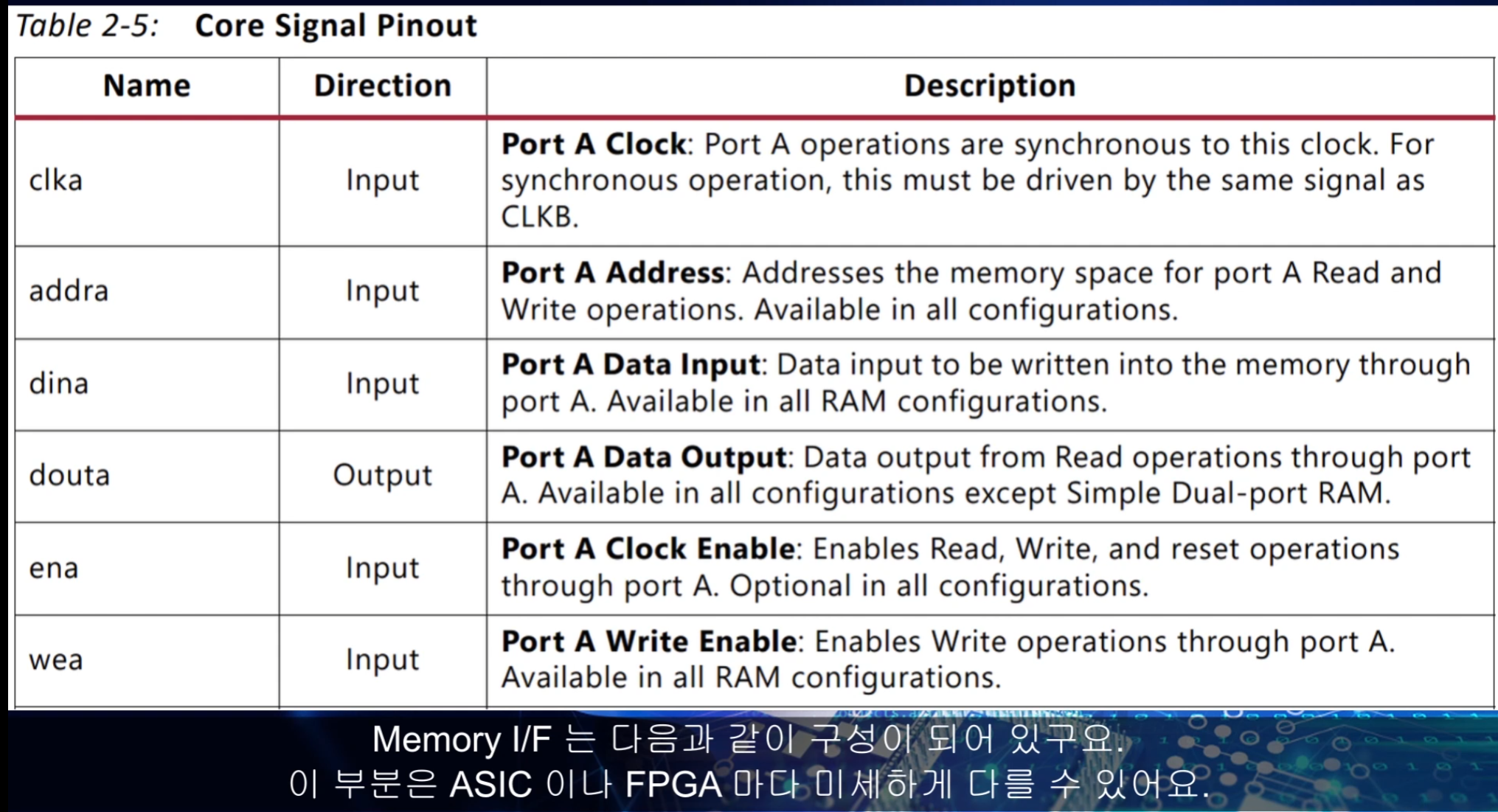

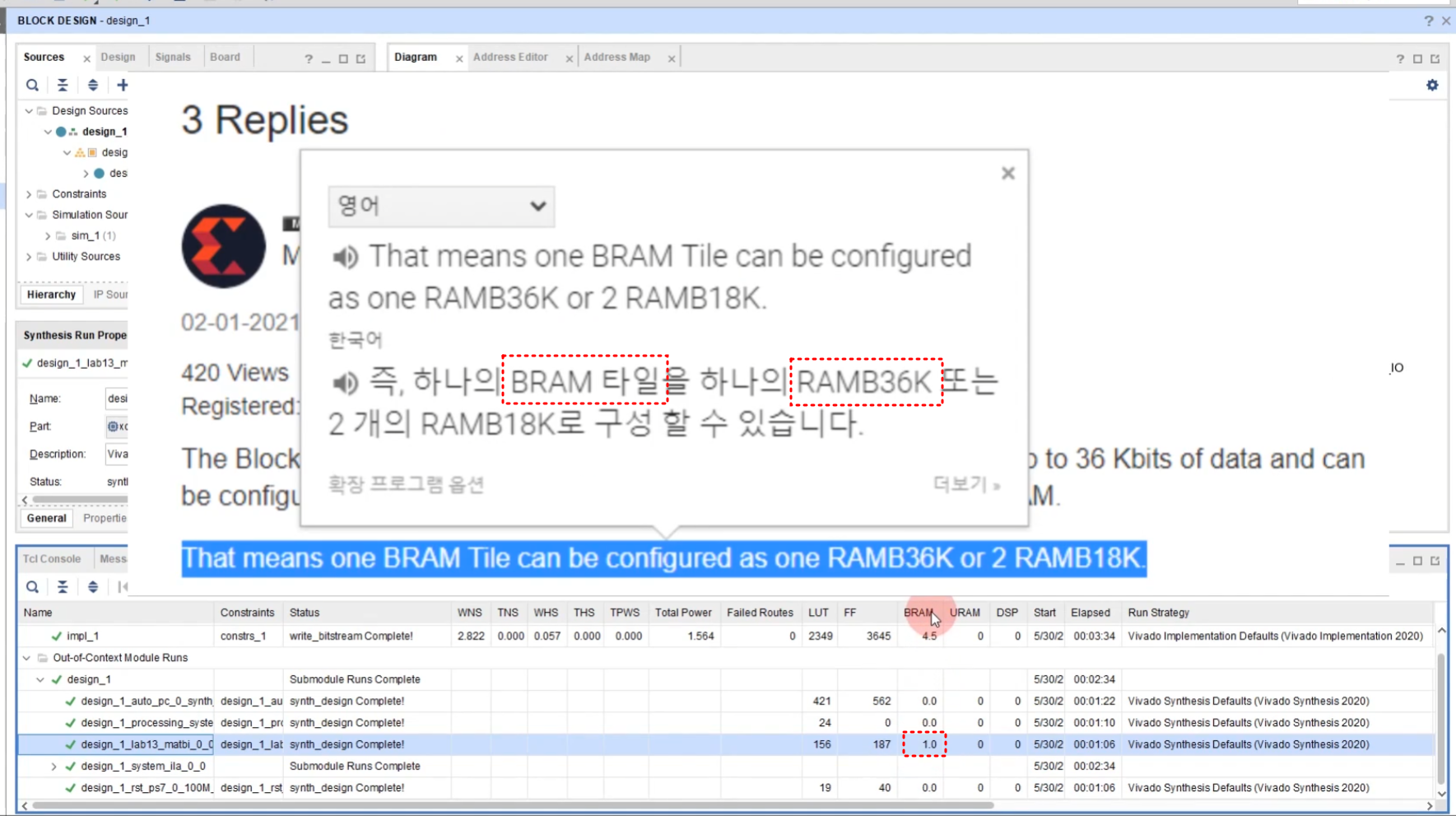

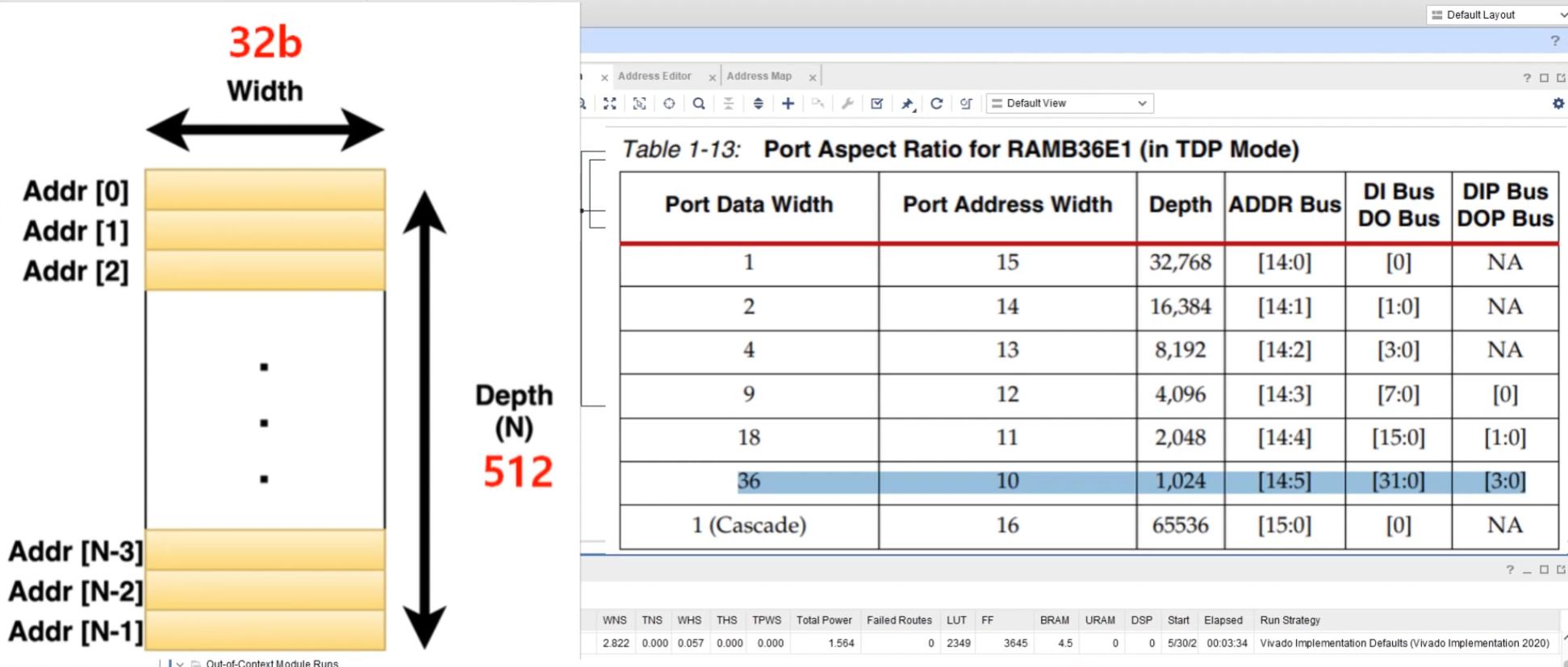

그중에서 BRAM

딱 잘맞게 쓰고 있는데

Width Depth를 조금이라도 더쓰게 되면

인스턴스 하나 더 불러오니

최적화 잘할것

그때 다음표 참고

export hw

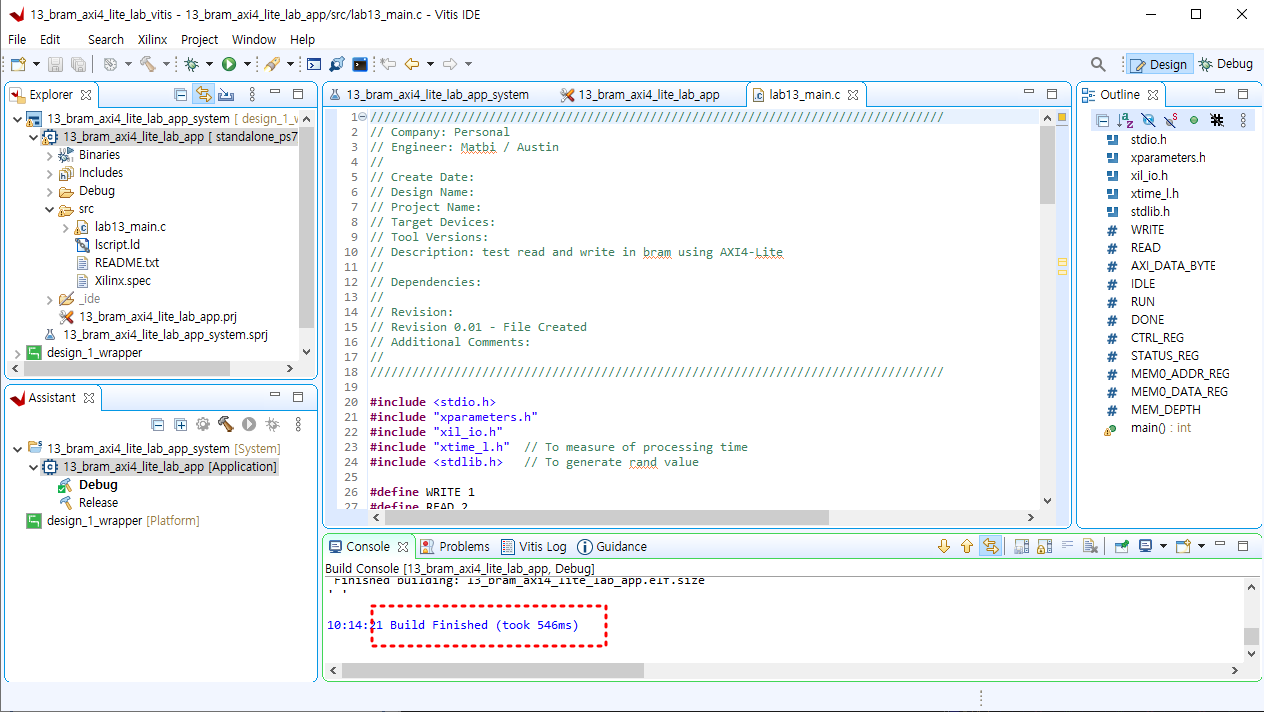

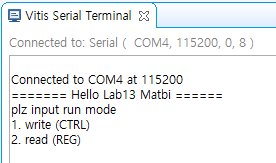

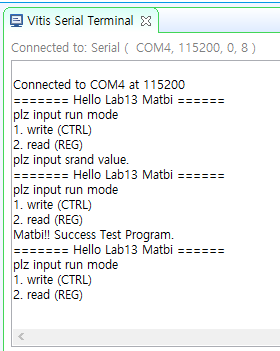

vitis

build finish

엄청 빠르다.

추가적으로 이 시간 보여주는 모듈도 항상 추가하면 좋겠다.

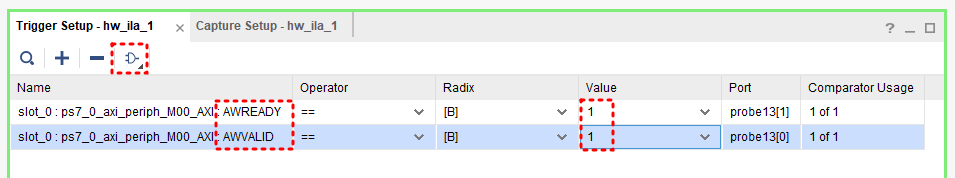

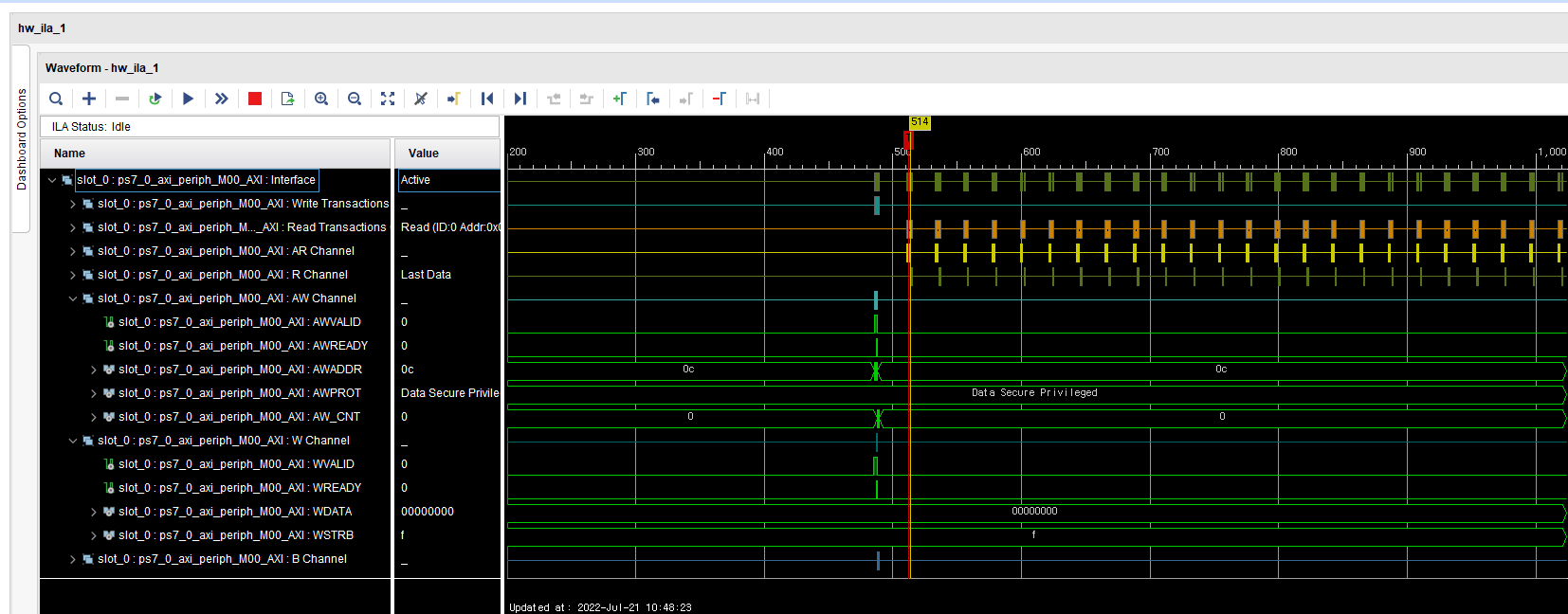

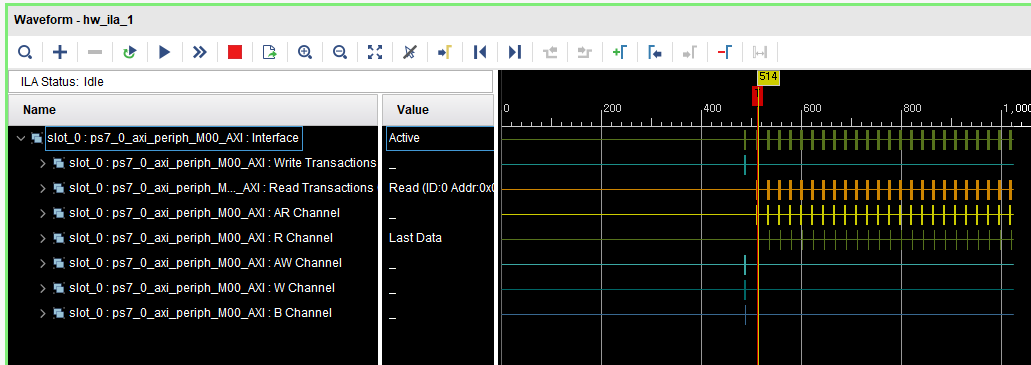

잘 돌아가는지 실제로 확인하기 위하여

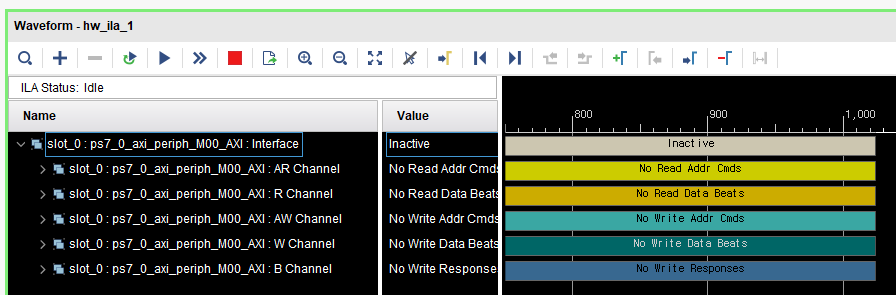

ila 붙혀놓은 것을 이용해

waveform dump를 이용해

눈으로 확인해보도록 하자.

vivado의 open hw manager

여기서 triggering을 해야한다.

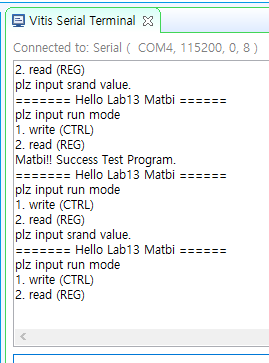

그리고 여기에서 vitis로 rand값을 넣어주어야한다.

음 근데 vitis로 trigger까지 주었음에도 불구하고

512번 등장해야 하는데 아직까지도 1개만 등장하는 오동작이 있다.

https://www.inflearn.com/questions/600296

ila triggering - 인프런 | 질문 & 답변

안녕하세요. 13강을 공부중에 있었습니다. vivado에서 ila triggering을 통해 hw의 동작을 확인중인데 (27:51) [FPGA 13장] AXI4-Lite I/F 를 사용하여 Register 가 아닌 메모리에 Write / Read 해보기 - 실습편 &nbs...

www.inflearn.com

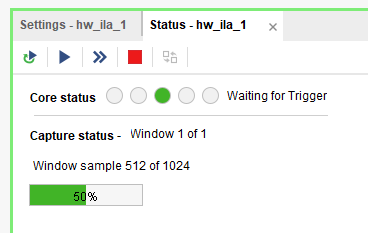

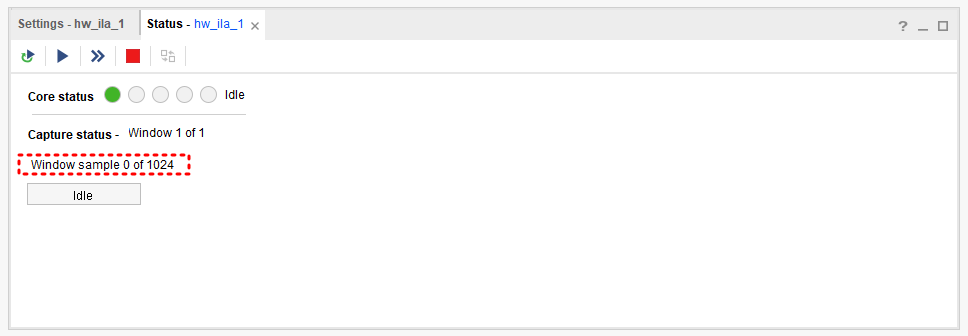

ila는 1024 사이클까지만 샘플을 받을 수 있다.

그래서 우리는 axi4lite를 모두 캡쳐하지 못한다.

(write, read를 모두)

Read는 잘된다.

---

'적극적 생각 > FPGA' 카테고리의 다른 글

| (중요) 0721 - 섹션4 - AXI4Lite 이용해 BRAM에 RW [복습] (0) | 2022.07.21 |

|---|---|

| AXI BRAM Controller (0) | 2022.07.21 |

| 모식도 작성툴, gliffy, drawio (0) | 2022.07.17 |

| 0717 - 섹션3 - HW Sleep, FSM(IDLE→RUN→DONE) (0) | 2022.07.17 |

| 이더넷 (0) | 2022.07.17 |