화가나서 죽을 것 같아 ...

현재 RTL이 제대로 동작하지 않는듯하다.

sensitivy와 제어를 잘못 다룬 것 같다.

이 부분을 점검하자.

`timescale 1ns / 1ps

module dice_controller(clk, reset_n, reset_button, shuffle_button, led);

// io

input clk;

input reset_n;

input reset_button;

input shuffle_button;

output reg [3:0] led;

// reg

reg [1:0] dice_status;

reg [31:0] count;

// init

initial begin // reset initial

dice_status = 2'b00;

led = 4'b1111;

count = 0;

end

// main

always@(posedge clk or negedge reset_n) begin // reset signal

if(!reset_n) begin

dice_status <= 2'b00;

led <= 4'b1111;

count <= 0;

end

end

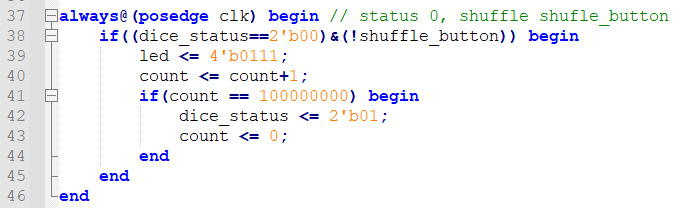

always@(posedge clk) begin // status 0, shuffle shufle_button

if((dice_status==2'b00)&(!shuffle_button)) begin

led <= 4'b0111;

count <= count+1;

if(count == 100000000) begin

dice_status <= 2'b01;

count <= 0;

end

end

end

always@(posedge clk) begin // status 1

if(dice_status==2'b01) begin

led <= 4'b0011;

count <= count+1;

if(count == 100000000) begin

dice_status <= 2'b10;

count <= 0;

end

end

end

always@(posedge clk) begin // status 2, reset reset_button

//

if((dice_status==2'b10)&(!reset_button)) begin

dice_status <= 2'b00;

led <= 4'b1111;

count <= 0;

end

end

endmodule

모식도는 다음과 같다.

모식도와 코드가 크게 달라보이지 않으므로

sensitivity와 if조건을 잘 확인해보자.

여기는 틀린건 없어보인다.

여기는 dice_status와 shuffle_button을 요구로한다.

https://inst.eecs.berkeley.edu/~cs150/fa06/Labs/verilog-ieee.pdf

점검해야 하는 지점은 두 지점인데

- posedge clk 만 두어도 되는가

- & 써야하는가 && 써야하는가

점심먹으면서 코드 째려보고 있었는데

아 이쪽이 잘못된게 맞기는 하다.

이 구문은 논리적으로 동작될 수 없다.

clk 그리고 concurrent를 많이 생각해야한다.

수정해서 다시 비트스트림 넣어봤는데

아직도 안된다... ㅠ_ㅠ 왜... ㅠ_ㅠ

`timescale 1ns / 1ps

module dice_controller(clk, reset_n, reset_button, shuffle_button, led);

// io

input clk;

input reset_n;

input reset_button;

input shuffle_button;

output reg [3:0] led;

// reg

reg [1:0] dice_status;

reg [31:0] count;

// init

initial begin // reset initial

dice_status = 2'b00;

led = 4'b1111;

end

// main

always@(posedge clk or negedge reset_n) begin // reset signal

if(!reset_n) begin

dice_status <= 2'b00;

led <= 4'b1111;

end

end

always@(posedge clk) begin // status 0, shuffle shufle_button

if((dice_status==2'b00)&(!shuffle_button)) begin

led <= 4'b0111;

dice_status <= 2'b01;

end

end

always@(posedge clk) begin // status 1

if(dice_status==2'b01) begin

count <= count+1;

if(count == 100000000) begin

dice_status <= 2'b10;

count <= 0;

led <= 4'b0011;

end

end

end

always@(posedge clk) begin // status 2, reset reset_button

//

if((dice_status==2'b10)&(!reset_button)) begin

dice_status <= 2'b00;

led <= 4'b1111;

end

end

endmodule

그냥 led 말고 버튼 누르면 깜빡이는 led로 축소해서 진행해보자 ... ㅠ_ㅠ 왜이래 이거 정말...

'적극적 생각 > FPGA' 카테고리의 다른 글

| dice_new 오류해결완료 (0) | 2022.08.16 |

|---|---|

| dice_new (0) | 2022.08.16 |

| @sensitivity (0) | 2022.08.12 |

| 대주제 (0) | 2022.08.10 |

| pci에 대해 공부하는 법 (0) | 2022.08.09 |