단톡방을 통해 물어보면서 문제를 해결했고

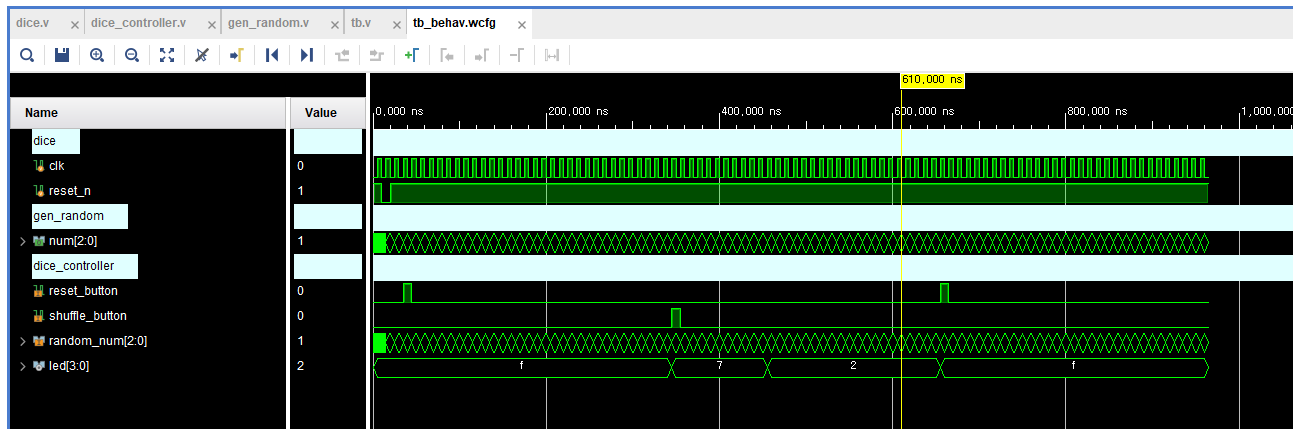

자 우선 결과적으로 된다.

`timescale 1ns / 1ps

module dice(clk, reset_n, btn, led);

// io

input clk;

input reset_n;

input [1:0] btn;

output [3:0] led;

wire [2:0] num;

// instantiation

dice_controller

dice_controller_0

(

.clk(clk),

.reset_n(reset_n),

.reset_button(btn[0]),

.shuffle_button(btn[1]),

.random_num(num),

.led(led)

);

gen_random

gen_random_0

(

.clk(clk),

.reset_n(reset_n),

.num(num)

);

endmodule

이 두 지점이 문제였는데

wire [2:0] num

.num(num)

num은 output 이므로 input port가 연결되는 것이 아니다.

num이 input으로 들어가주기 위해서는 input wire 이어야 한다.

왜? 이 지점이 아직도 아주 완벽히는 이해가 안간다.

입력신호는 반드시 net 형이기 때문에

reg로 들어온 출력신호를 net으로 변환해주어야 한다.

정도로 이해하자.

=====

자 다시 원래 흐름으로 돌아온다.

random num으로 생성된 4를 잘 받아와서 보여주고 있다.

이제 다음으로 해야하는일은

깜빡깜빡이는건데

(xsim을통해 sim과 imp구분필요)

중간에 0111으로 표현되는 구간을

깜빡이도록 해주자.

아 우선 그걸 하기에 앞서, 현재 코드가 보드에서 정상적으로 동작하는지를 먼저 봐야겠다.

왜그러냐면 가시주파수가 아닌 영역에서의 깜빡임은 기교의 영역인데 쓸모없는 기교이다.

32'd100000000 는 이진법으로 변환하면

101111101011110000100000000 27자리수다.

32'd300000000 는 이진법으로 변환하면

10001111000011010001100000000 29자리수다.

그러므로 parameter [31:0] WAIT_TIME = 32'd300000000 은 가능하다.

버튼 입력이 에러가 난다면

1) 자동으로 1초 있다가 다음 스테이지로 가게 해보는 것도 방법이고

2) 버튼 대신 스위치를 껏켰해서 동작하게끔 해보는 것도 방법이다.

아 우선 여기까지 탕탕.

'적극적 생각 > FPGA' 카테고리의 다른 글

| Memory mapped I/O and Isolated I/O (0) | 2022.08.23 |

|---|---|

| 왜 인터커넥트가 필요한가. (0) | 2022.08.23 |

| dice_new (0) | 2022.08.16 |

| [프로젝트] 주사위 (작성용2) (0) | 2022.08.12 |

| @sensitivity (0) | 2022.08.12 |