Lecture 1 : Introduction to Verilog

베릴로그는 HDL 종류중 하나. 회사에서 상업목적으로 많이 쓰임.

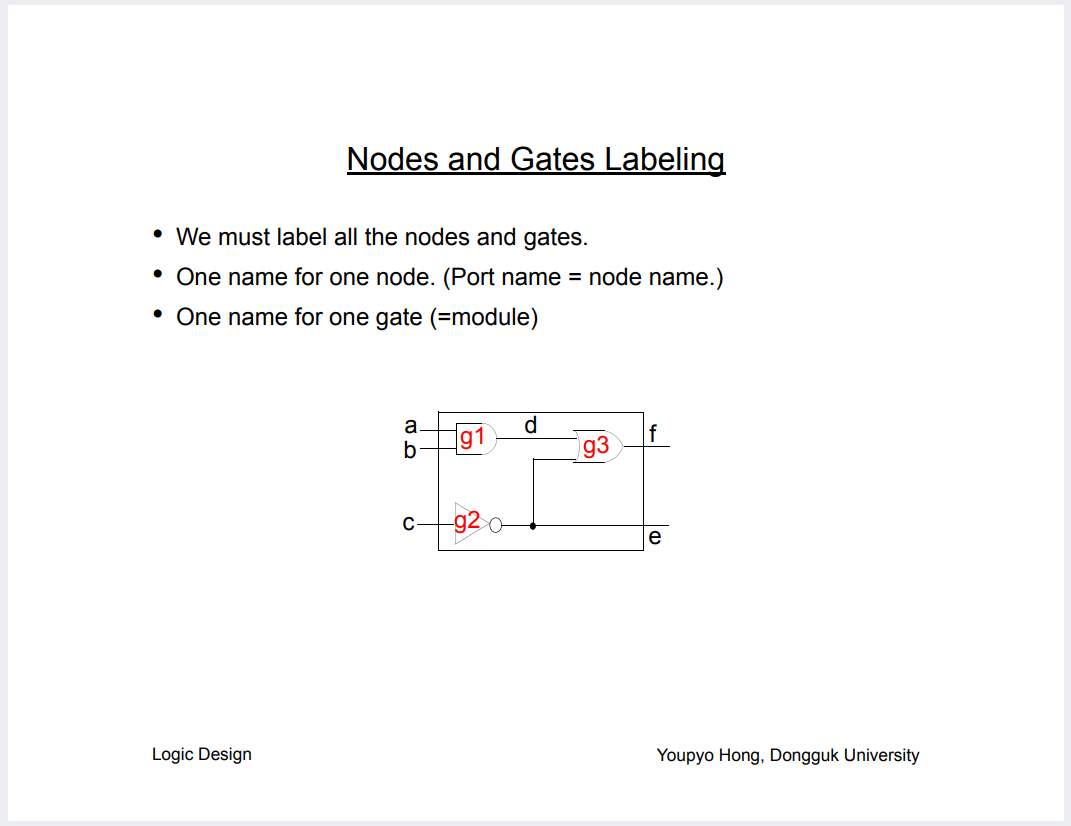

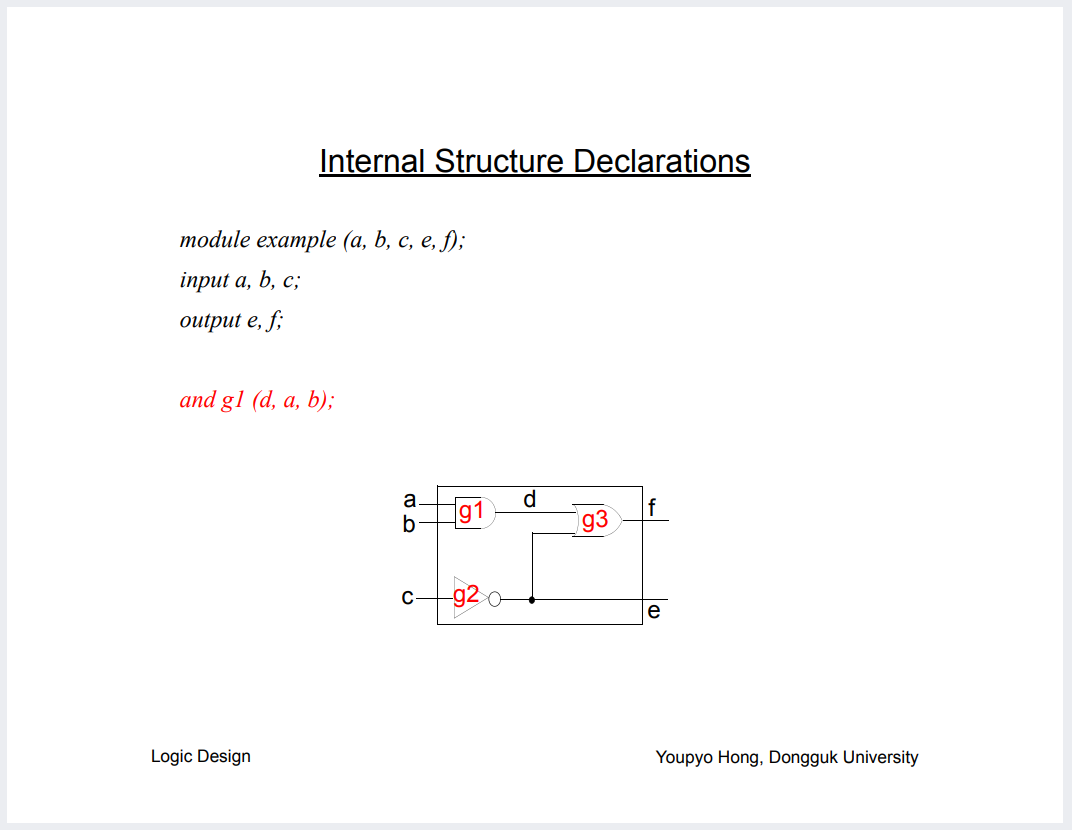

모듈과 커넥션에 초점을 맞춤

문법 및 컨벤션은 다음과 같음

자 그래 코드에게 회로를 이해시켰으면, 이걸로 뭘 할건데?

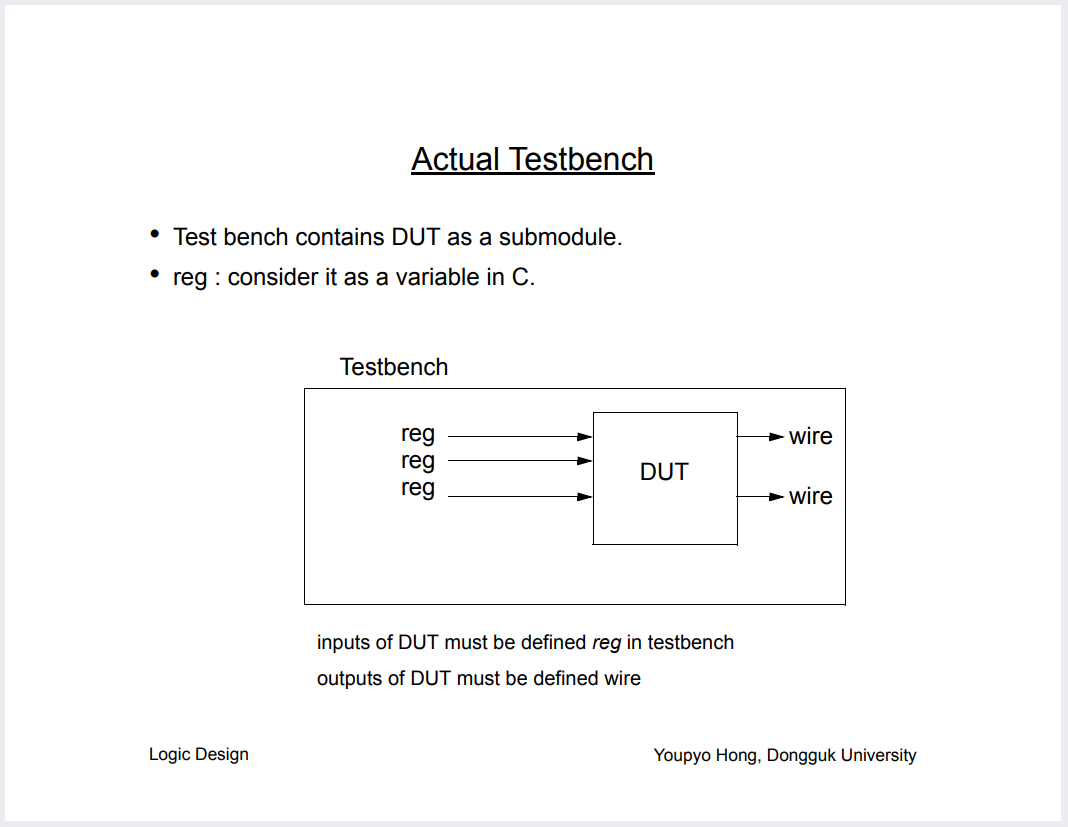

DUT는 Test를 받게될 Circuit 및 Code를 의미하고

Testbench는 DUT가 올바르게 작동하는지 확인하기 위한 test pattern module 이다.

Testbench 안에 DUT가 서브모듈로 들어가고

reg를 input에 wire를 output에 꽂아준다.

그리고 이것을 vivado를 통해 simulation 해서 waveform을 관찰하여, 원하는 결과가 나오는지 확인한다.

Lecture 2 : Verilog Coding of a Full Adder

Full Adder의 DUT를 만들어서 Waveform까지 관찰하시오.

Lecture 3 : Verilog Behavioral Coding & Testbench

근데 우리가 지금까지 짠 방식은, HDL 하게, Structural 하게 작성한 것. 앞으로는 Behavioral 하게 작성.

그래서 4-bit adder를 2방식으로 프로그래밍 해보고 비교해보아라.

'Engineering(SoC Design) > Verilog' 카테고리의 다른 글

| [복습] FSM - Coffee Machine (0) | 2022.03.13 |

|---|---|

| 과거 실습과제 복습 (0) | 2022.03.13 |

| Register With Parallel Load 과제 (0) | 2022.03.13 |

| 블로그 설계독학-맛비 (0) | 2022.03.06 |

| github, verilog category (0) | 2022.03.05 |