Reference C

9.3 Golden Reference Models

TestBencher Pro and Reactive Test Bench Help

www.syncad.com

delay 하던 부분에 대하여

mul core로 대체함

어려운건 data를 이동시키는 과정이며

과정 전체에서 data mover의 내용을 가장 잘 장악해야한다.

곱셈같은 경우는

합성 단계에서 알아서 잘 처리해주기 때문에

굳이 low level로 낮출 필요는 없다.

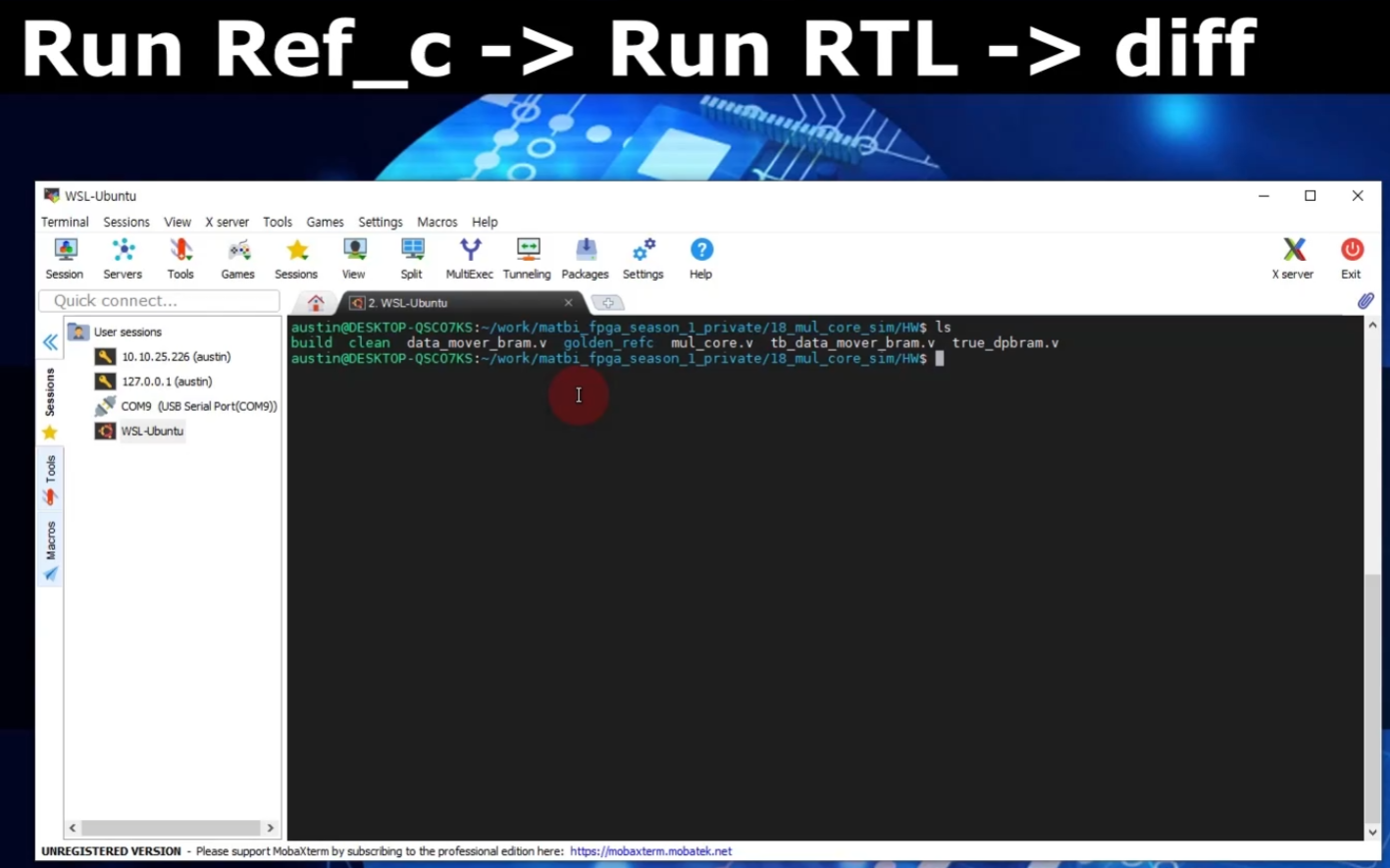

c를 먼저 실행하는 workflow로 진행된다.

make를 통한 실행

argument까지 넘겨주면 실행이 된다.

vim editor

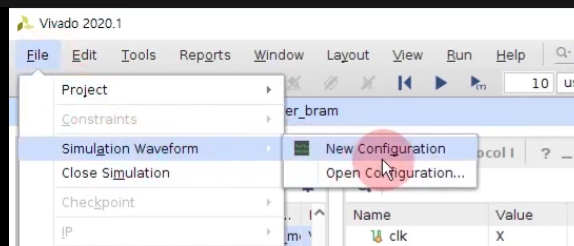

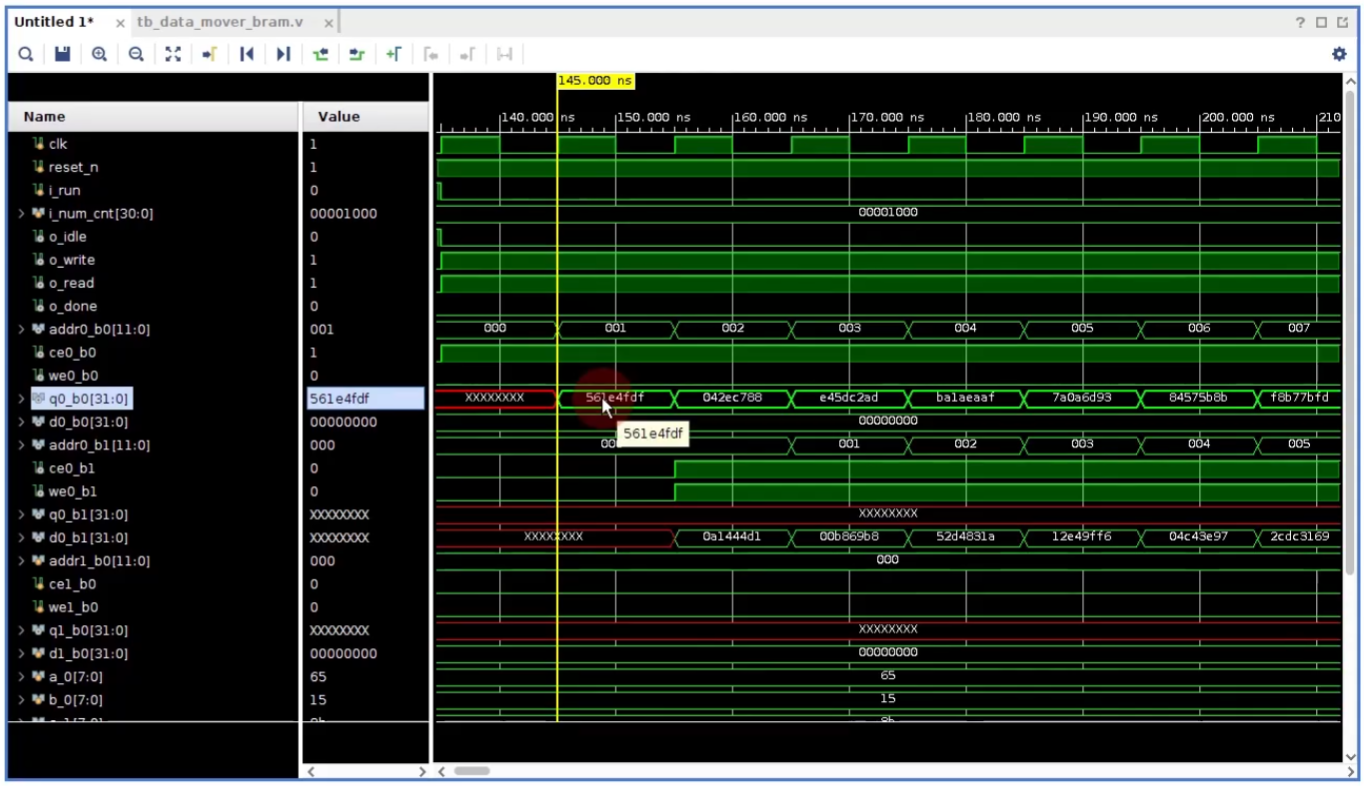

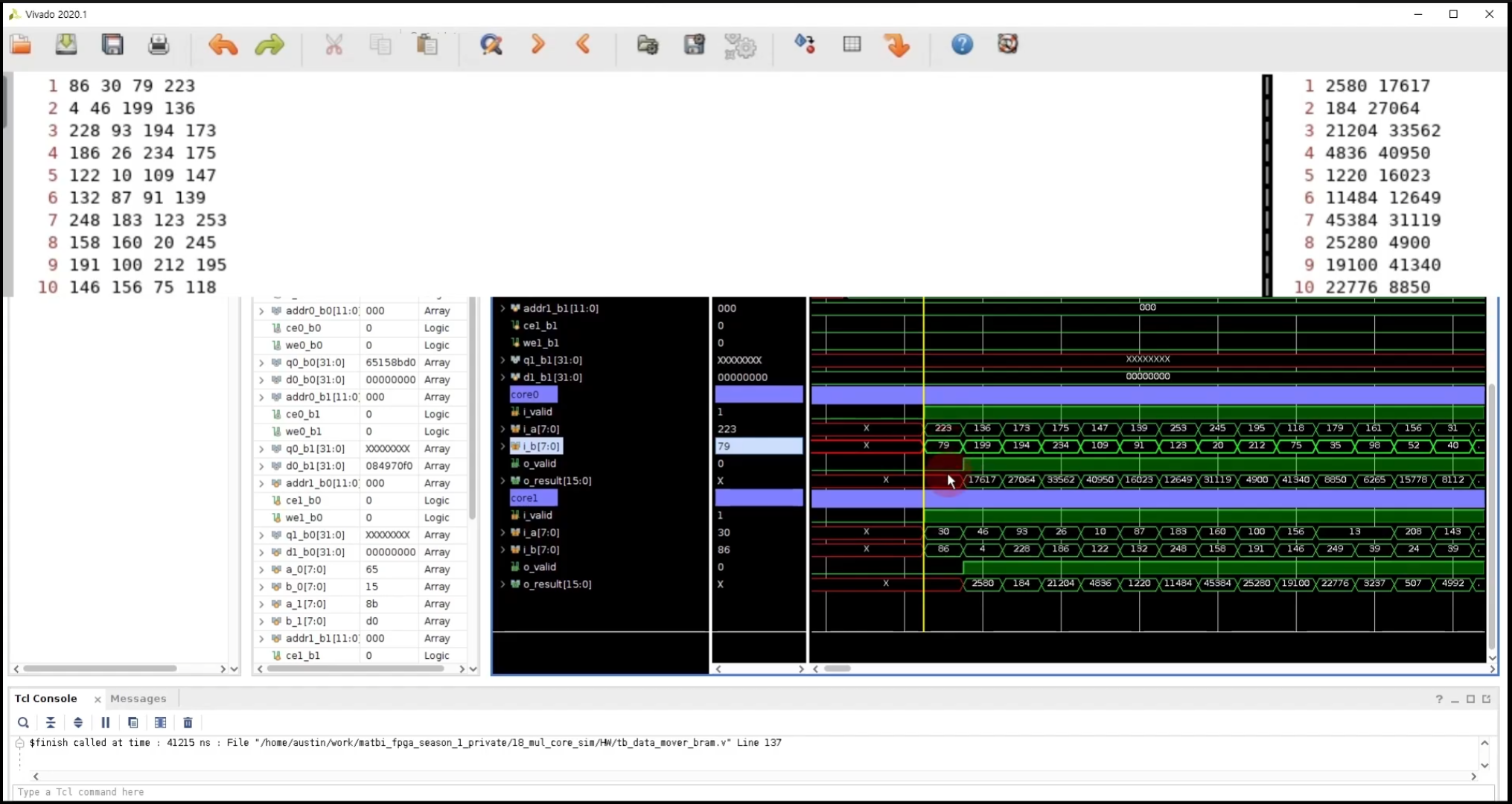

그리고나서 waveform을 보자

조금 더 잘 보기 위하여

이 값은 결과값의 concatenation

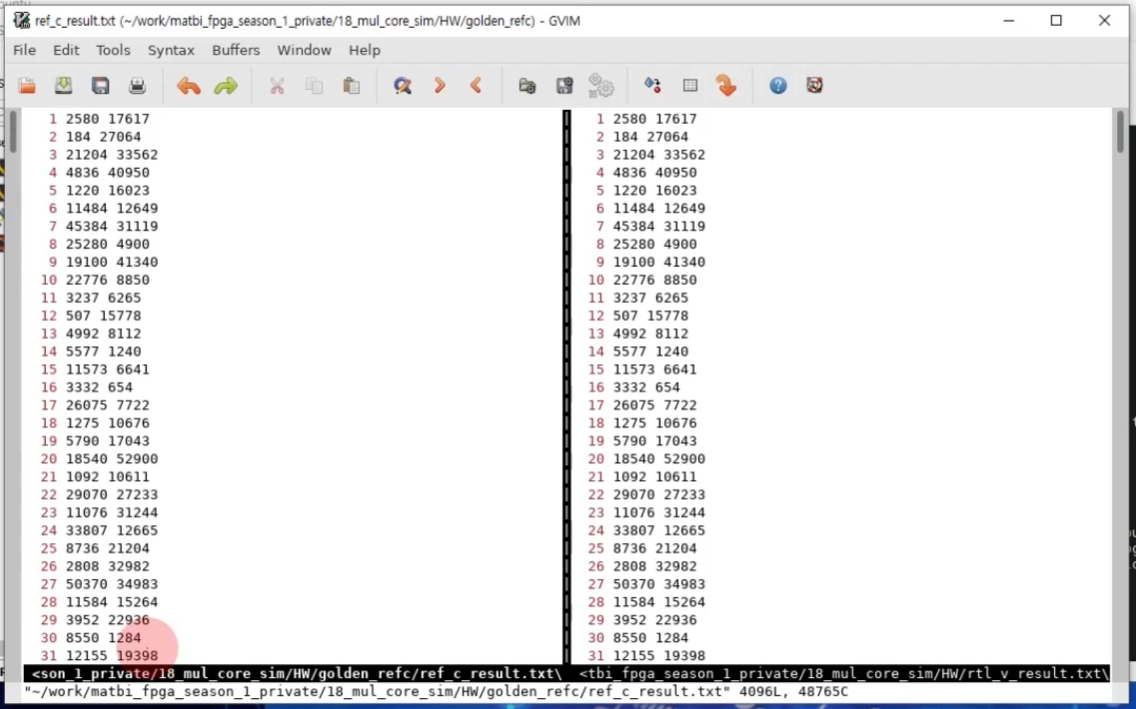

결과확인

이 두개의 파일을 수동 비교하기 위해서는

diff 기능을 통해서 비교할 수 있다. 텍스트 에디터 상에서.

또는 linux 명령어중에 diff 기능을 통해서 비교를 할수도 있다.

'적극적 생각 > FPGA' 카테고리의 다른 글

| 0802 / Fully Connected Layer 가속기 Core 설계 (1) (0) | 2022.08.02 |

|---|---|

| 0802 / HW 가속기 설계 연습. 8b 곱셈 Core 설계 (2) (0) | 2022.08.02 |

| 0802 / HW Accelerator (가속기)설계 비밀? 우리가 HW 를 공부해야 하는 이유 (0) | 2022.08.02 |

| design_1_wrapper가 필요한 이유 (0) | 2022.07.31 |

| IPCore에서의 ILA를 사용하기 (0) | 2022.07.29 |