Lecture 8 : Intro to Combinational Blocks

앞으로 우린 다음 요소들을 logic blocks 단위로 design 하는 법을 다룰거다.

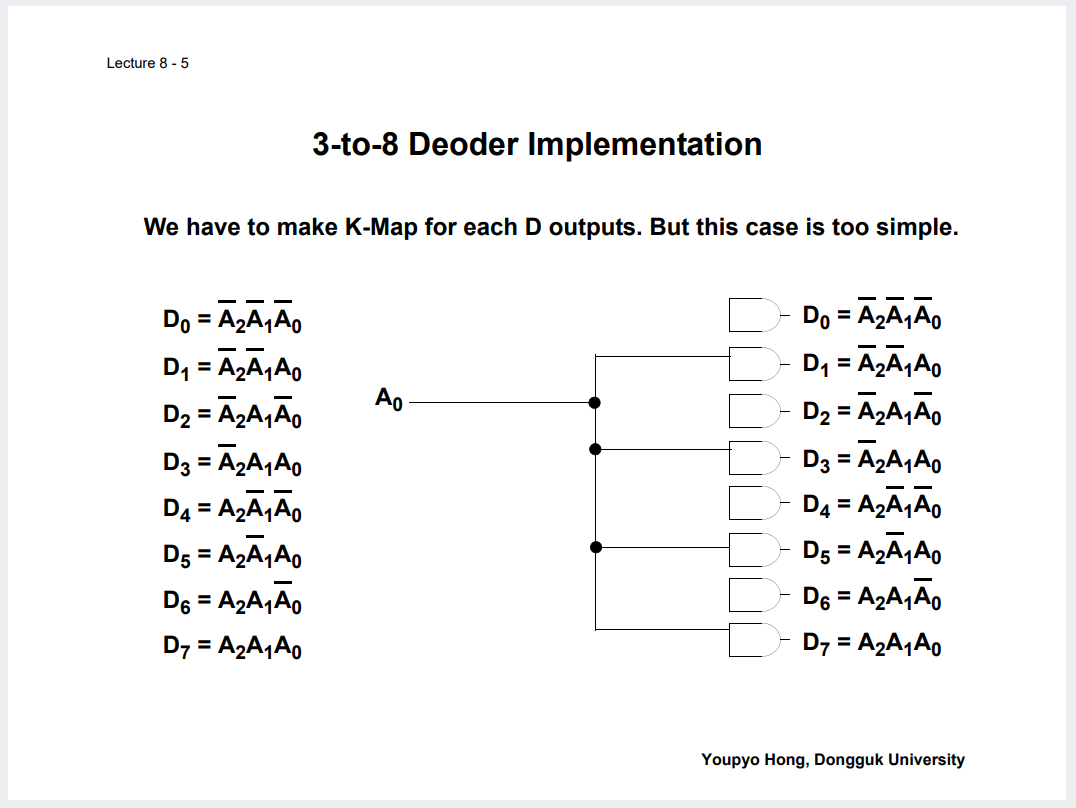

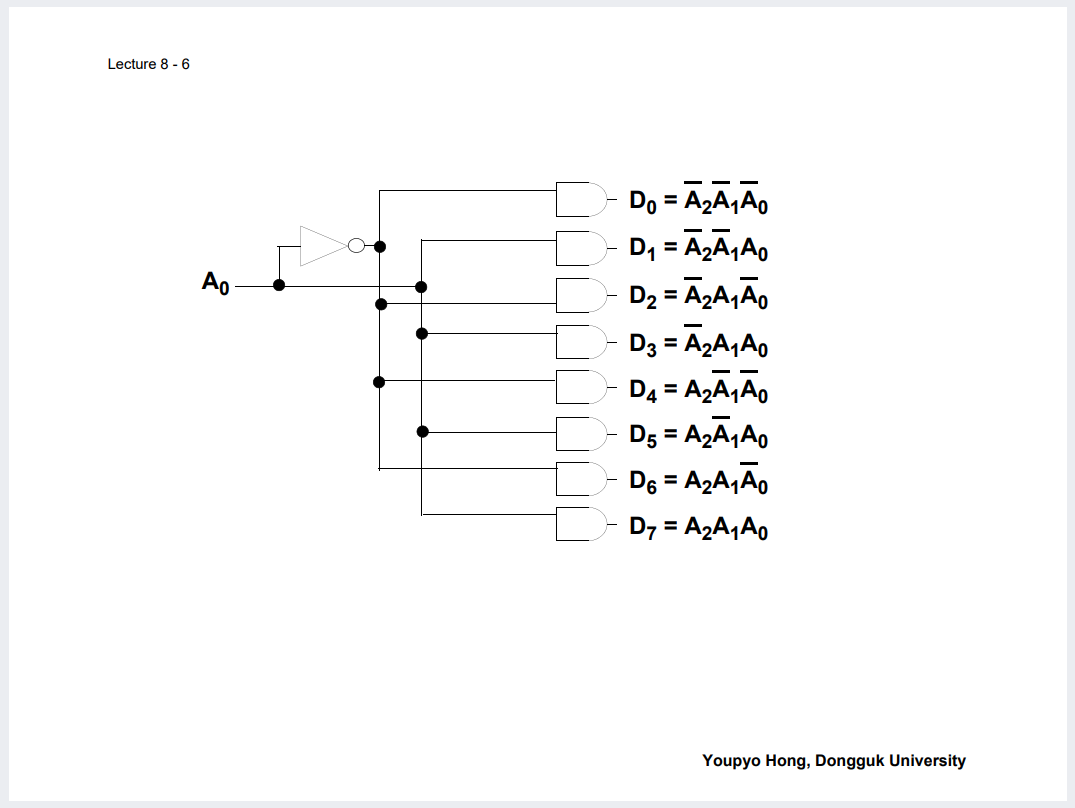

디코더는 인풋조합에 따른 결과값을 유니크하게 펼쳐주는 역할을 하는 소자며. 다음과 같이 그릴 수 있다.

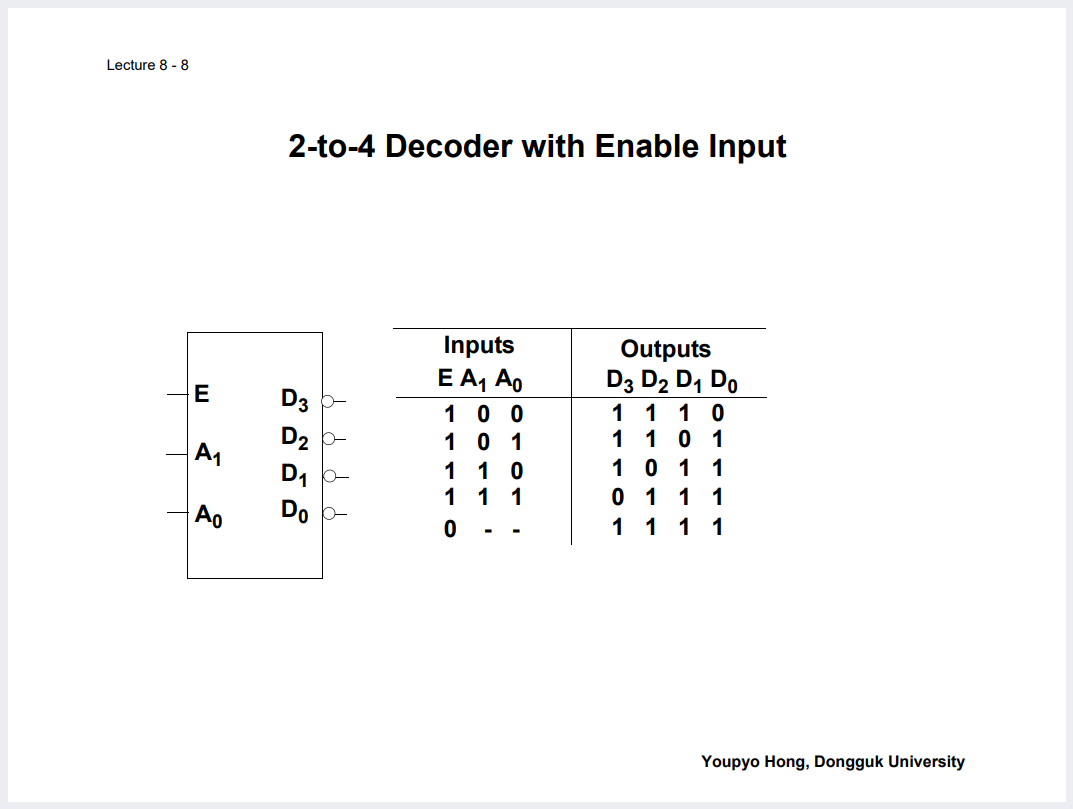

여기서 Decoder의 활성화 여부를 나타내는 Enable Input을 추가할 수 있다. (with EN)

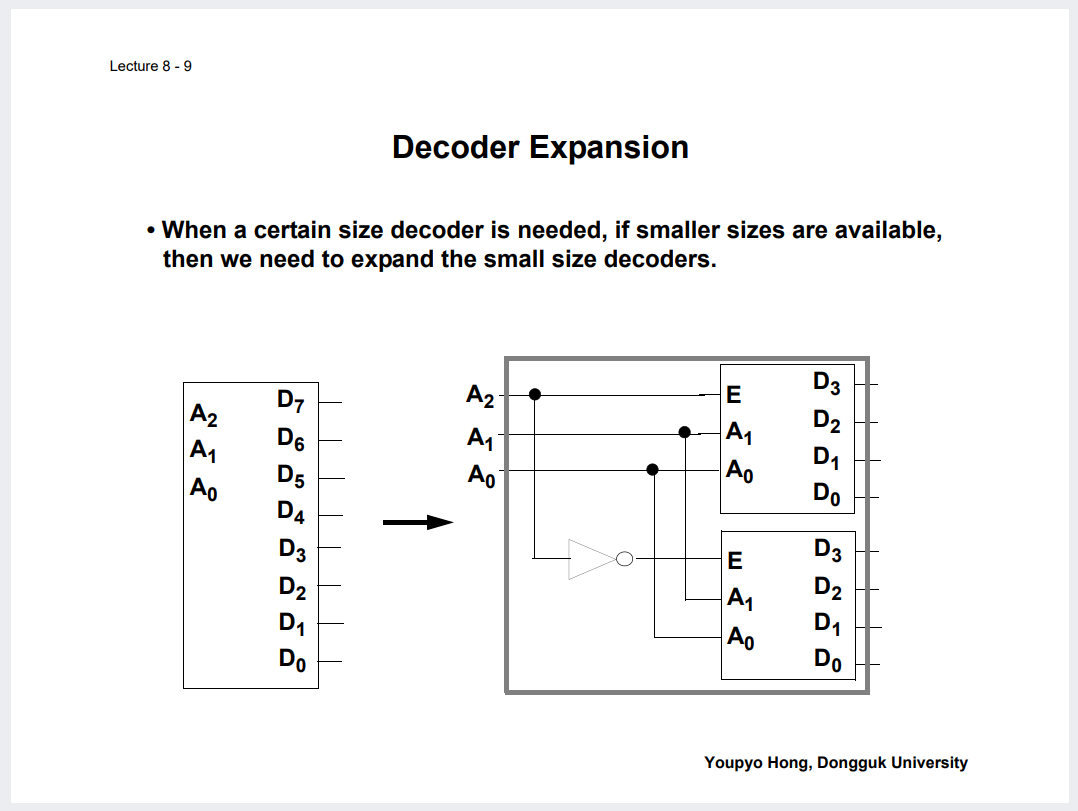

큰 디코더는 작은 디코더의 조합으로 나타낼 수도 있다. (Expansion)

Encoder는 Decoder와 반대 역할을 한다.

중요. 지금 참고로 내러티브에서 Encoder 그리는 것은 생략되어 있으니, 직접 확인해볼 수 있도록.

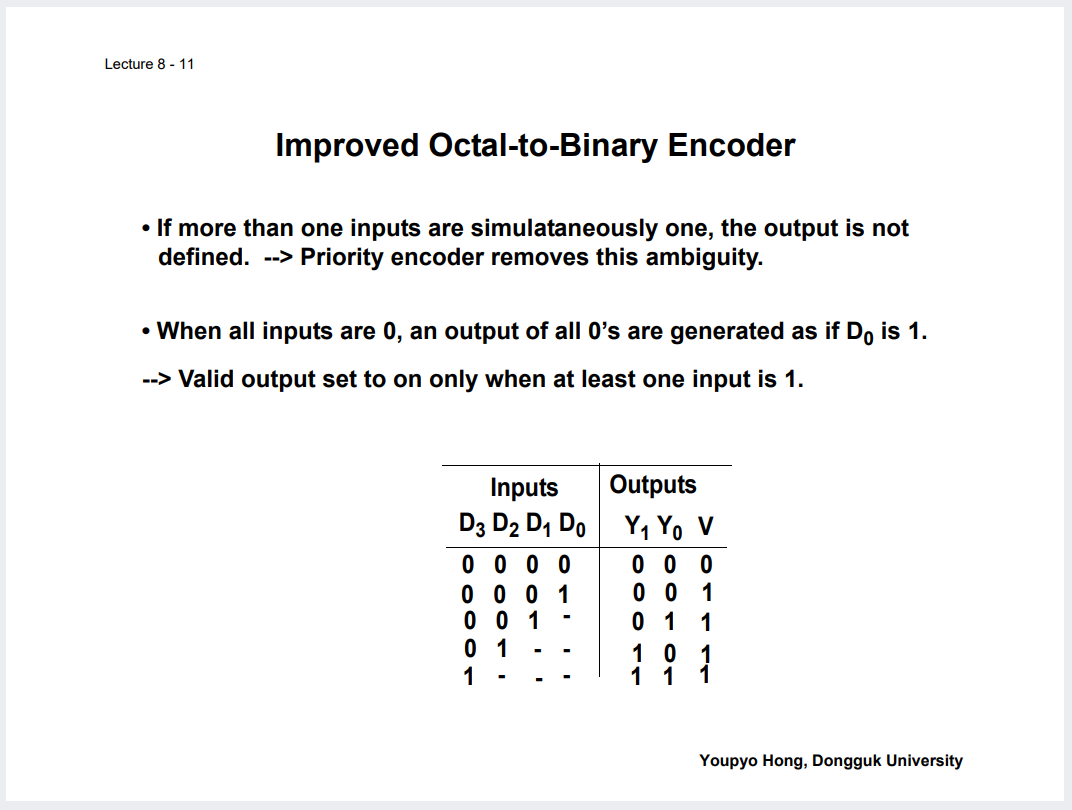

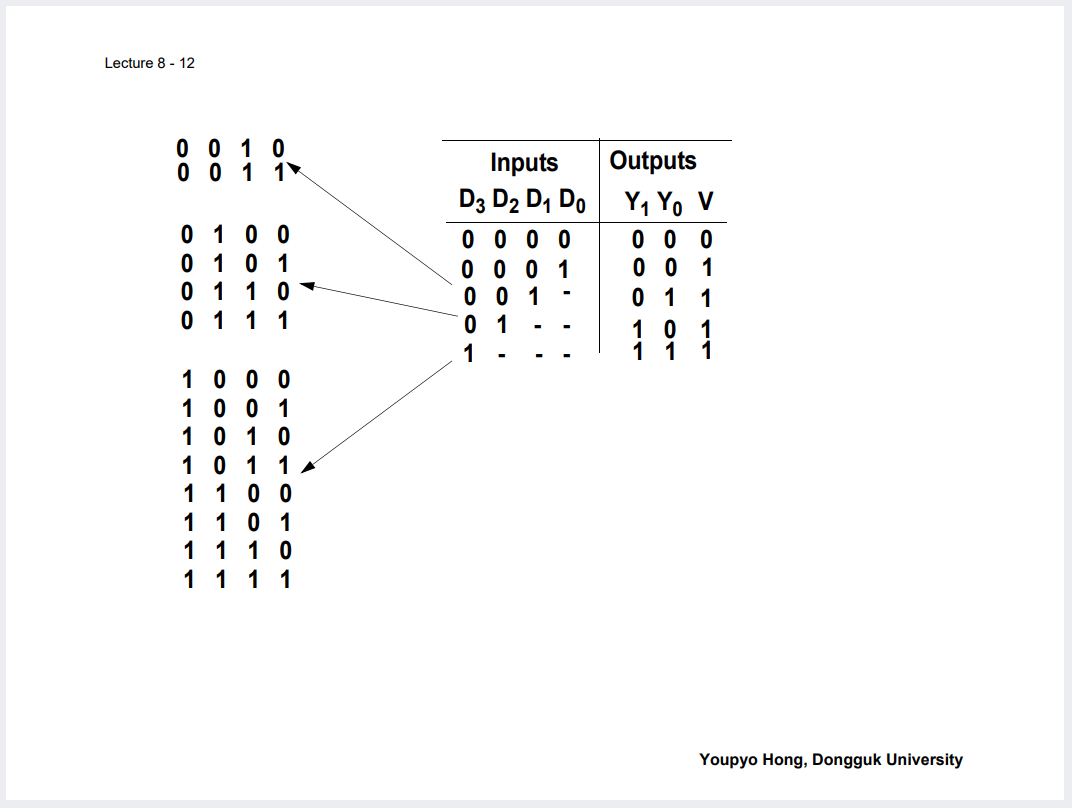

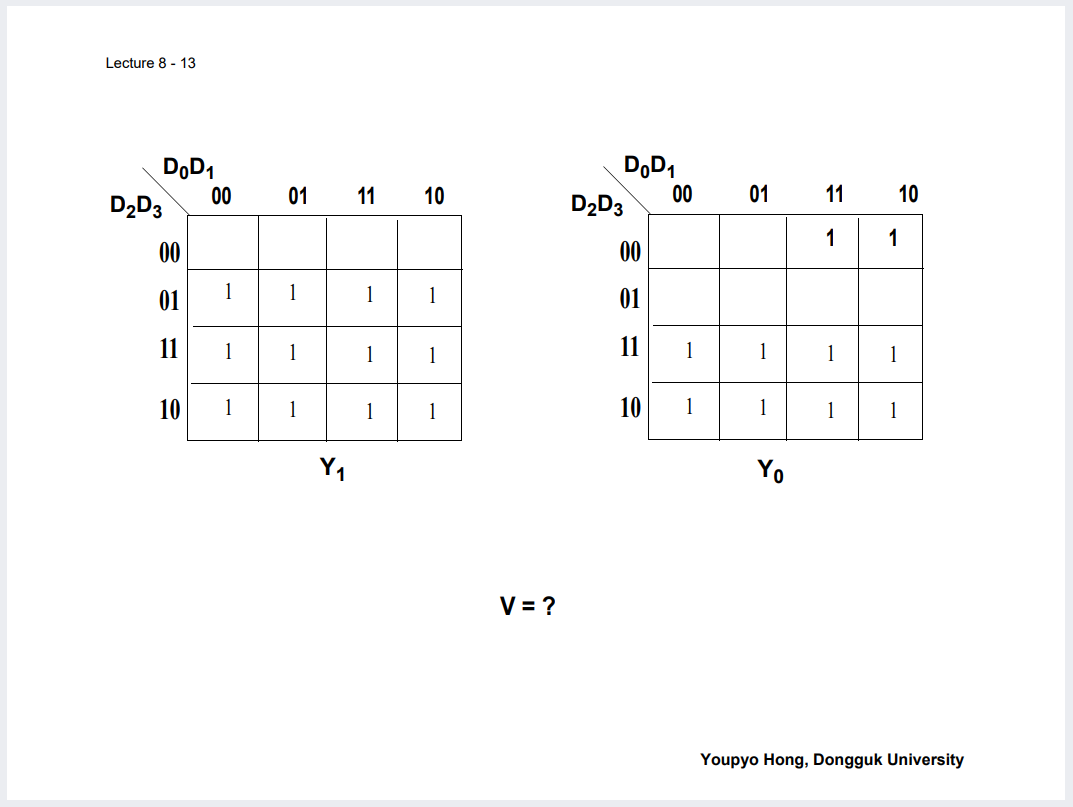

중요. don't cares와 V신호를 이용해서 다음과 같은 Improved Octal-to-Binary Encoder를 만들수도 있다.

Lecture 9 : Multiplexor and Demultiplexor

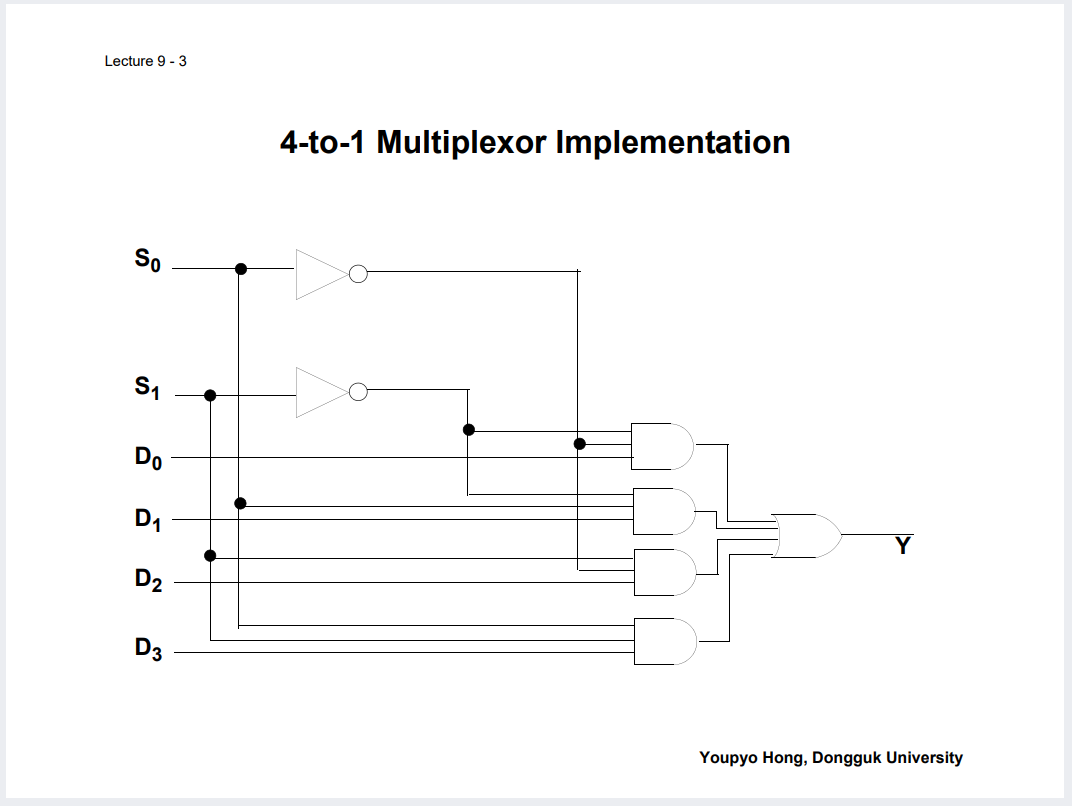

멀티플렉서는 Select 신호를 통해 Input Data를 Output Data로 제어해줄 수 있다.

Demux는 그 반대.

Lecture 10 : Adders

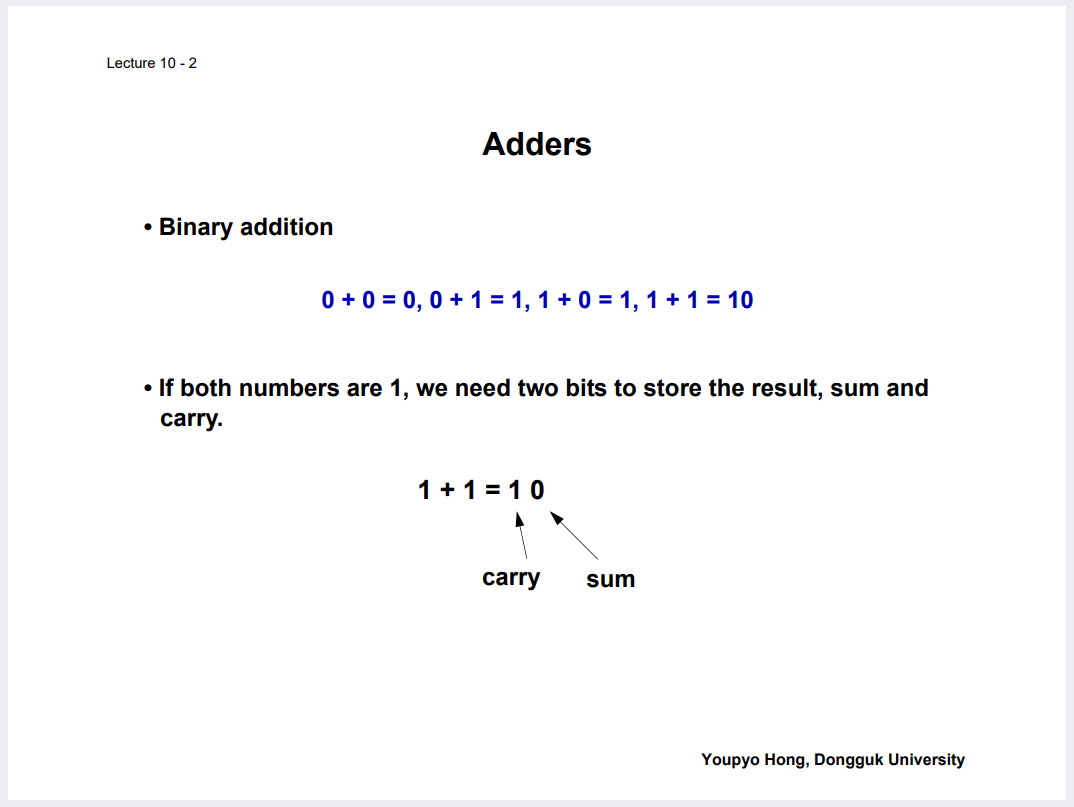

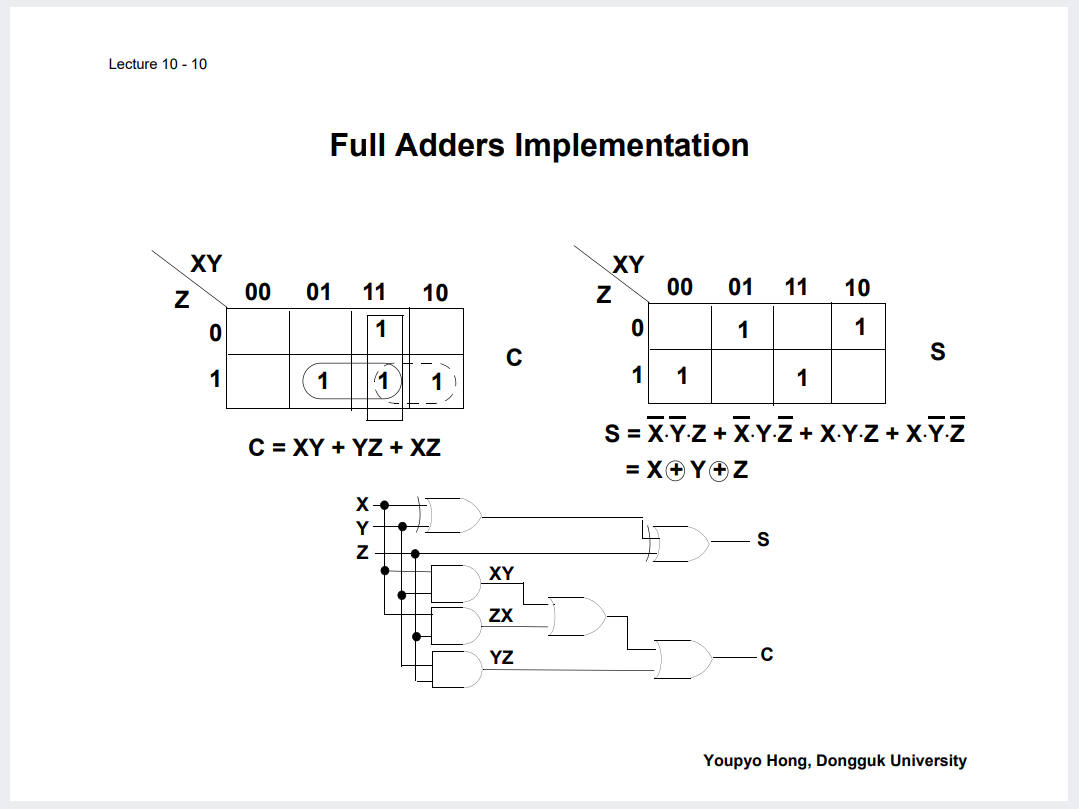

Binary Addition을 수행할 수 있는 회로이며, Carry와 Sum의 개념이 존재함.

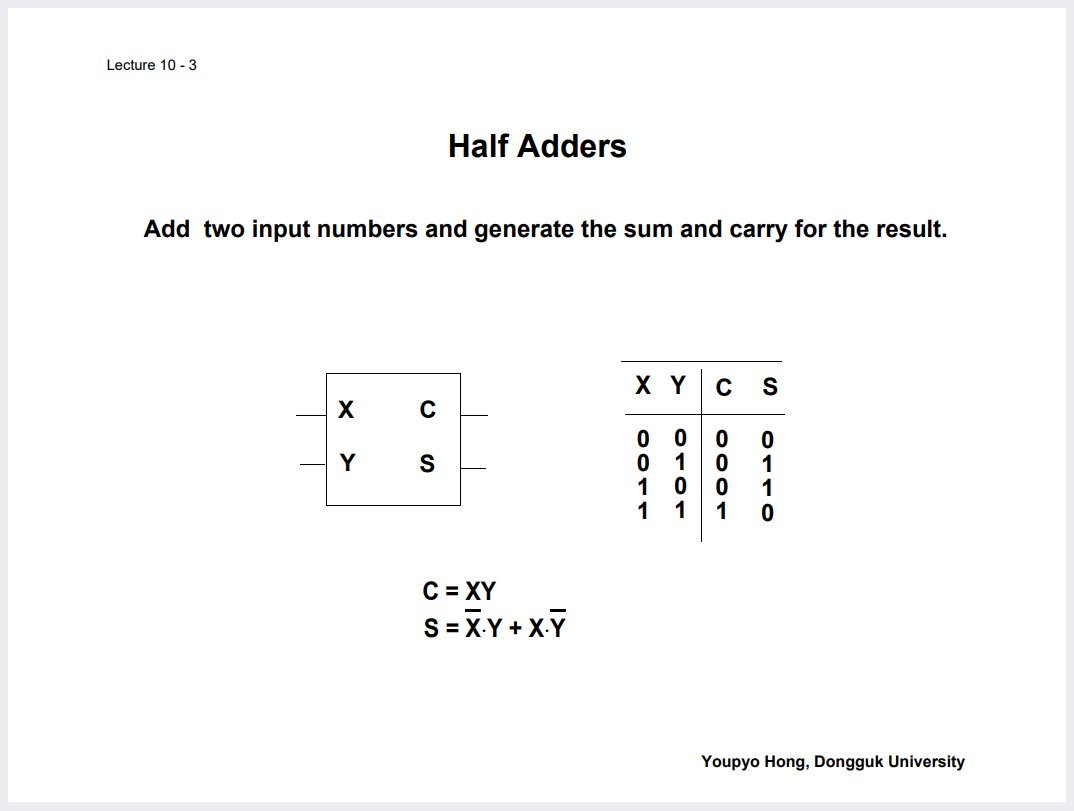

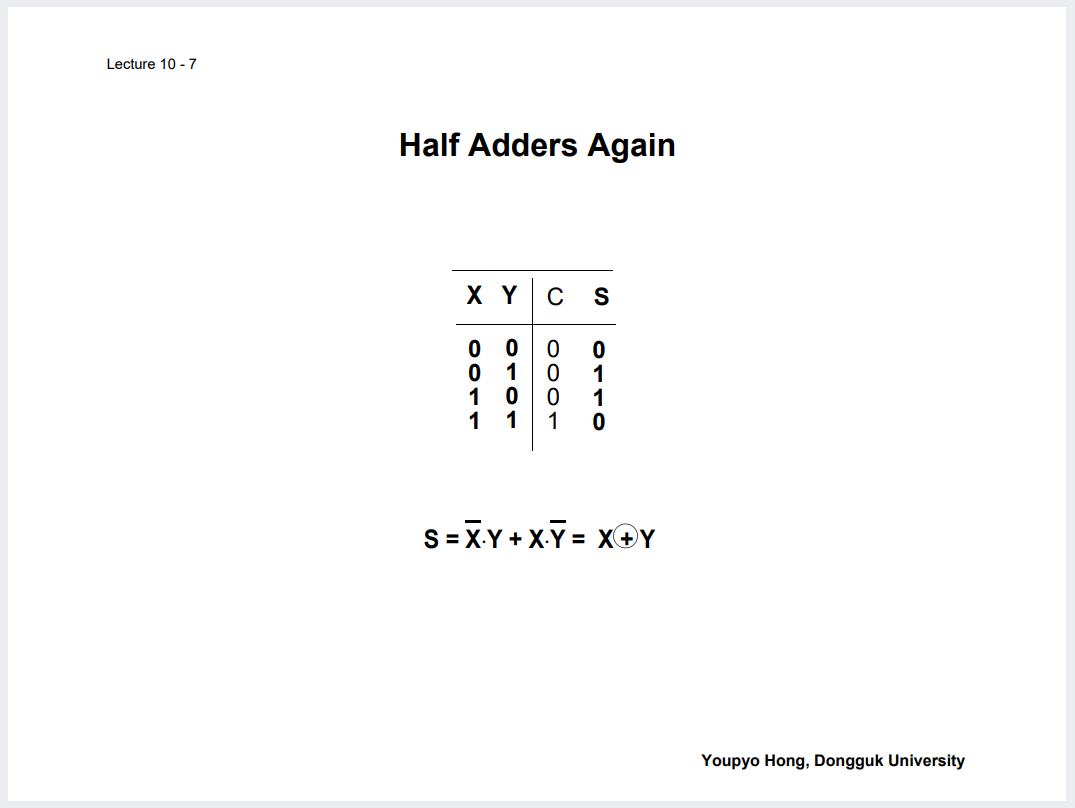

아주 간단하게 덧셈만 해주는 회로를 반가산기라고 부름.

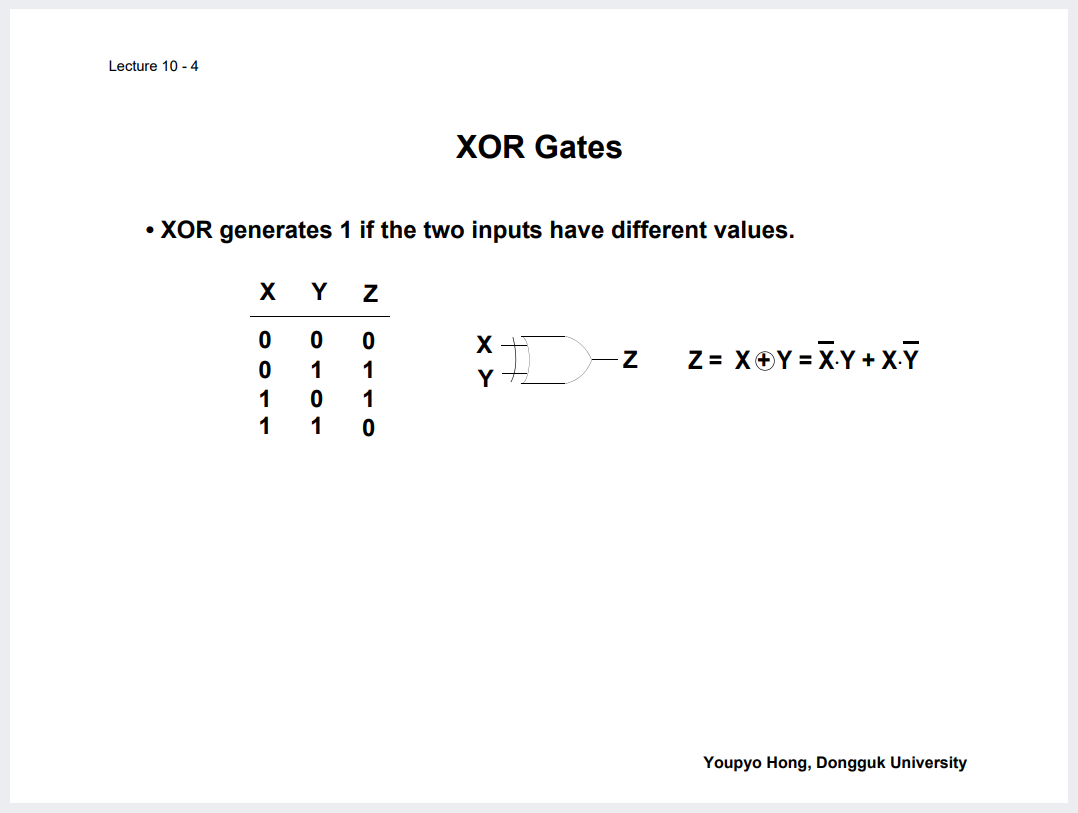

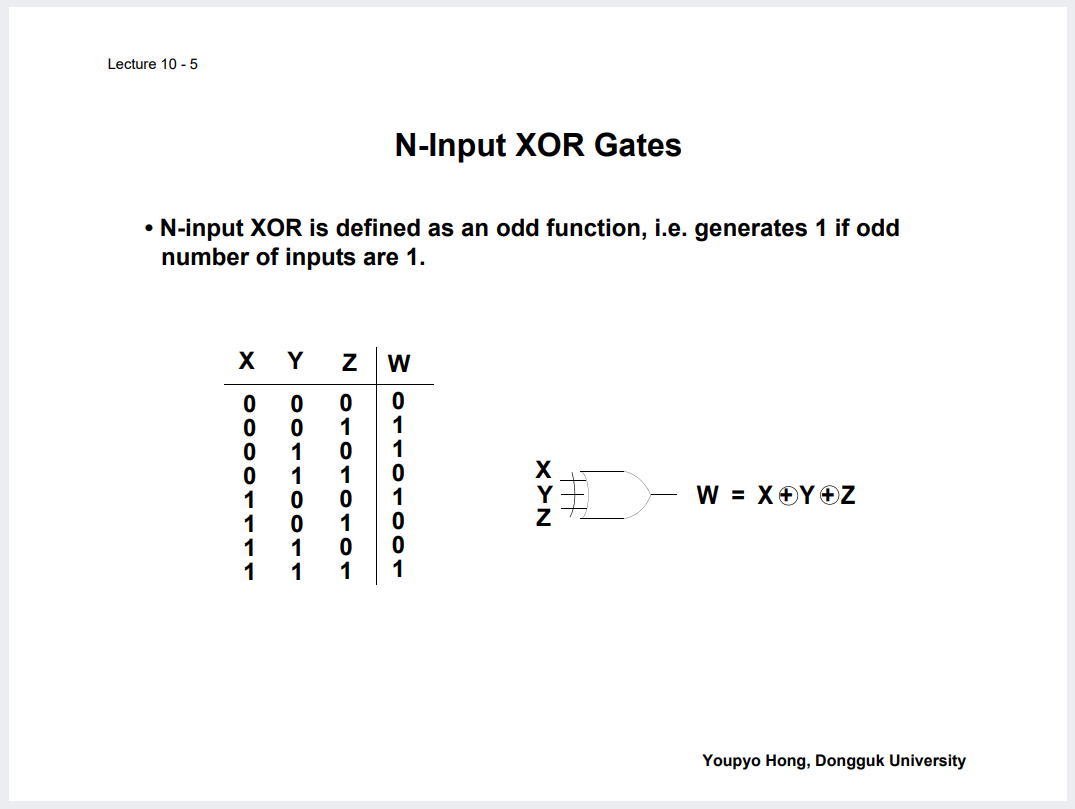

XOR는 '다르다'를 판별해주는 역할을 하며, 다음과 같이 구성된다. (odd function으로 볼수도 있다.)

(이것 또한 분해해서 그릴 수 있어야겠지?)

3 input gate는 다음과 같이 2 input gate로 분할 가능하다. (ex. 2-input gate로만 그리세요)

이걸 이용하면 반가산기를 줄일 수 있다.

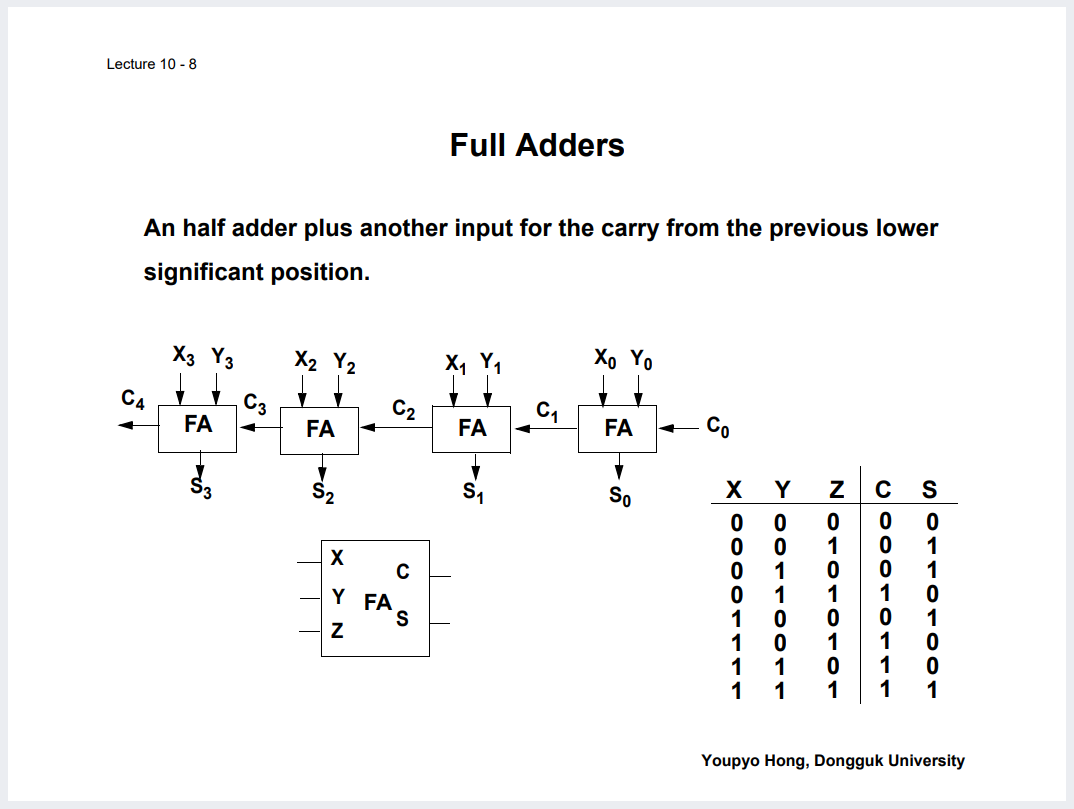

또한 여러 비트의 숫자를 더하기 위해서는

Carrying-in, out의 역할을 수행해줄 수 있는

꼬리물기(Output이 또다시 Input이 된다.) 역할을 수행해줄 수 있는 가산기가 필요하다.

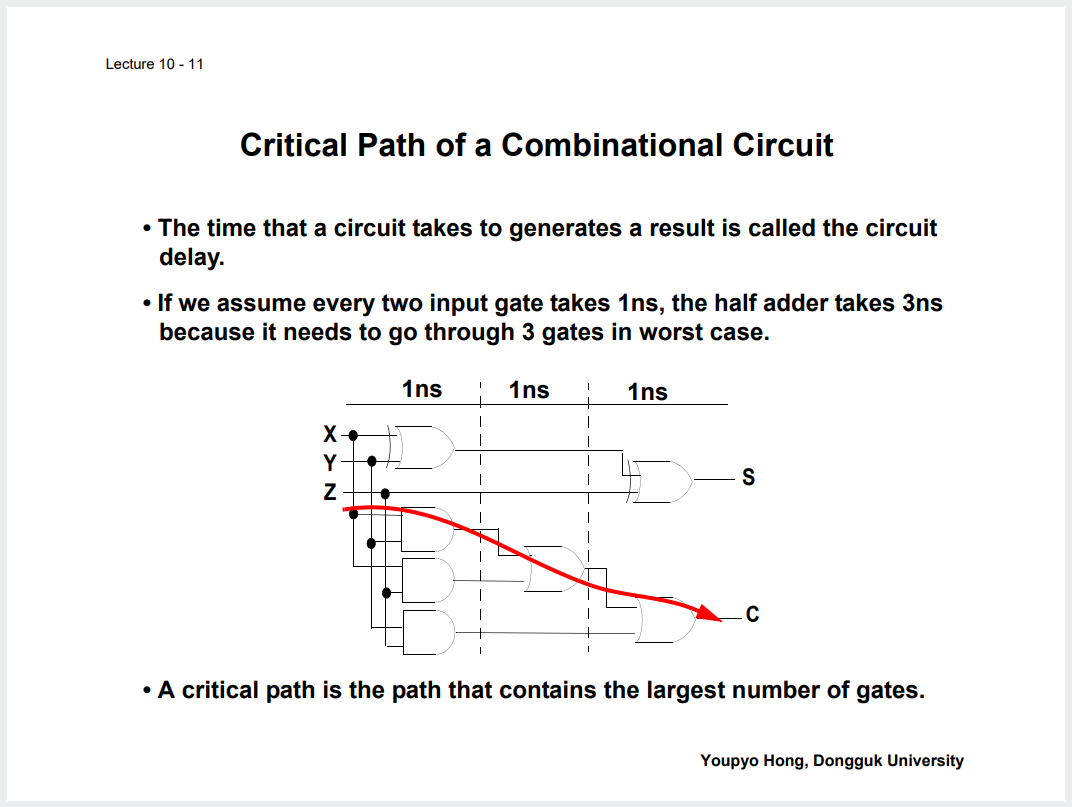

여기서 우리가 챙겨갈 수 있는 개념이, best case 와 worst case의 critical path를 파악할 수 있게 된다.

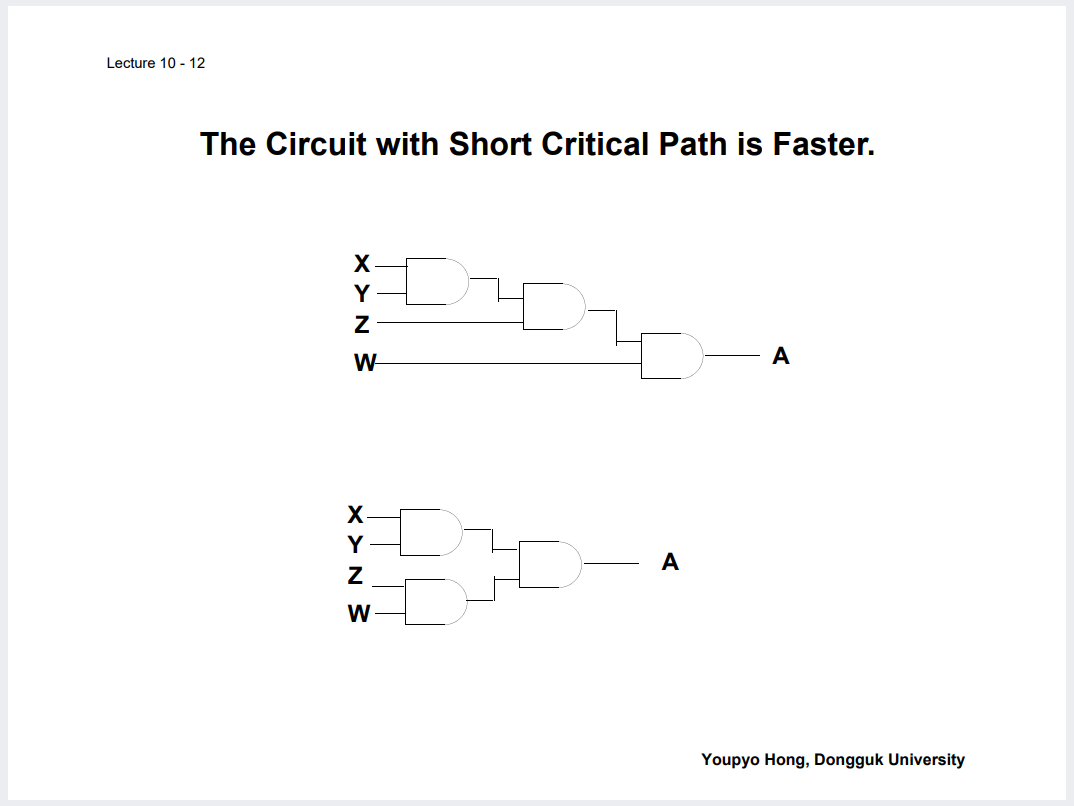

short path = faster, long path = slow & critical path.

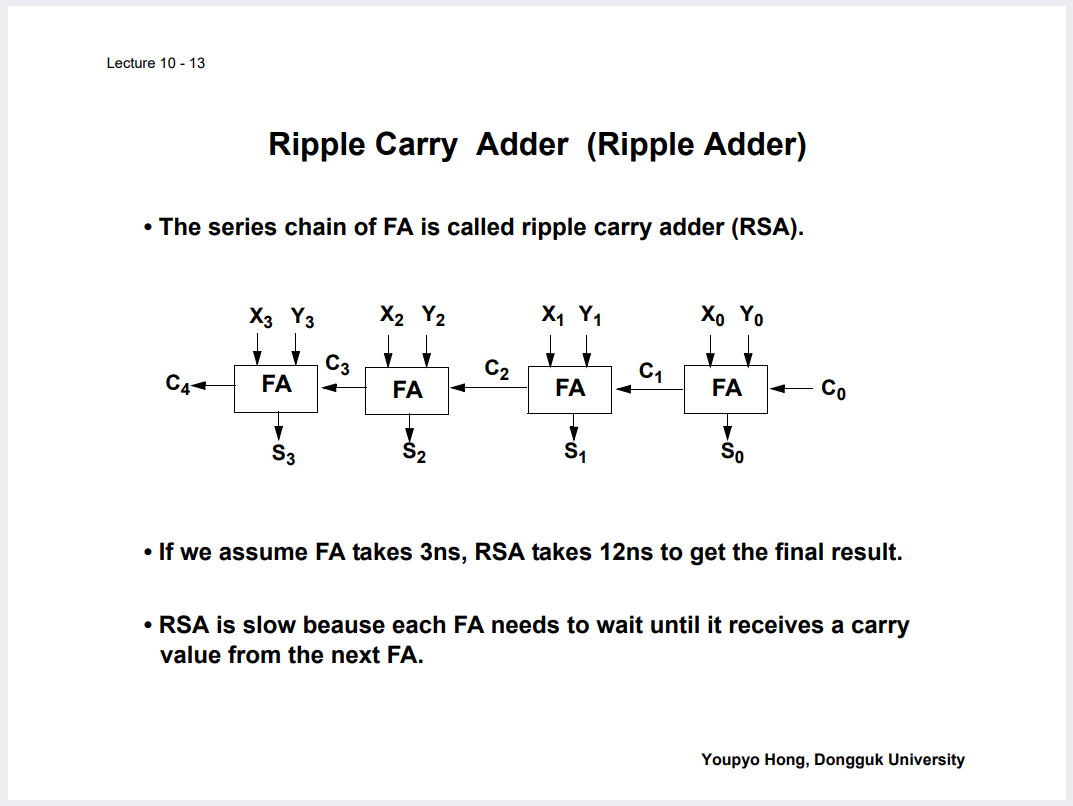

FA의 Serial chain은 RSA(Ripple Carry Adder)가 된다.

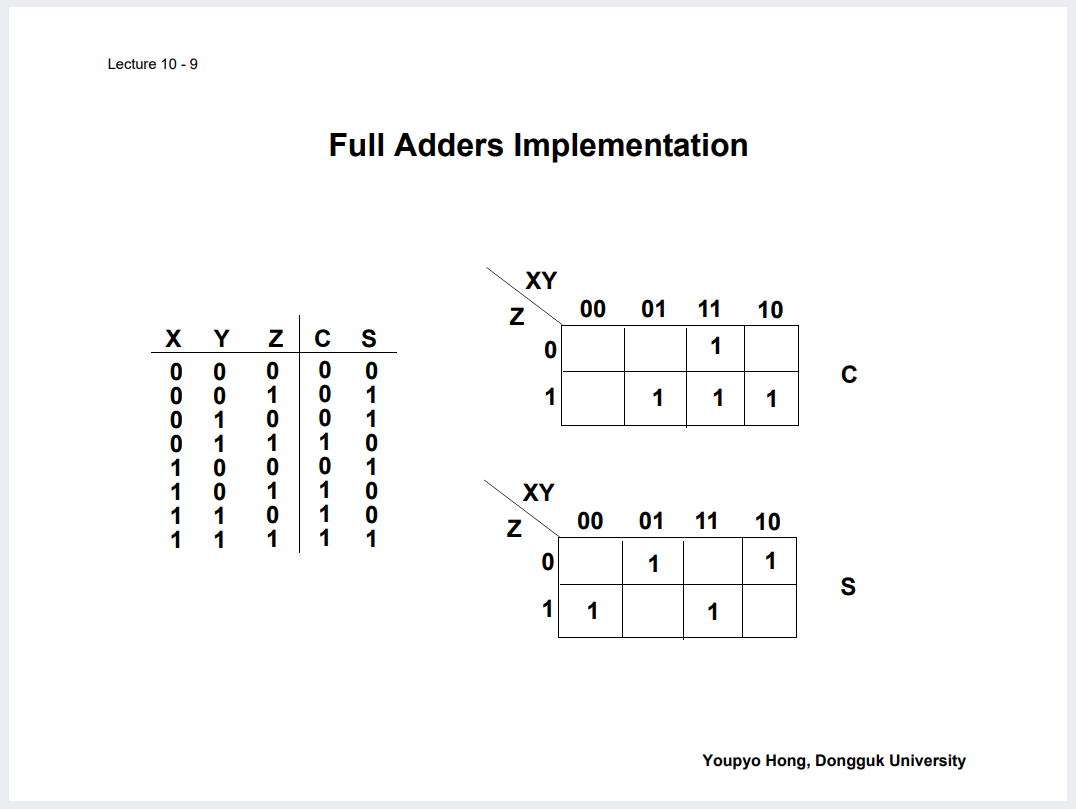

하지만 critical path 개념으로 보면, 꼬리의 꼬리를 문 셈이 되니, 엄청 느려지겠지.

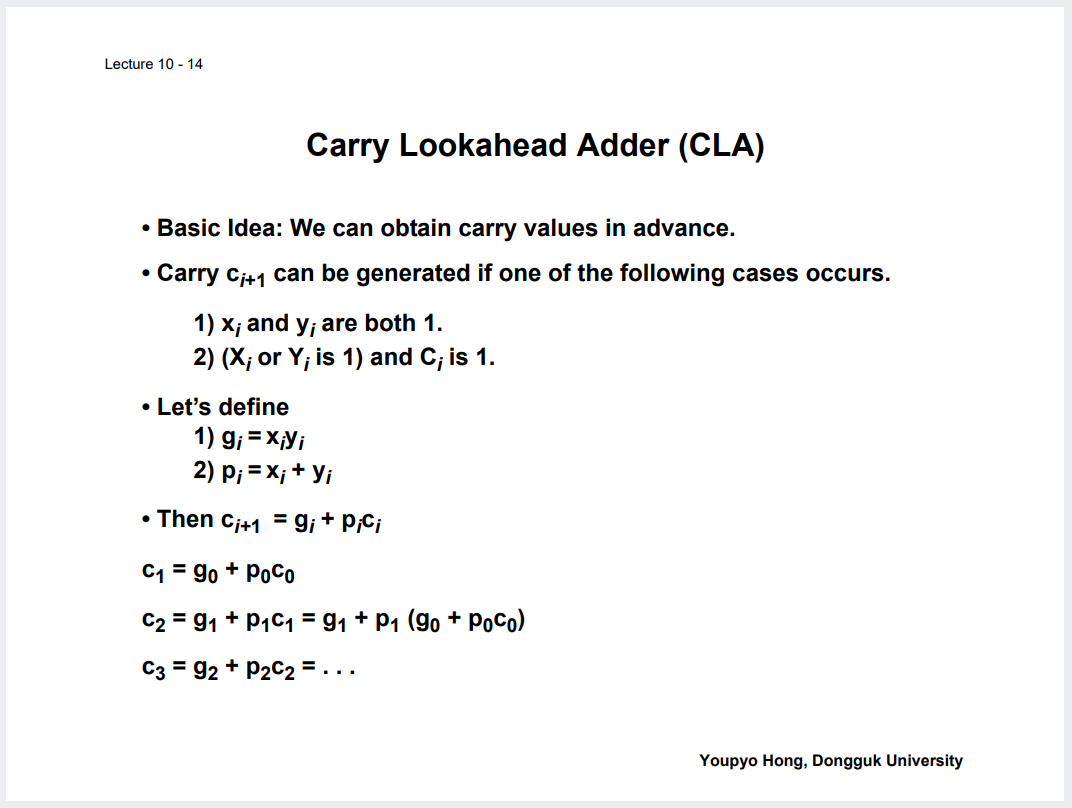

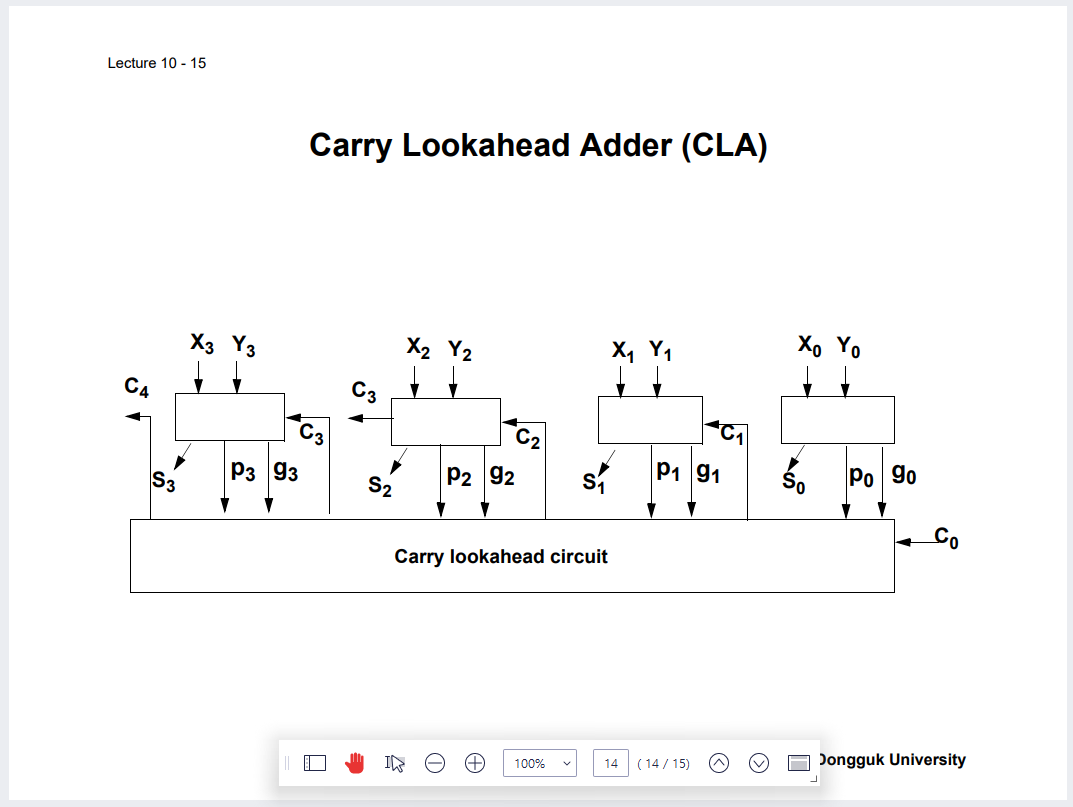

그래서 그 문제를 해결하기 위해 규칙성을 통해 Carry를 Lookahead 할 수 있는 CLA(Carry Lookahead Adder)가 존재.

이 수식과 논리를 어떻게 증명해내는지에 대해서는 다시 파악할 필요가 있다.

Lecture 11 : Subtractor and Multiplier

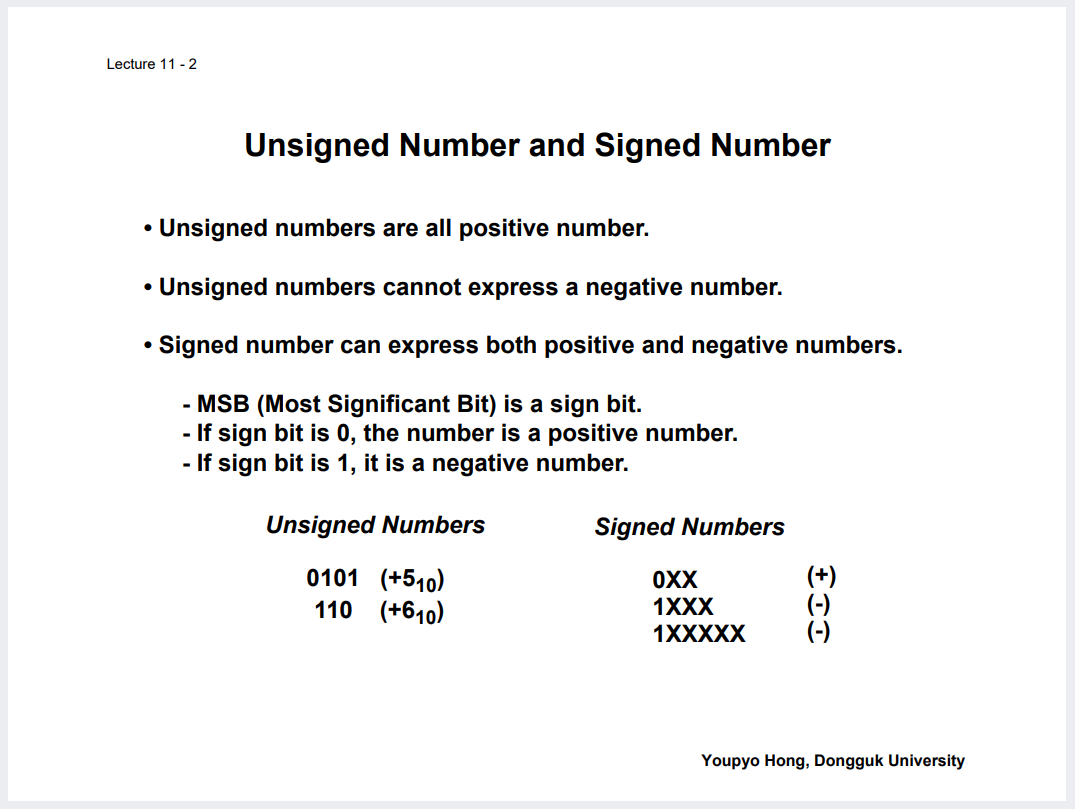

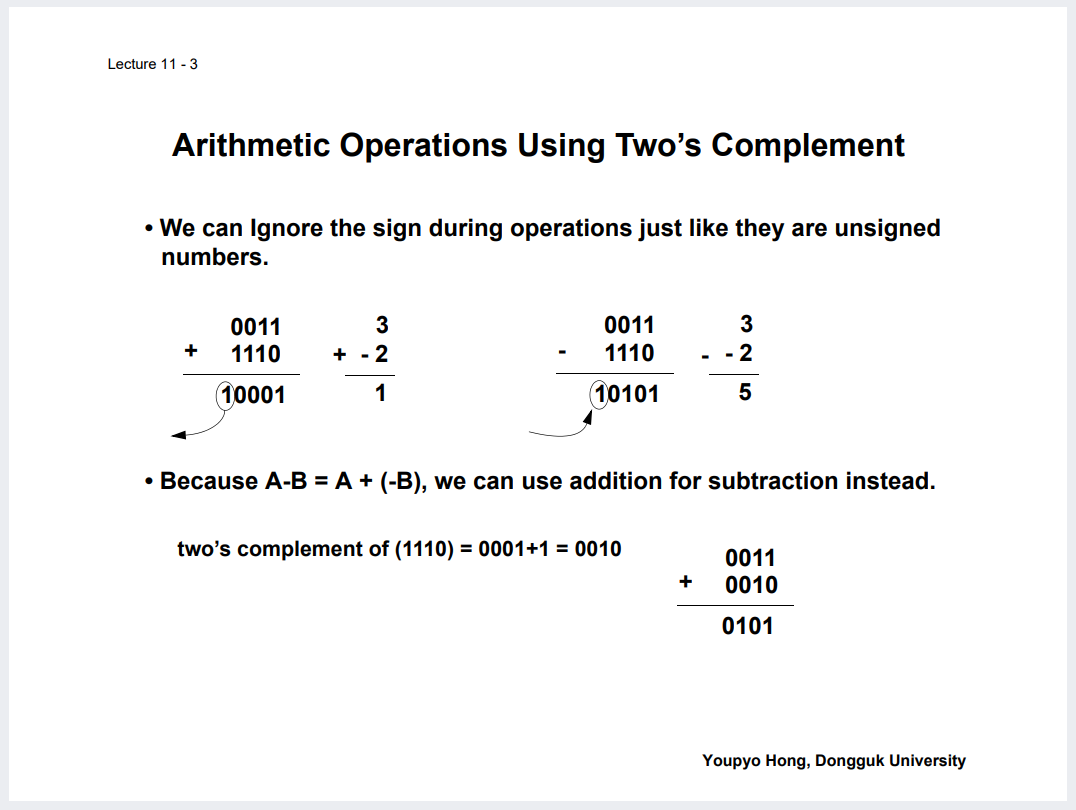

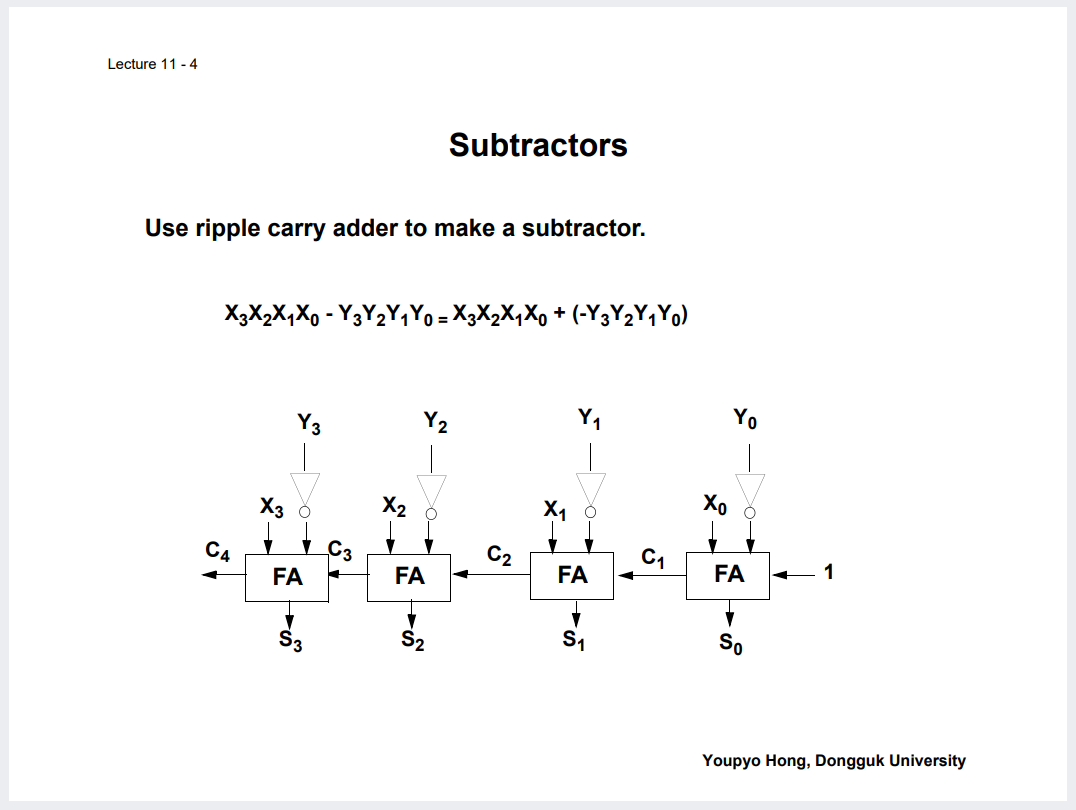

우리는 앞서 Number Systems에서 Binary Substract에 대해서 배웠다.

이 것을 응용하여 Substractor는 다음과 같이 응용구현이 가능하다.

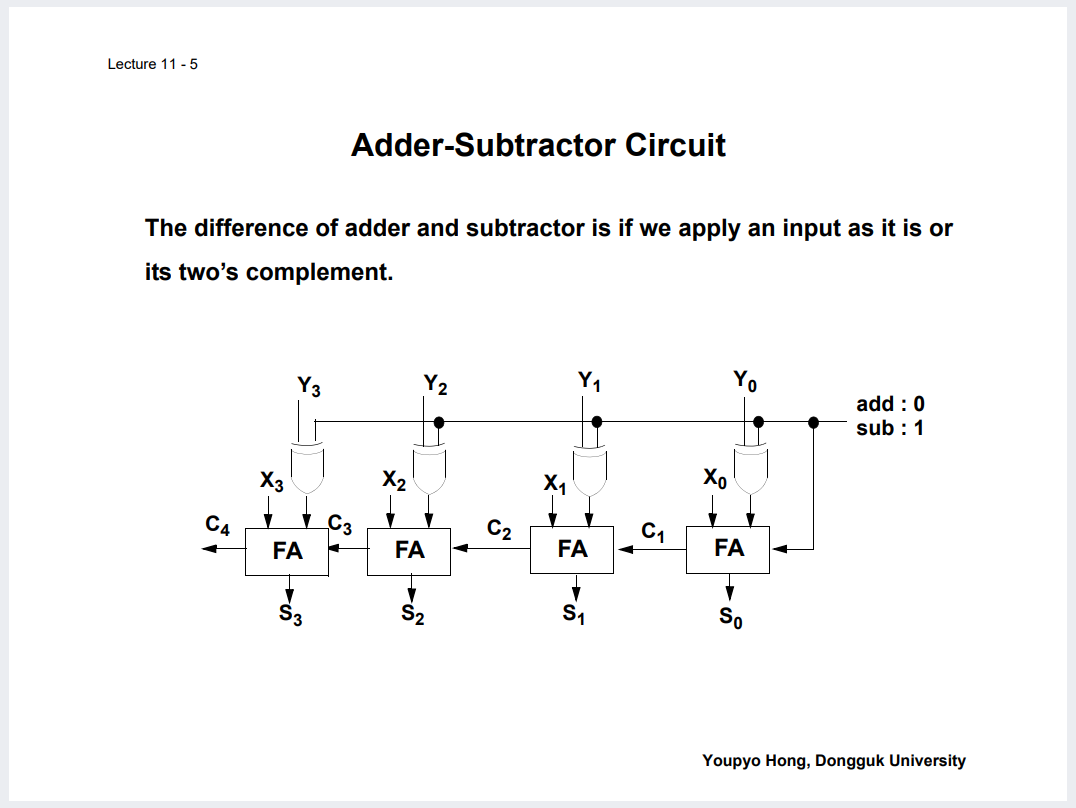

Controll signal을 도입하여 Adder와 Substracter를 모두 동작하게끔 할수도 있다.

또한 Multiplier같은 경우는 원리상, Adder의 조합 등을 이용해서 나타낼 수 있다.

(이 부분 증명하는 것도 팔로업)

'Engineering(SoC Design) > 디지털공학&논리회로설계' 카테고리의 다른 글

| 논리회로설계 (복습 10~12) (0) | 2022.03.11 |

|---|---|

| 논리회로설계 (복습 6~9) (0) | 2022.03.11 |

| 논리회로설계 (복습 2~5) (0) | 2022.03.11 |

| 디지털공학 (복습 4~7) (0) | 2022.03.11 |

| 디지털공학 (복습 1~3) (0) | 2022.03.11 |