Lecture6 : Counters

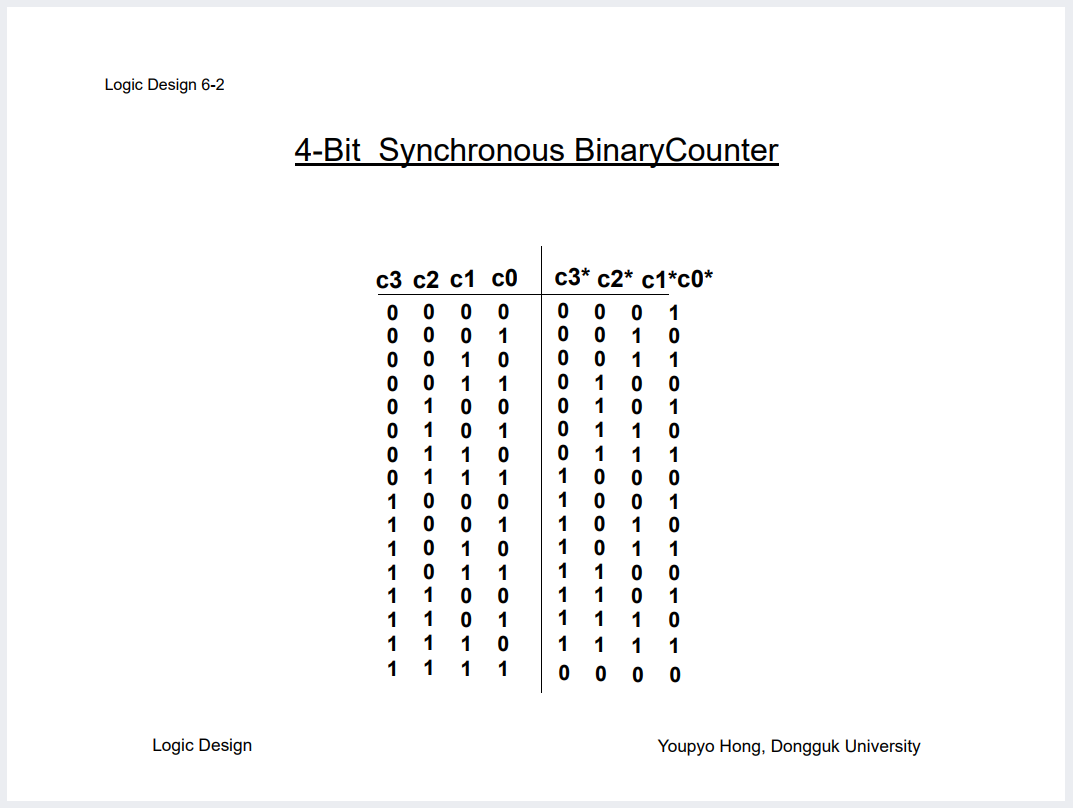

지금까지 배운 FF와 달리, Counter는 이런 성질을 갖는다.

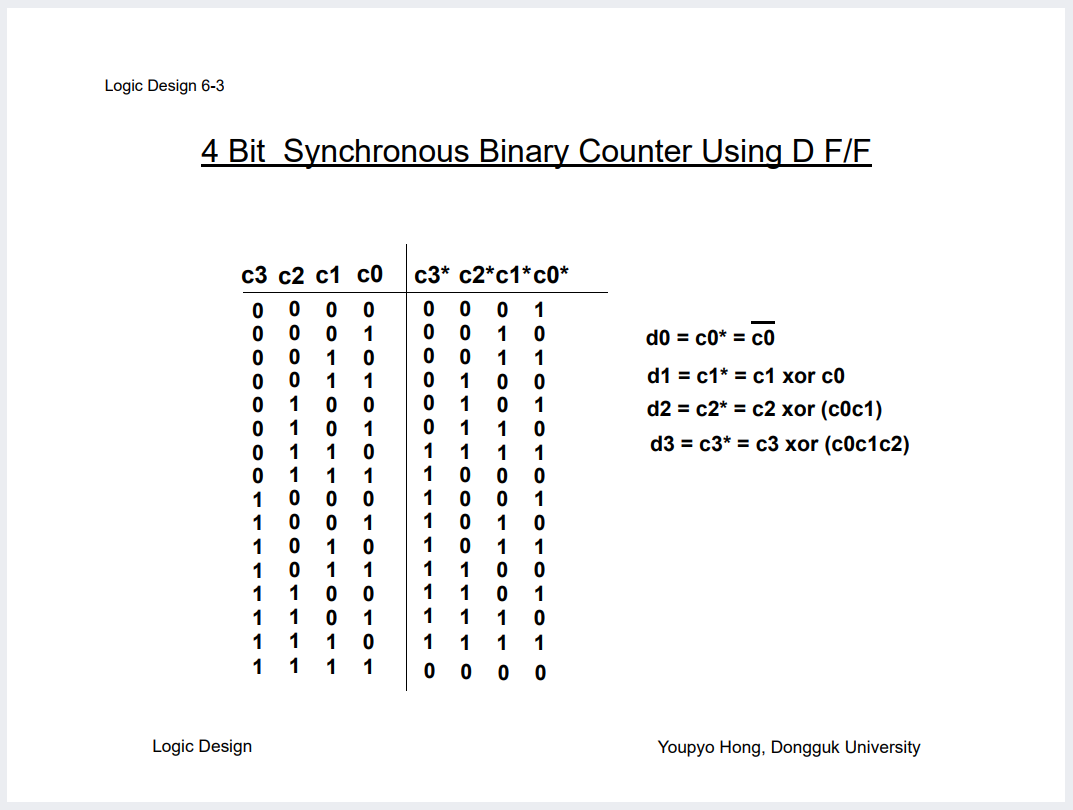

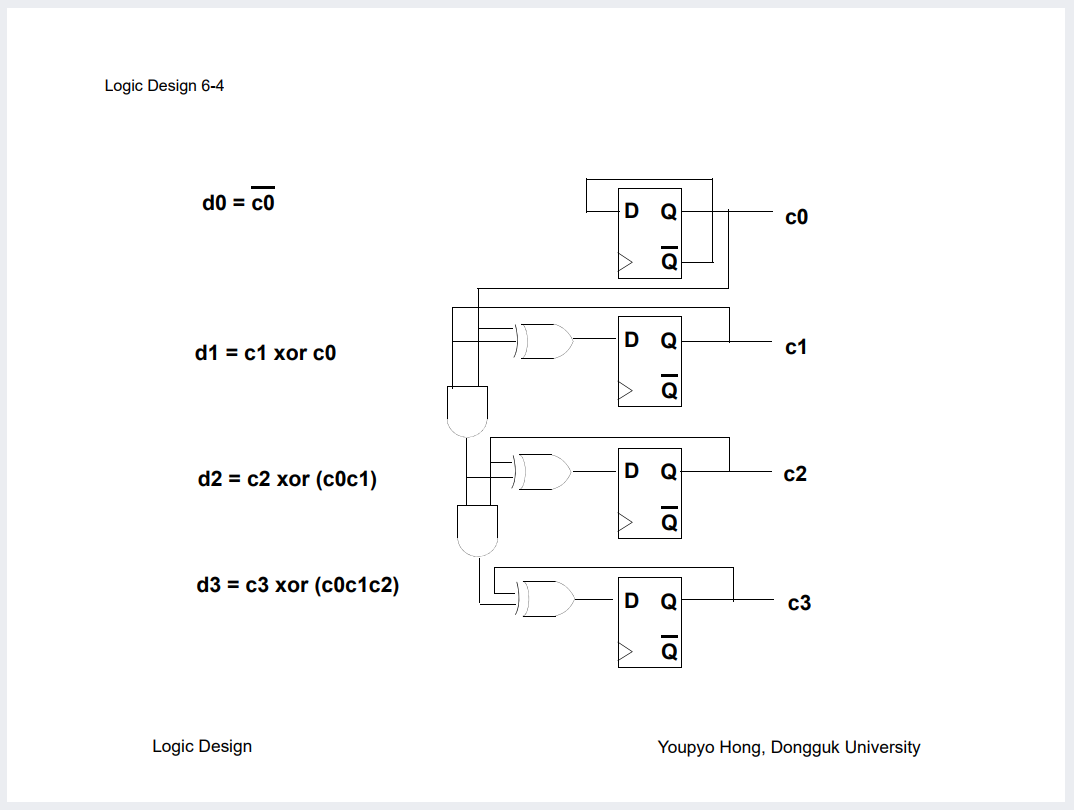

이걸 D FF로 구현해보자.

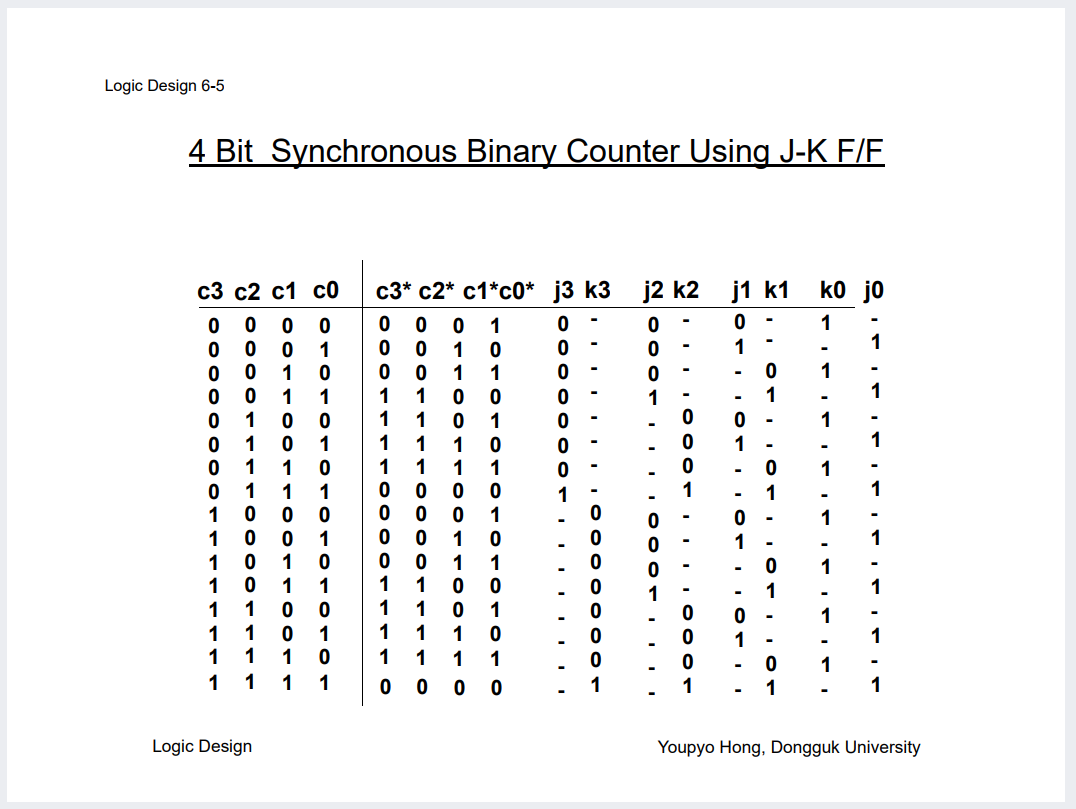

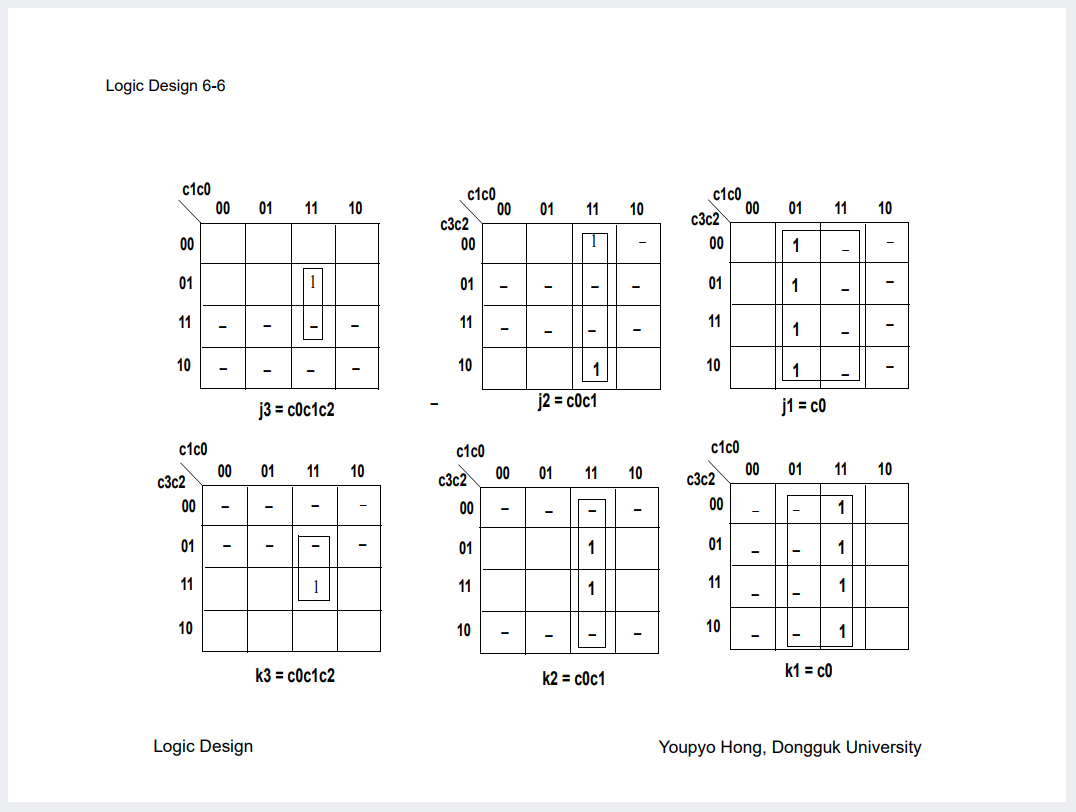

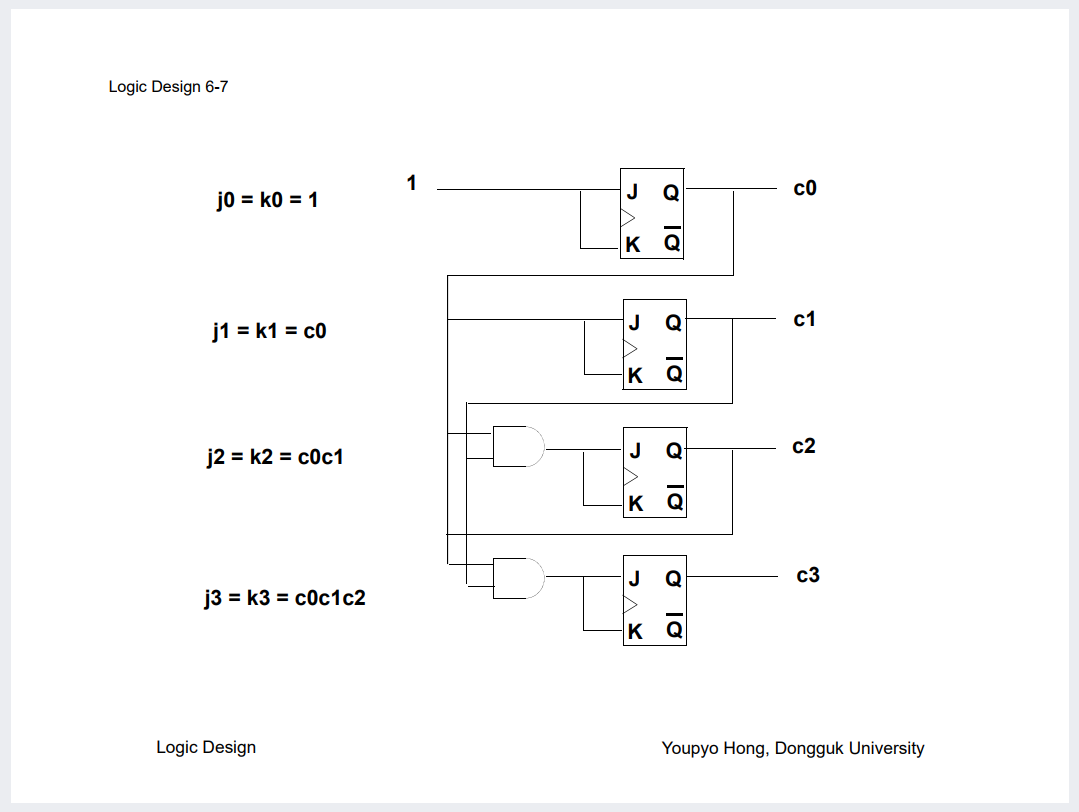

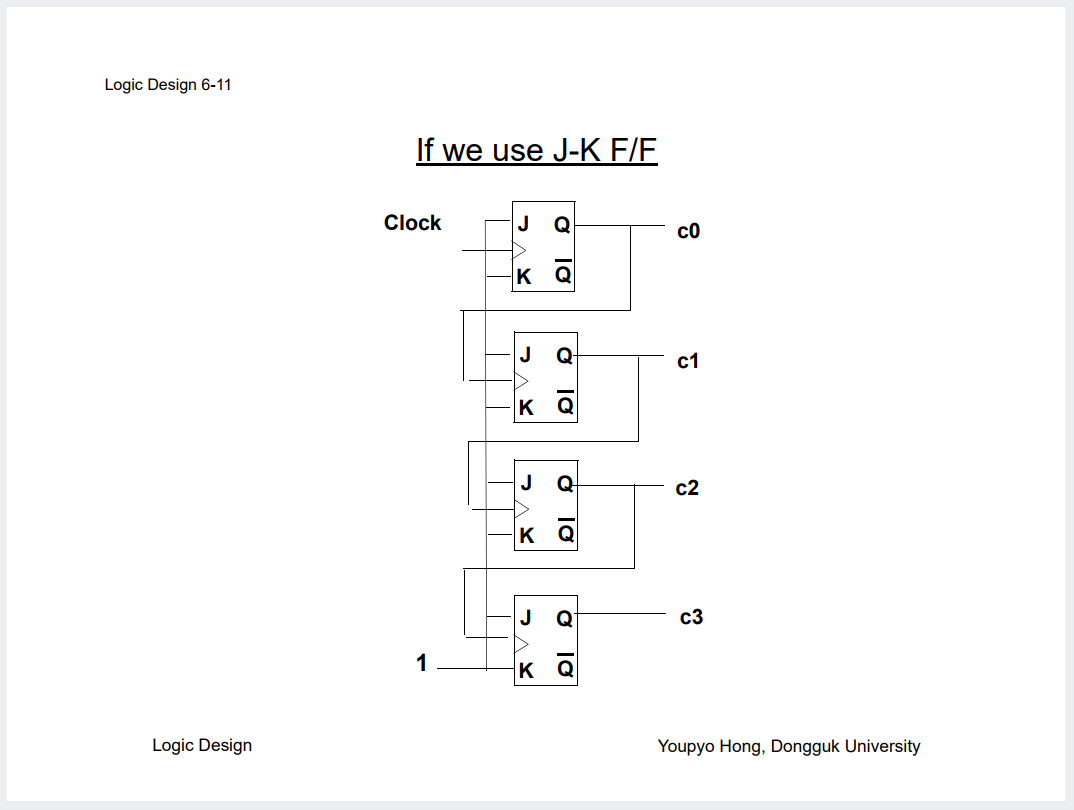

이번엔 JK로 구현해보자.

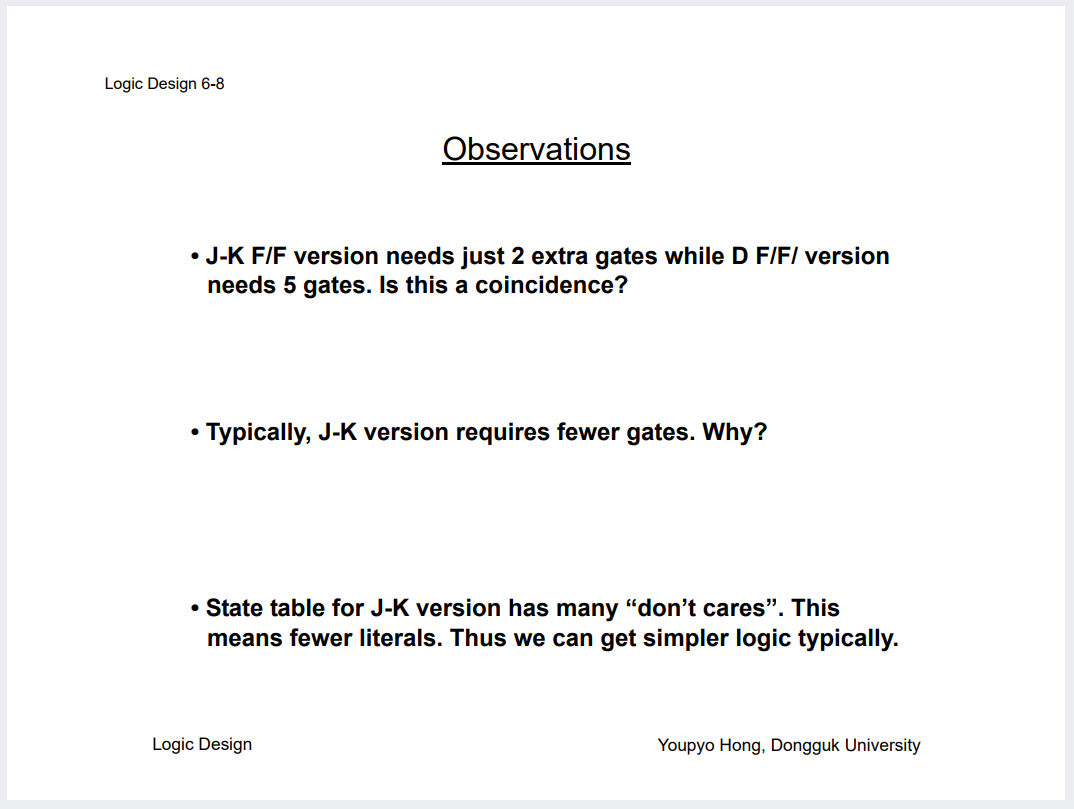

JK가 D보다 적은 Gate(D는 몇개고 JK는 몇갠지도 고려)가 필요한 이유를

Don't cares 신호 관점에서 생각 및 서술해보기.

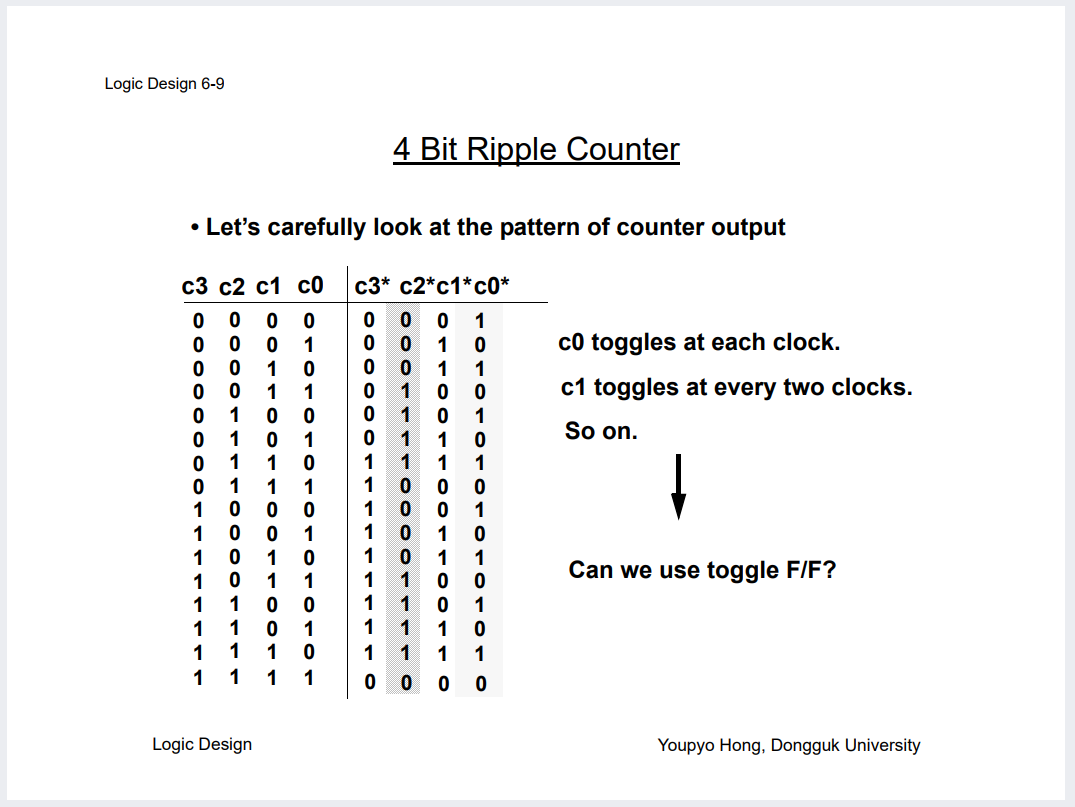

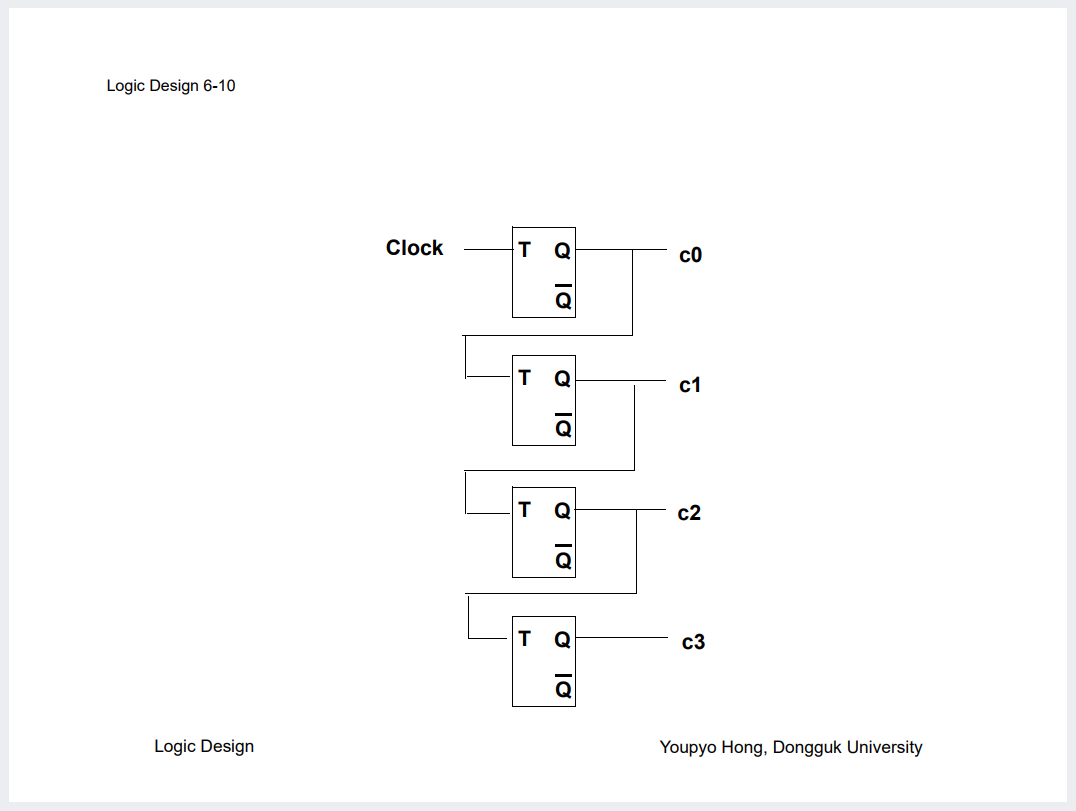

그럼 일반 Counter가 아닌 Ripple Counter도 보자. 얘는 Toggle 의 특성이 있으니 T FF 쓰면 효율적일까?

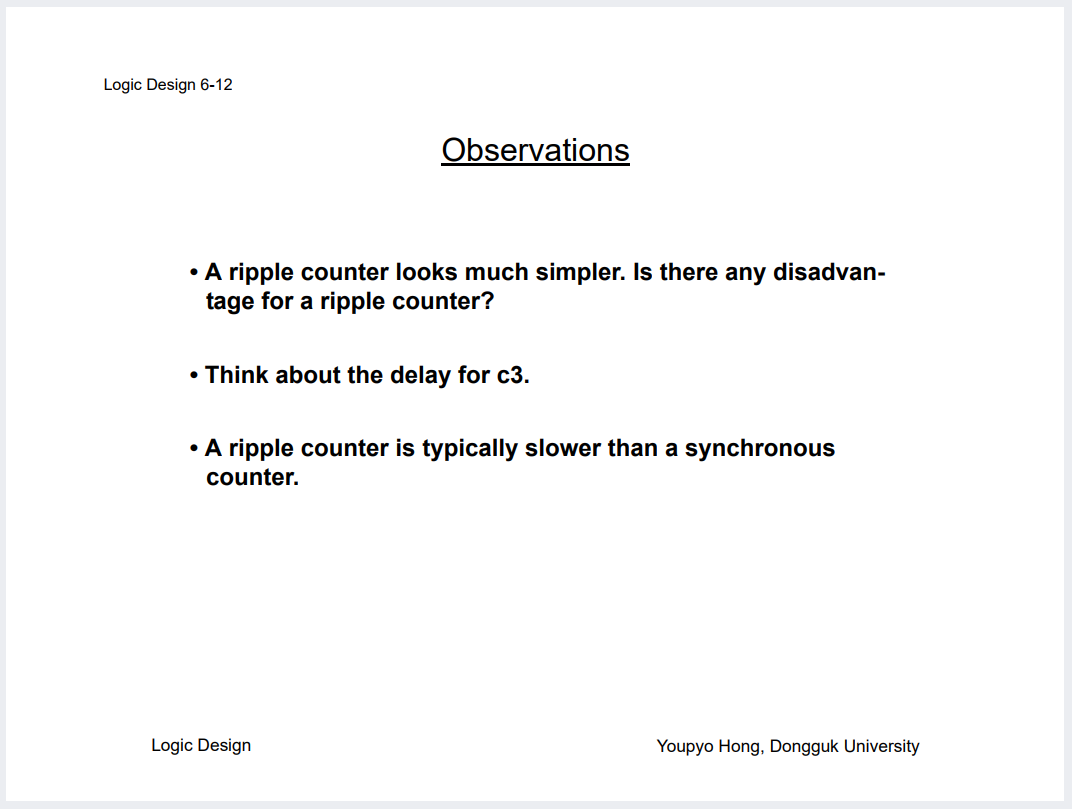

두 카운터의 장단점 비교.

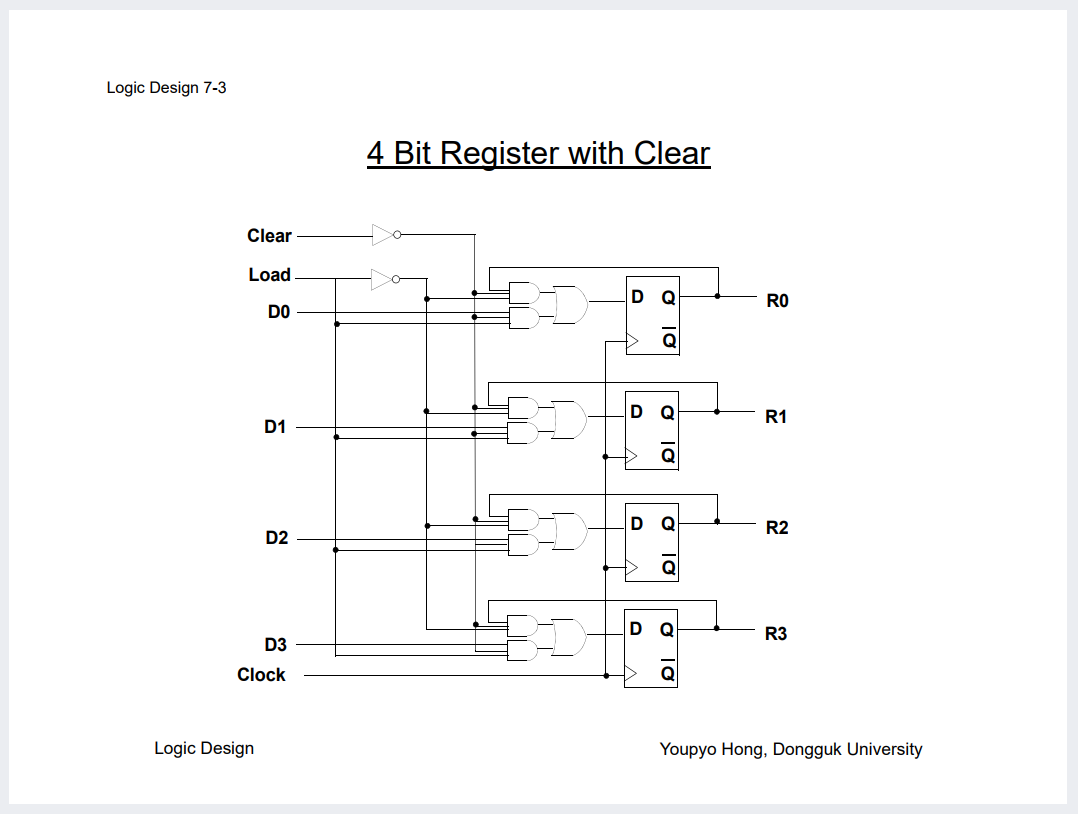

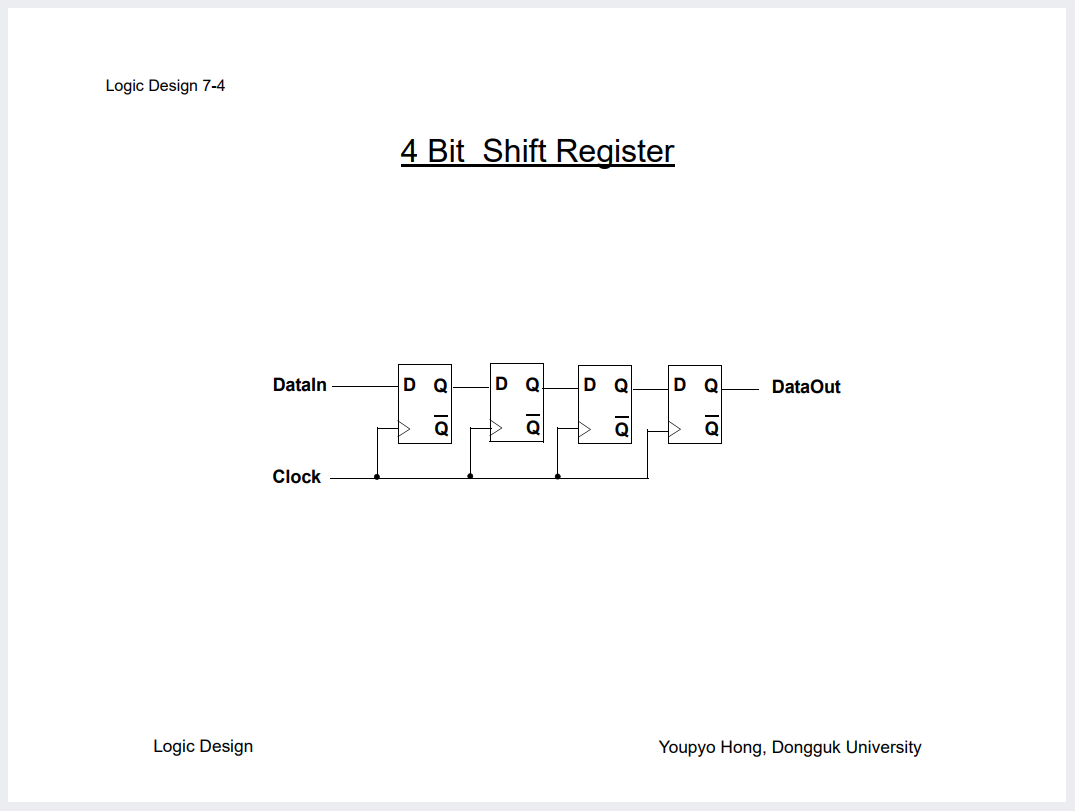

Lecture7 : Sequential Circuits Misc.

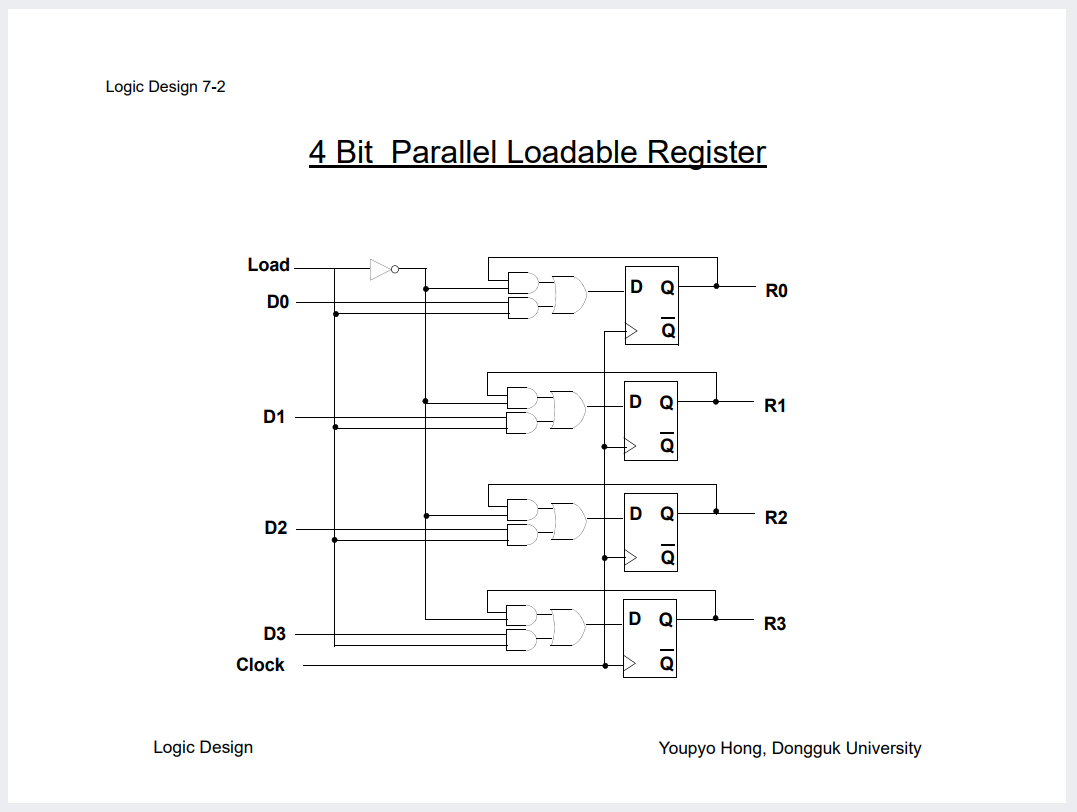

이 응용형들에 대해서도 함께 생각해보자.

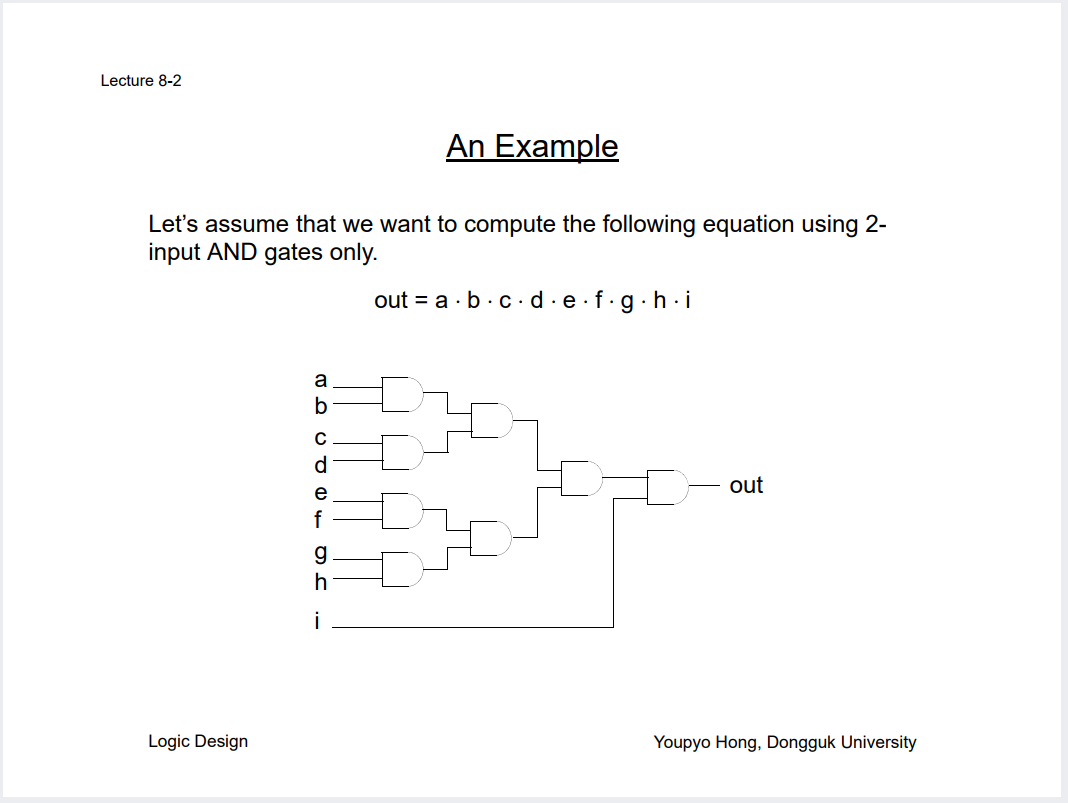

Lecture8 : High-Performance Design

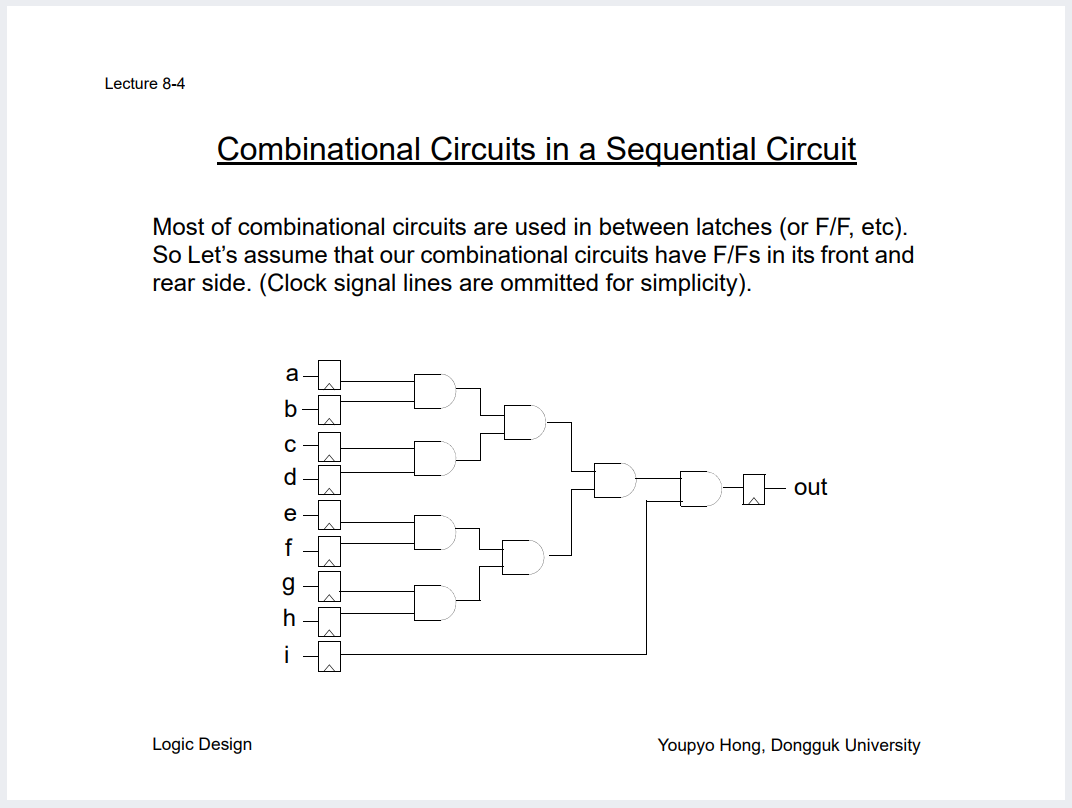

using 2-gate only 라는 조건이 있을때의 특징.

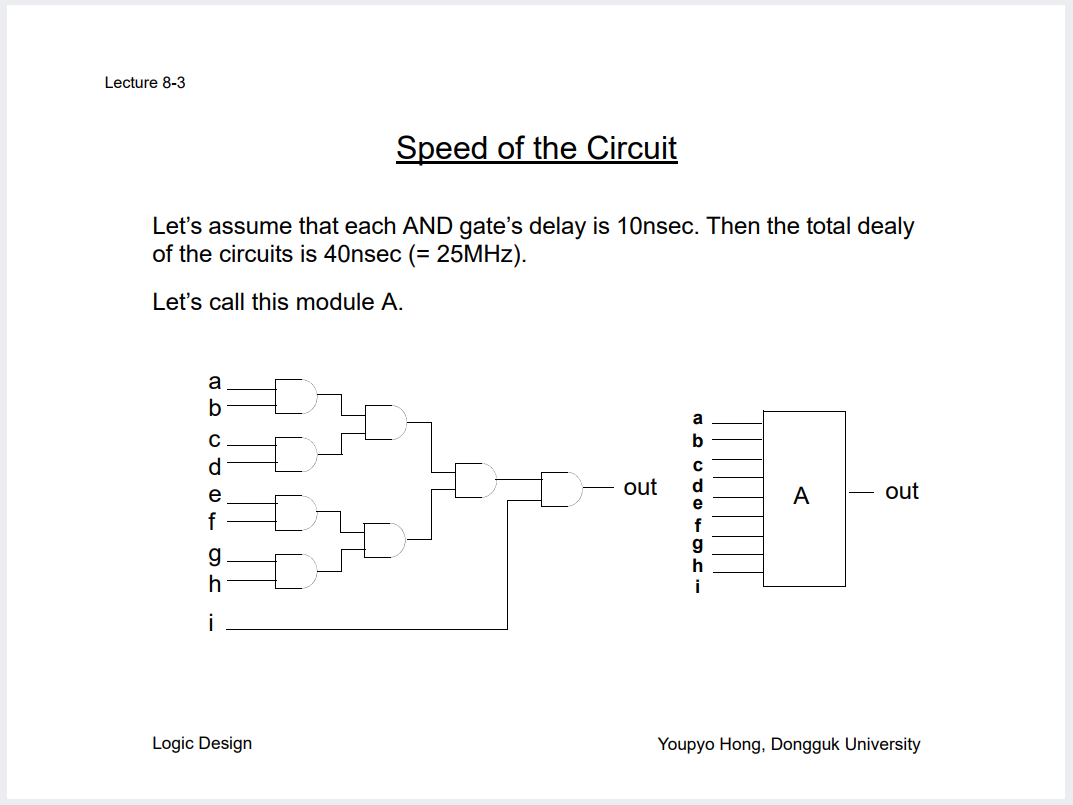

Speed of the circuit 이라는 개념.

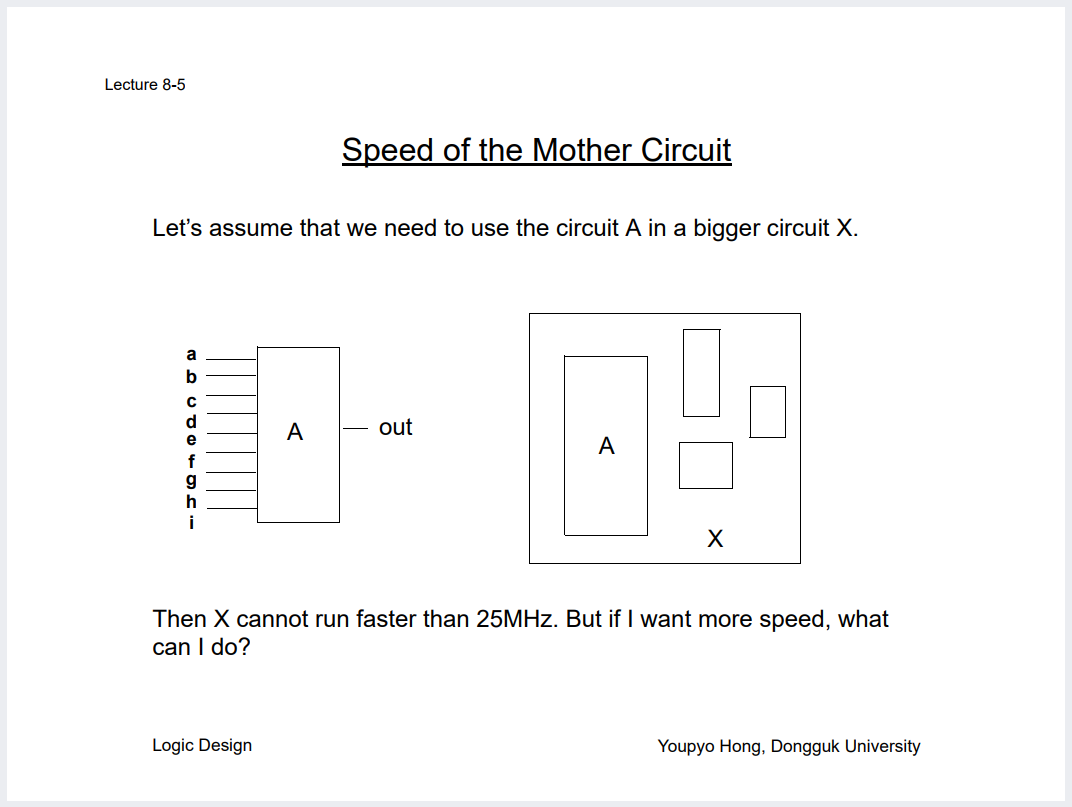

다음과 같은 문제상황이 있다고 할때, 어떻게 해결할지 생각해보자. Mother Circuit.

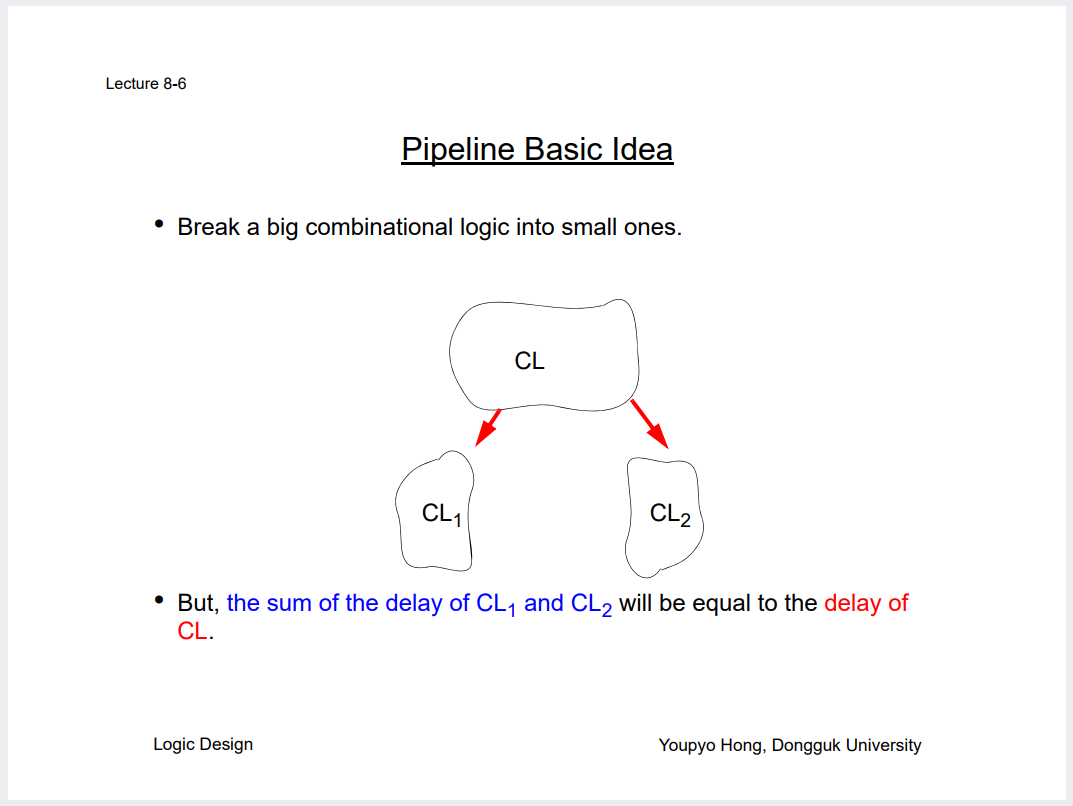

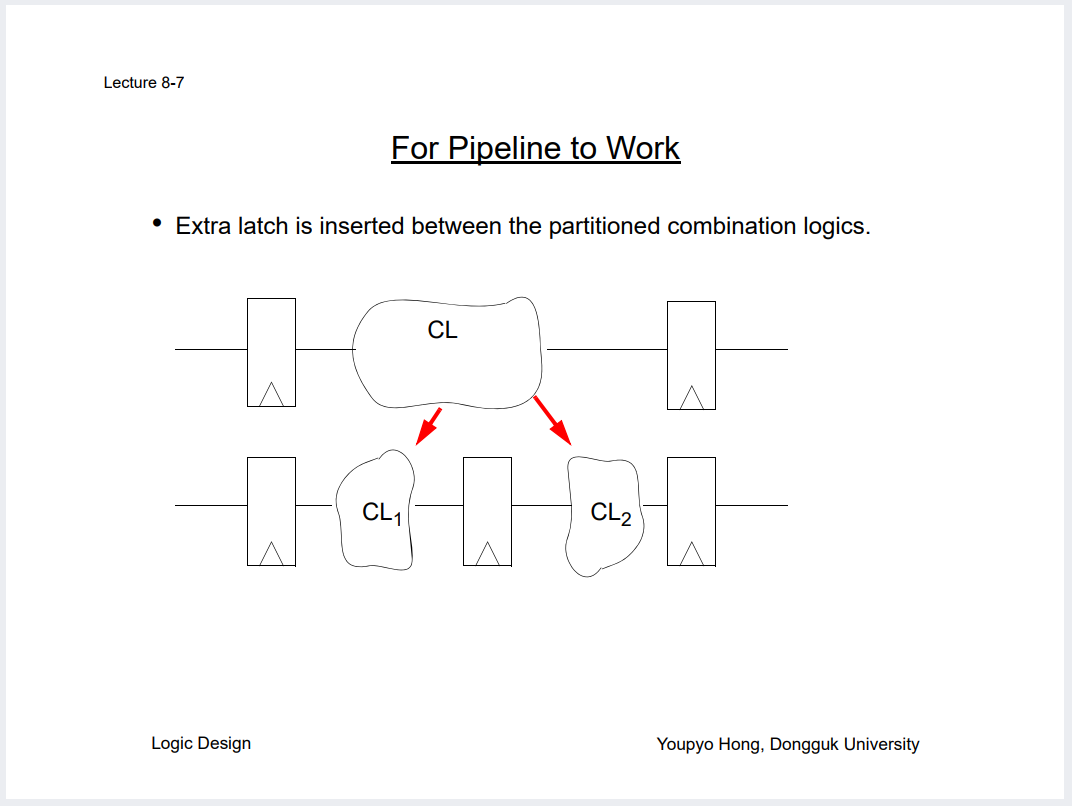

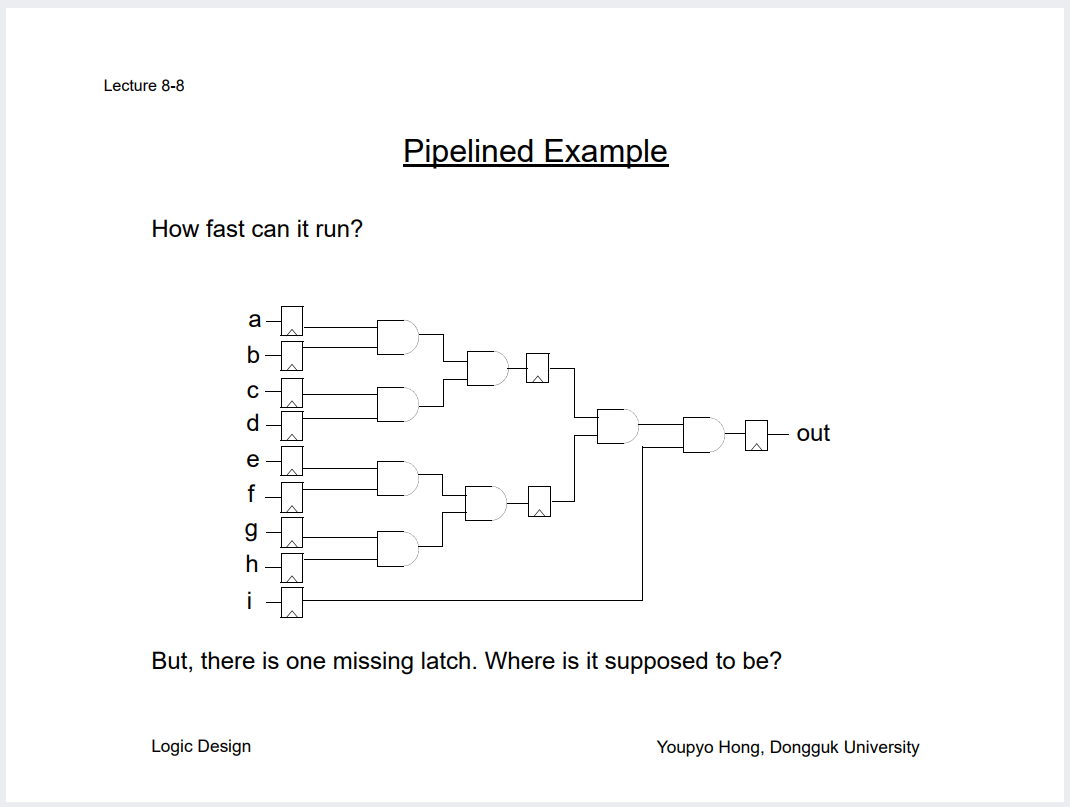

파이프라이닝을 해서 중간에 FF 하나 심으면 어떻게 상황이 변하는지 직접 계산해볼것.

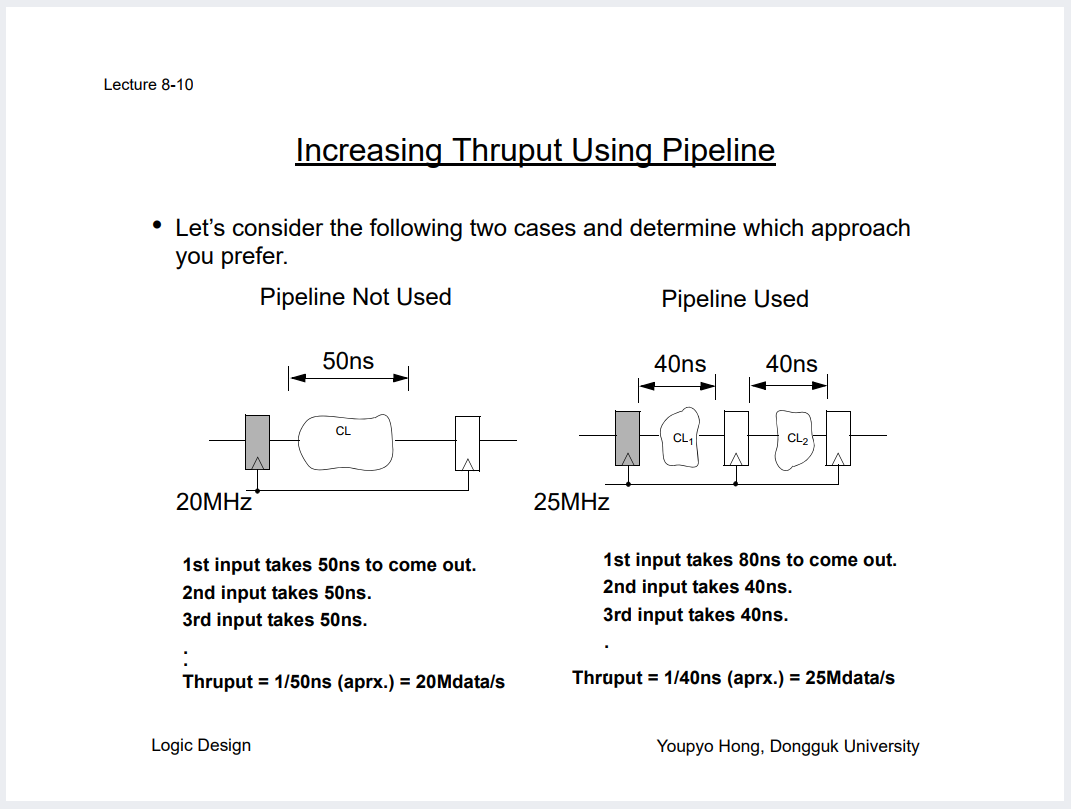

Thruput과 Delay라는 개념이 존재. 두개는 구분됨.

쓰루풋은 단위처리량이고, 딜레이는 처리기간임.

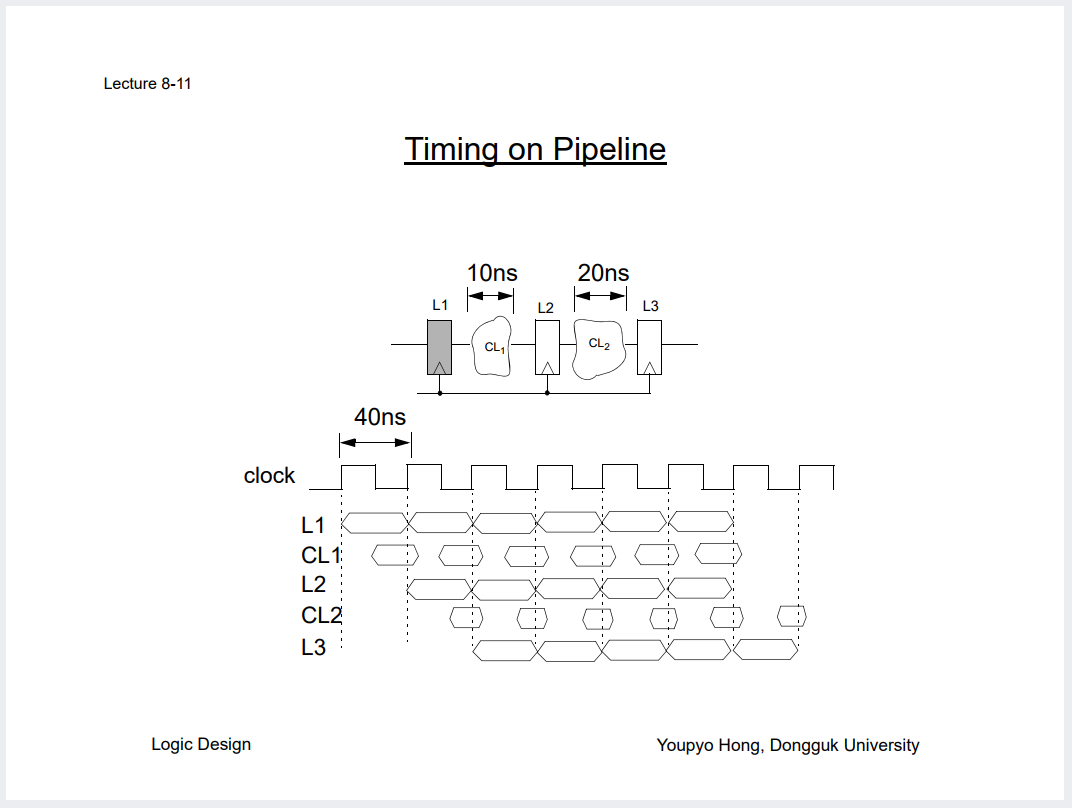

아 근데 여기서 CL1의 길이와 CL2의 길이가 달랐던 이유가 기억이 안난다.

Lecture9 : Programmable Logic Devices

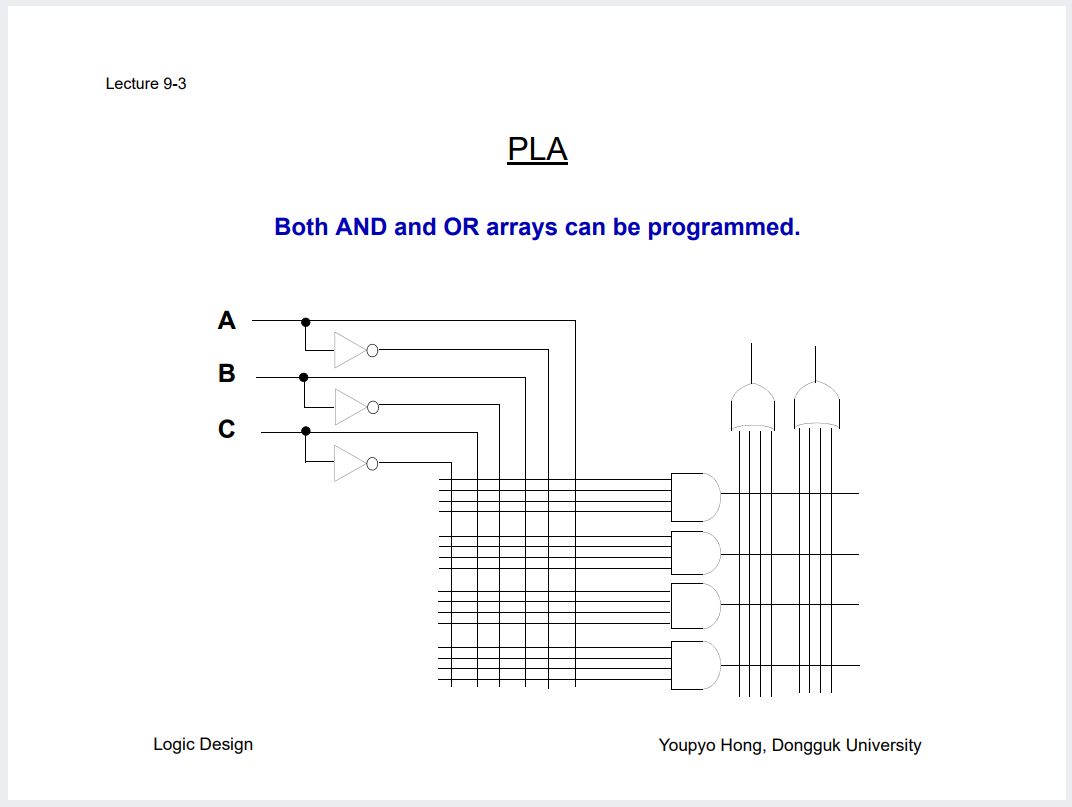

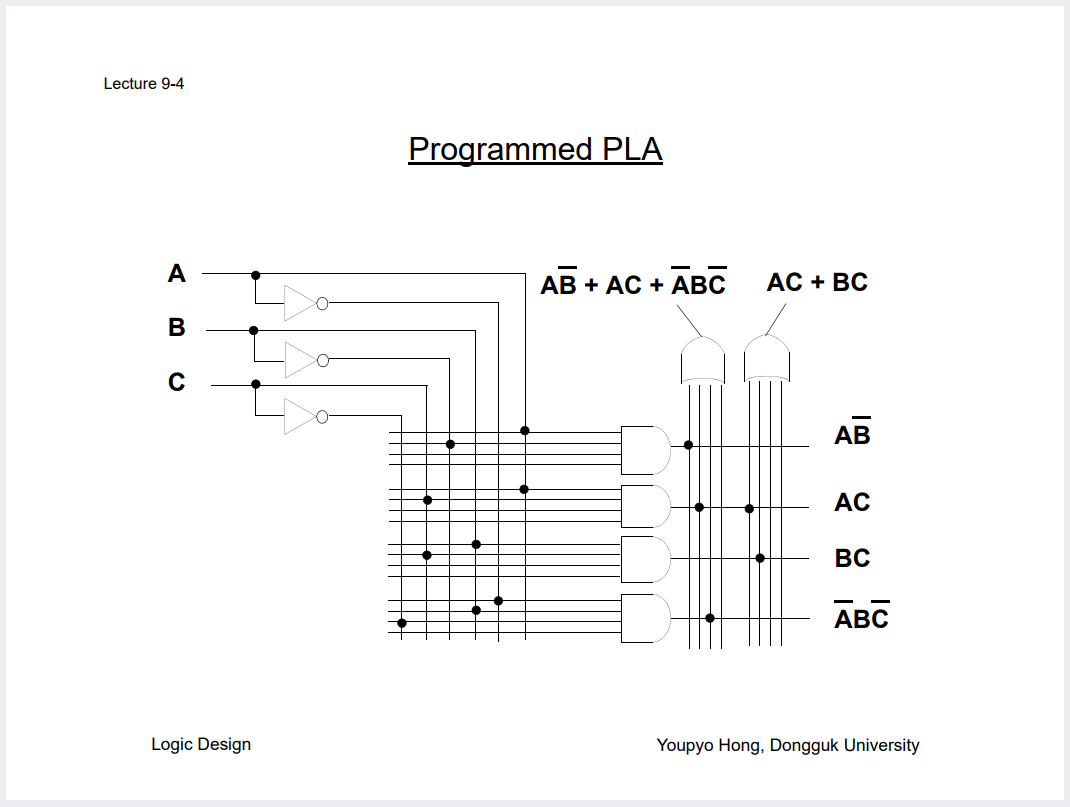

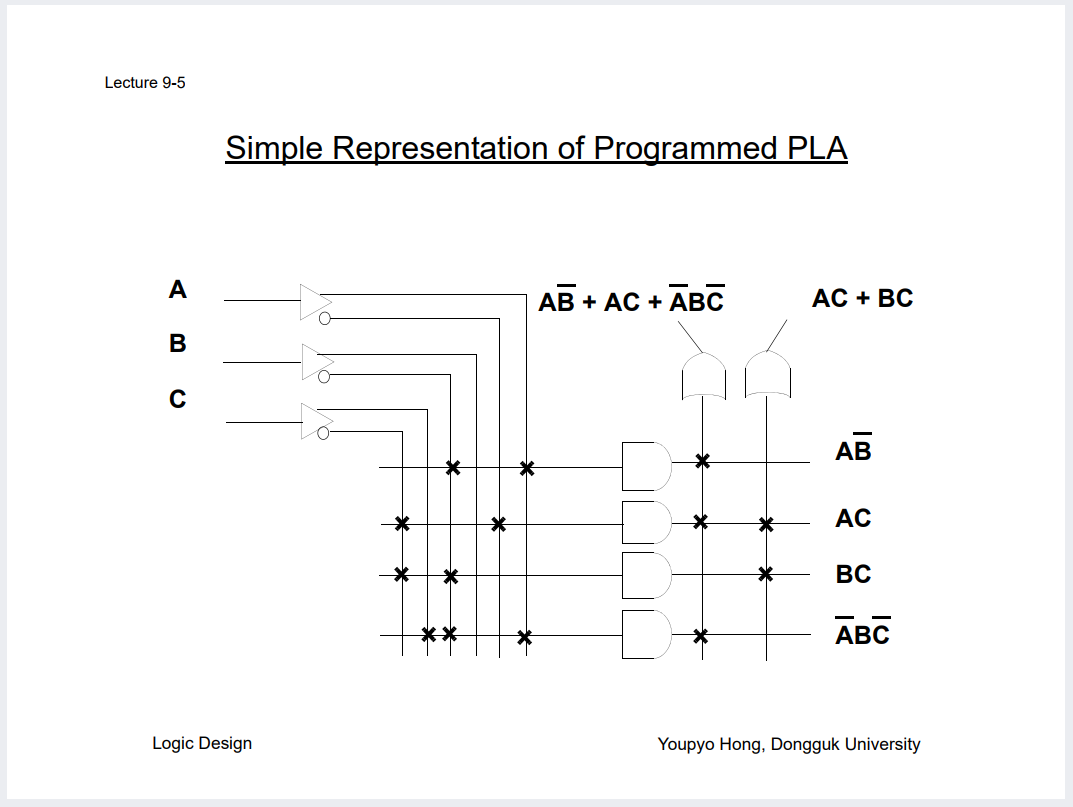

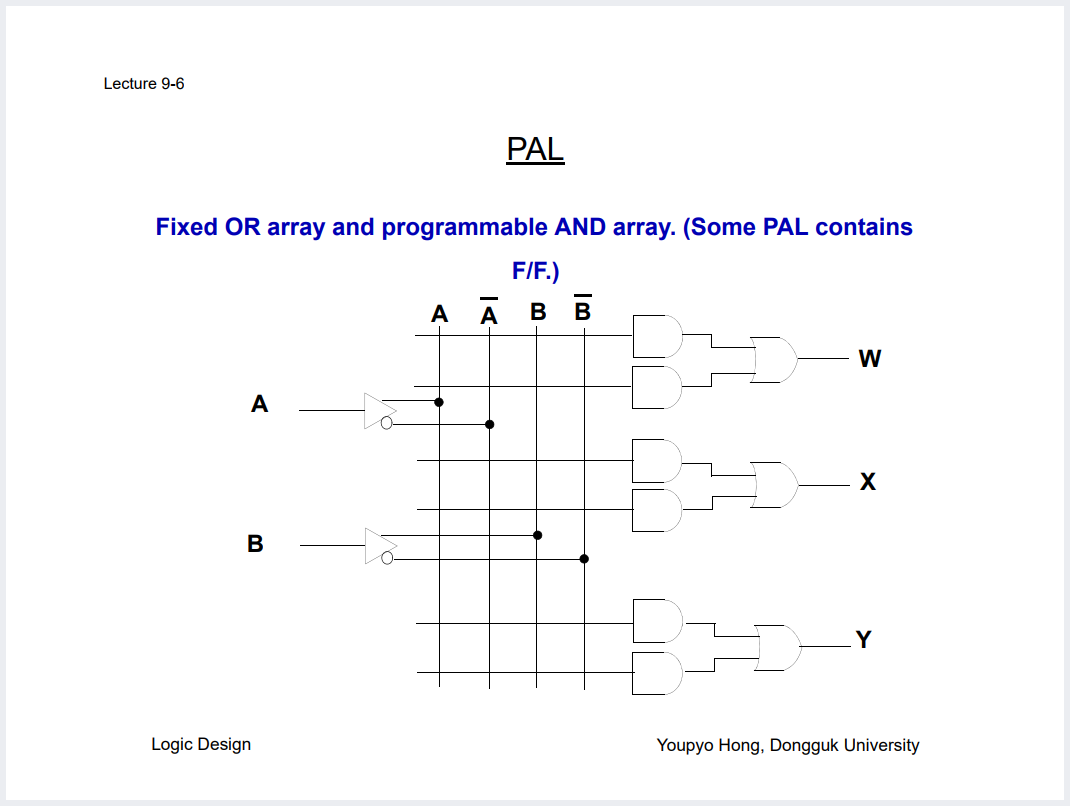

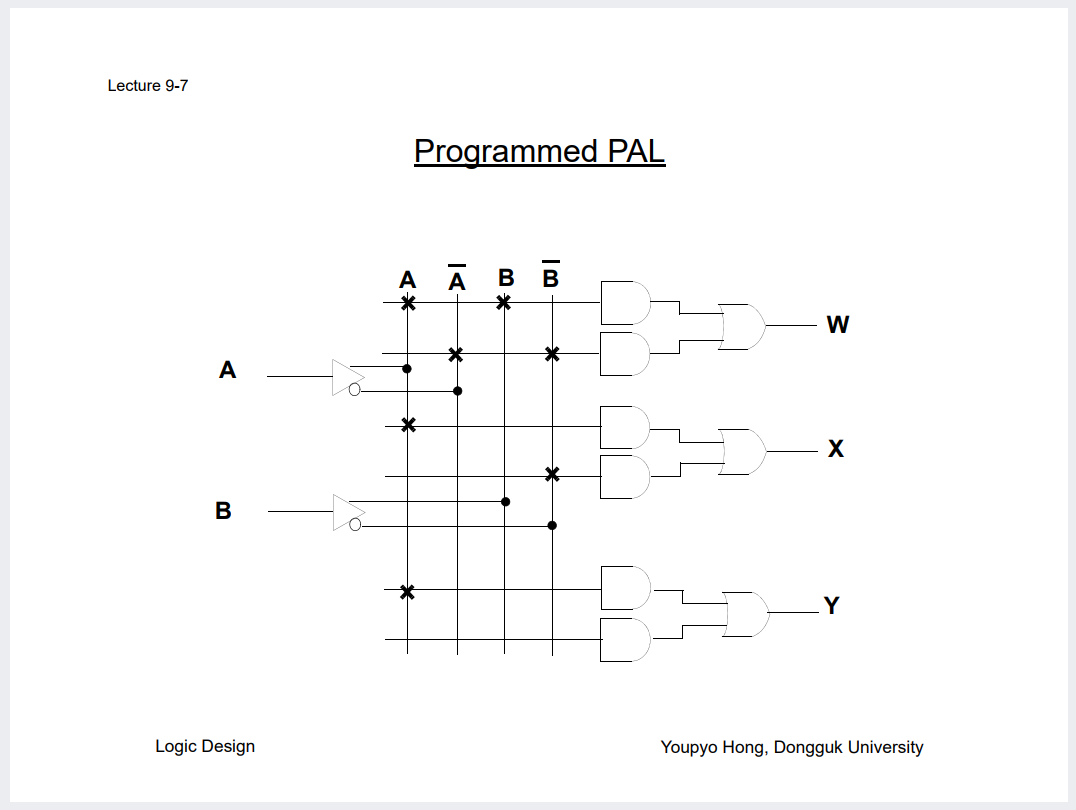

우리는 Sequential 한 회로를 하나로 Fix 시켰는데, Array 형태로 배열해두고 Programming 하는것도 가능하다.

이 사례가 위의 사례와 뭐가 다른건지 기억이 안나.

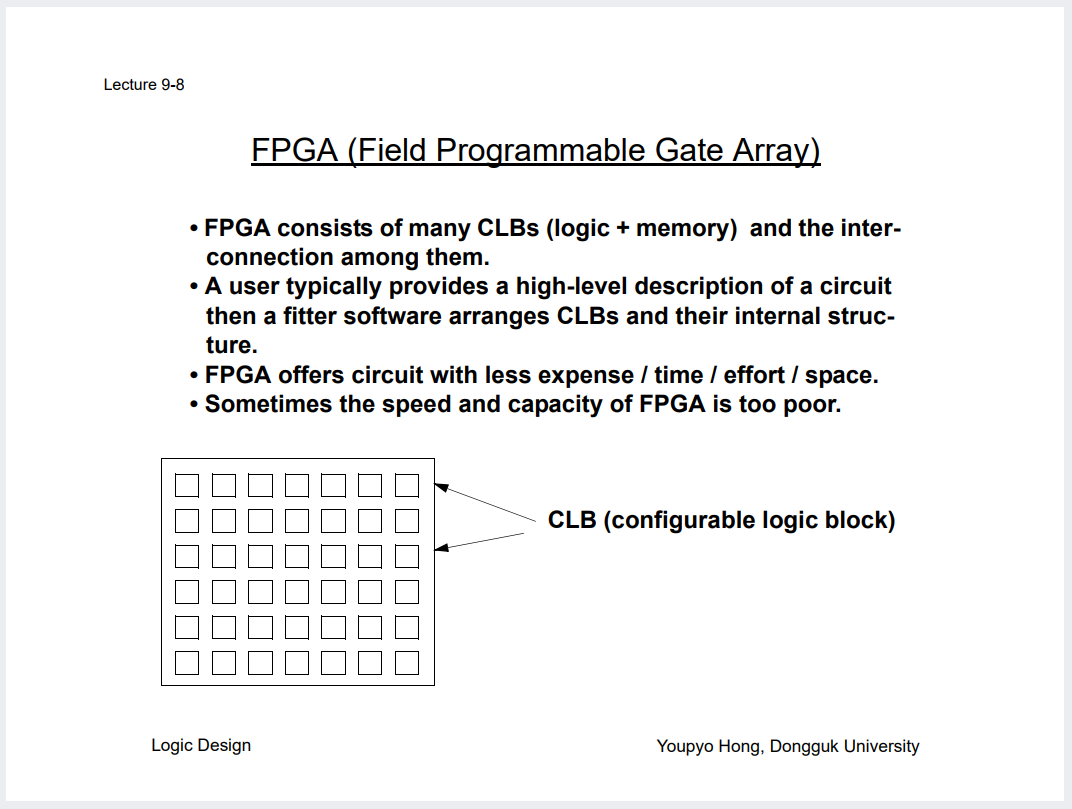

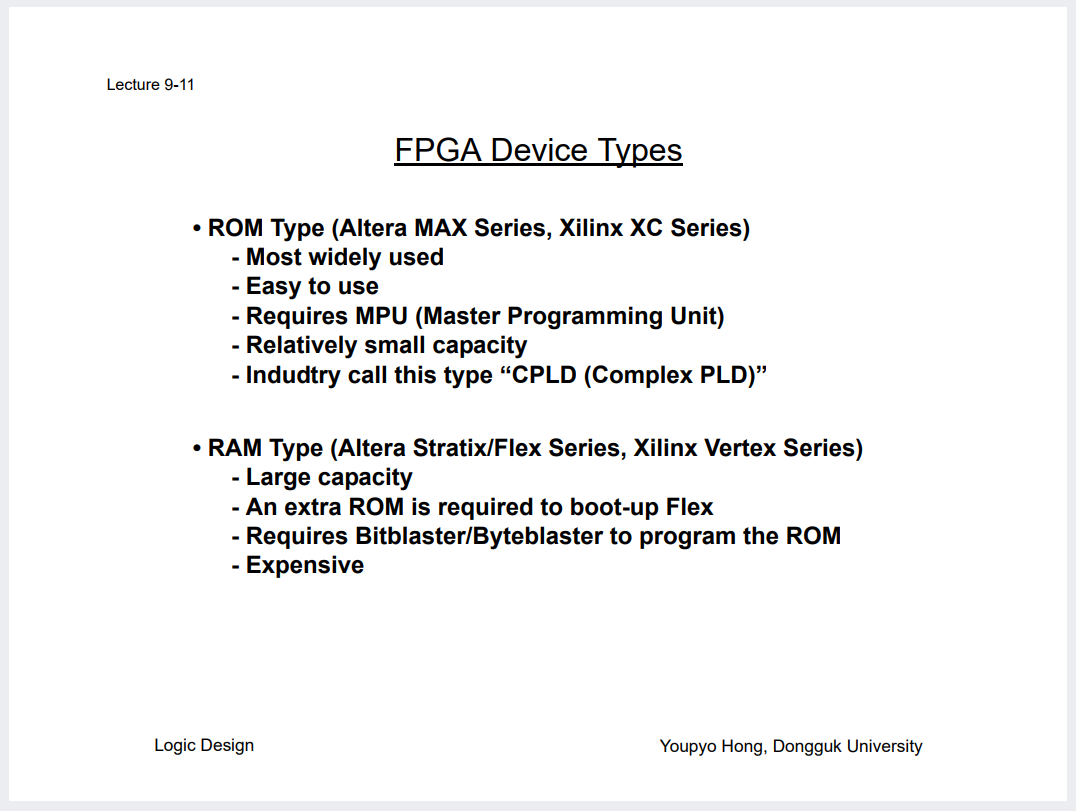

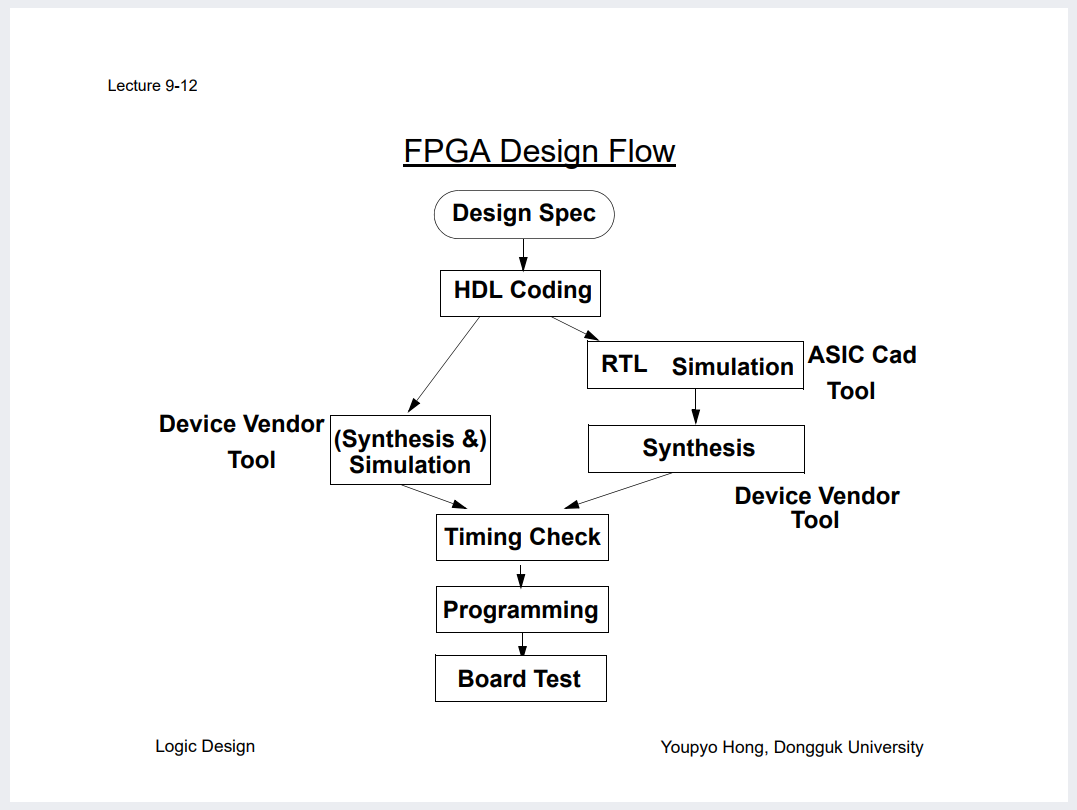

그래서 이 원리를 이용한 FPGA 같은것도 존재한다. (SoC의 양산전 아두이노 같은 용도)

'Engineering(SoC Design) > 디지털공학&논리회로설계' 카테고리의 다른 글

| 논리회로설계 (복습 10~12) (0) | 2022.03.11 |

|---|---|

| 논리회로설계 (복습 2~5) (0) | 2022.03.11 |

| 디지털공학 (복습 8~10) (0) | 2022.03.11 |

| 디지털공학 (복습 4~7) (0) | 2022.03.11 |

| 디지털공학 (복습 1~3) (0) | 2022.03.11 |