Lecture2 : Introduction to Sequential Circuits

우리가 디지털공학에서는 memory 역할이 없는 Combinational 회로만 다뤘다.

그러나 이제는 memory 역할을 더해, Sequential을 다루자. Counter 또는 Microprocessor 등.

memory가 있다는 것은 '이전값' 이라는 것에도 영향을 받는다는 것.

Sequential은 다시 둘로 나뉜다. Synchronous 와 Asynchronous로.

Asynchronous는 '순서'에도 영향을 받는데, 우선 Synchronous를 먼저 다루자.

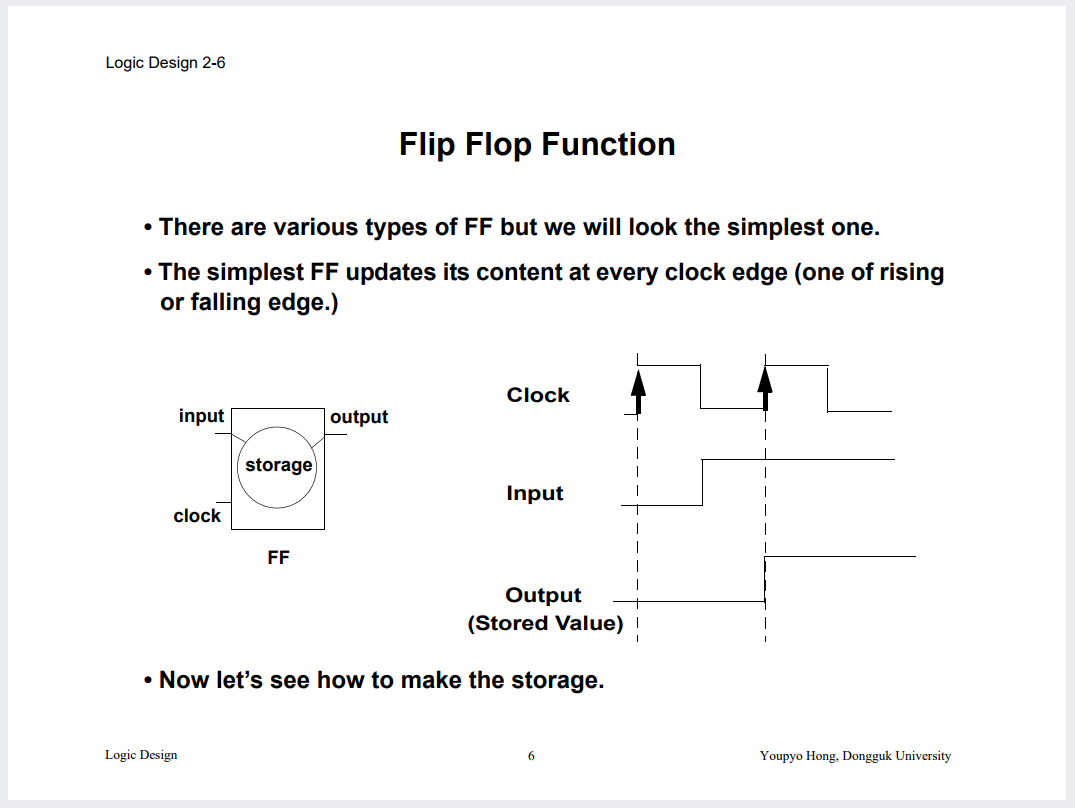

우리는 memory 소자에 clock pulse를 물려주기 시작할거다.

메모리에는 RAM, ROM, Flash, CD, Register 등이 있지만

우선 1bit를 저장할 수 있는 Flip Flop을 통해 접근하자.

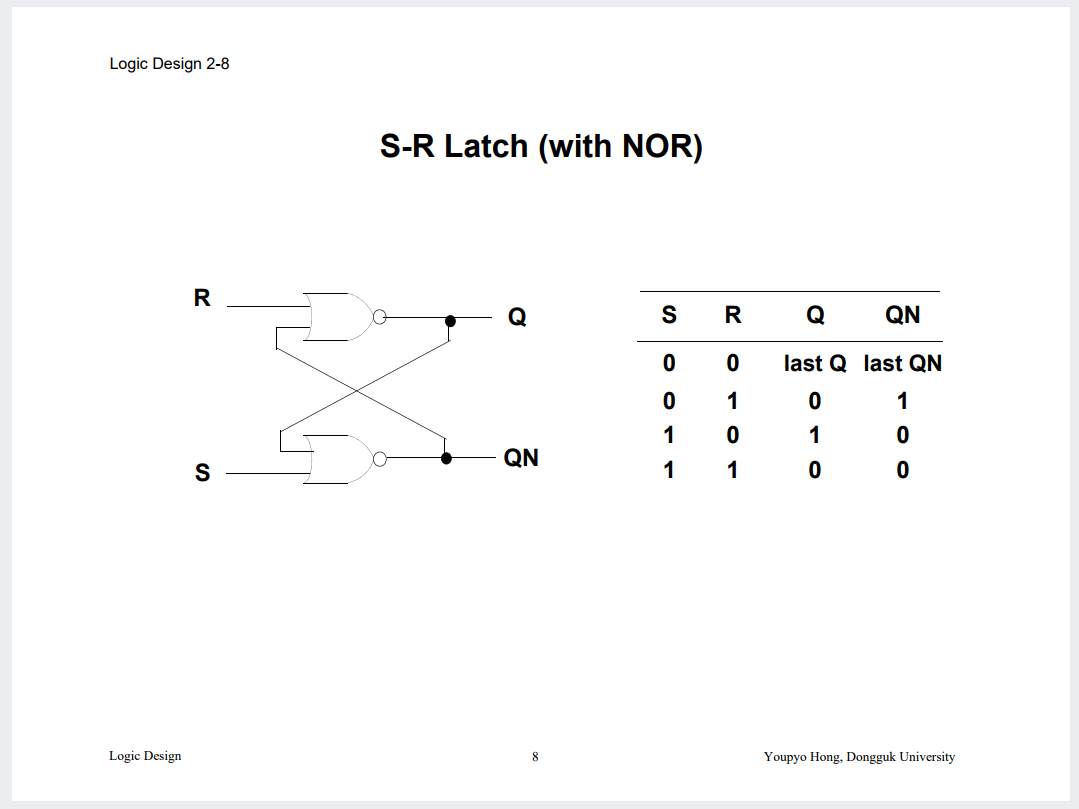

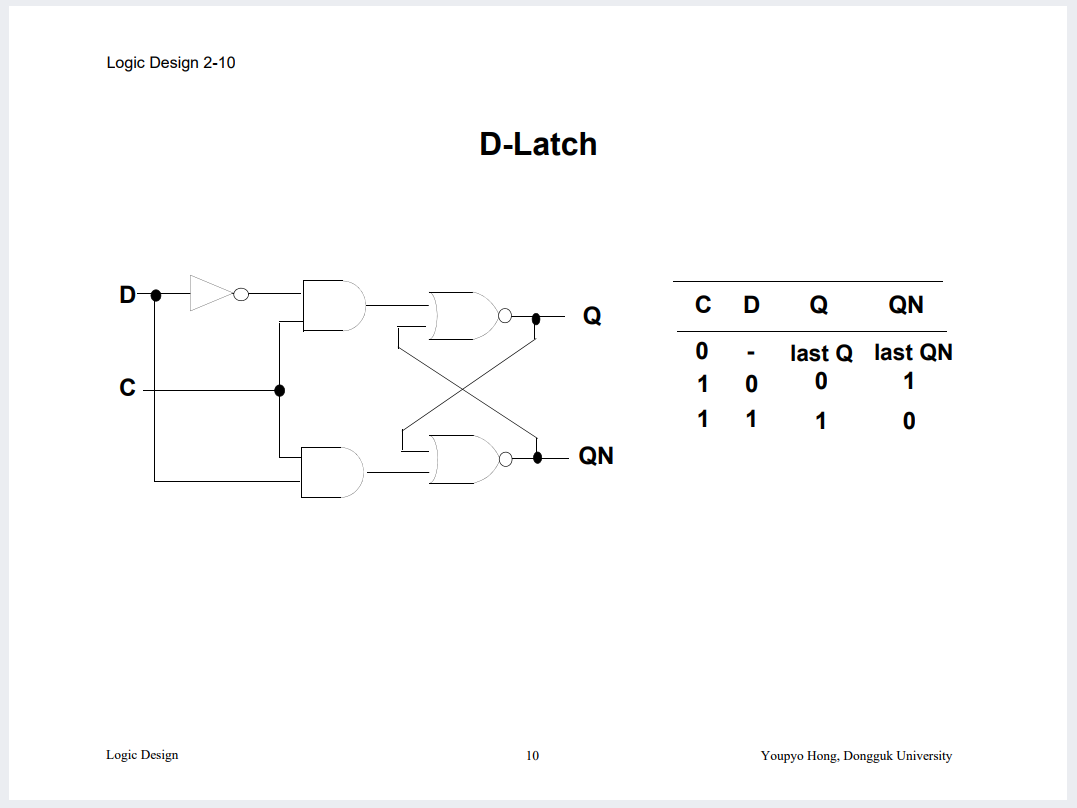

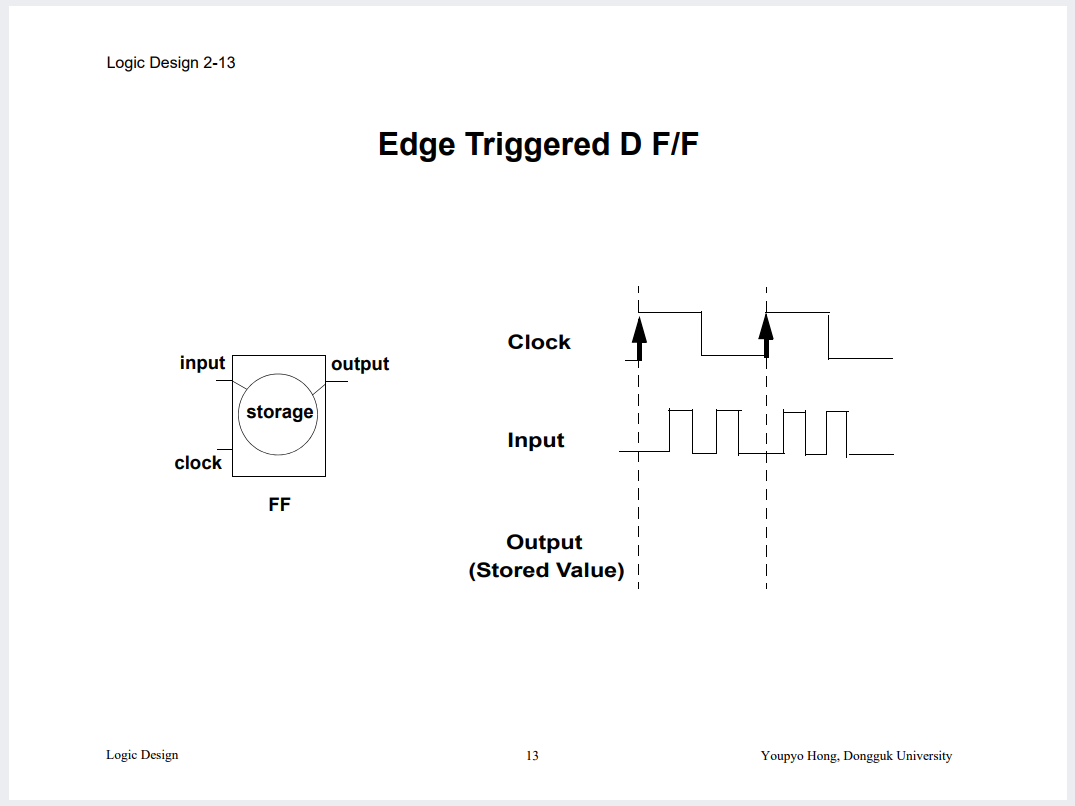

FF는 물려있는 값을, Clock timing(at rising edge)에 맞추어 뱉어준다. 그리고 그것은 Latch를 통해 구현된다.

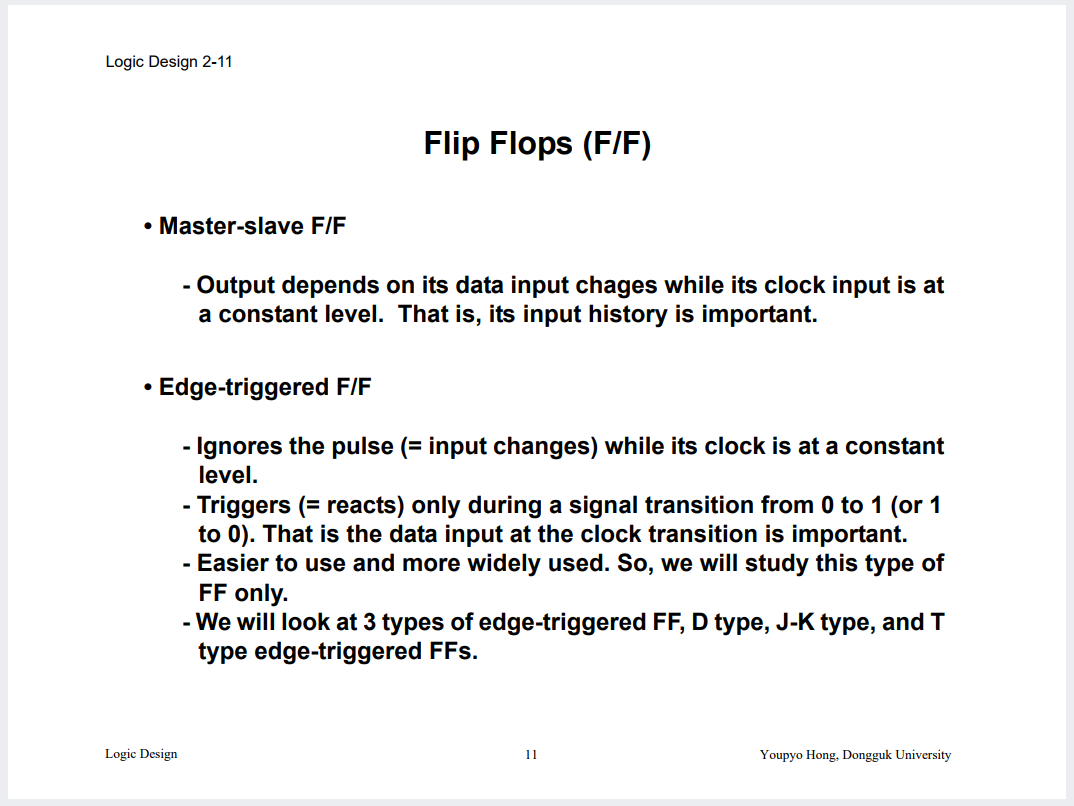

FF는 Master Slave와 Edge-triggered. 둘이 존재하는데, Master Slave는 Async에 가깝다. 우리는 엣지트리거로 다루자.

그리고 Edge-Triggered FF는 FF를 어떻게 응용해서 구현되는가?

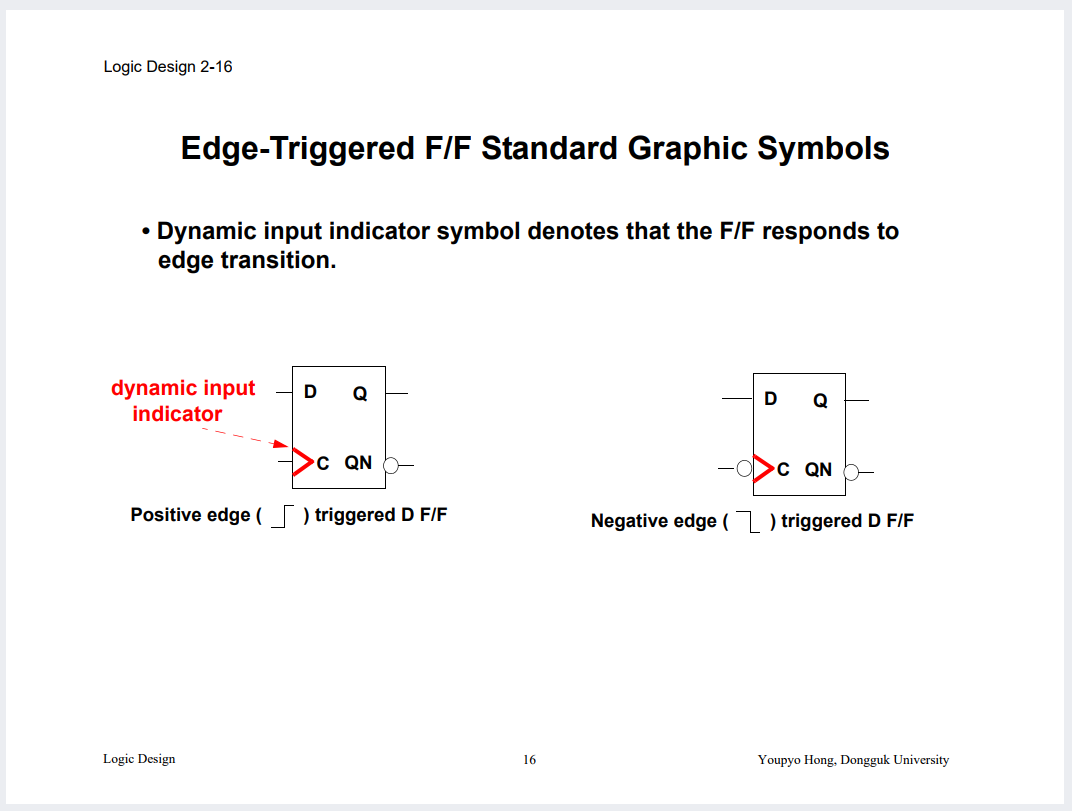

클락 물리는 FF는 다음과 같이 표준적으로 표기한다.

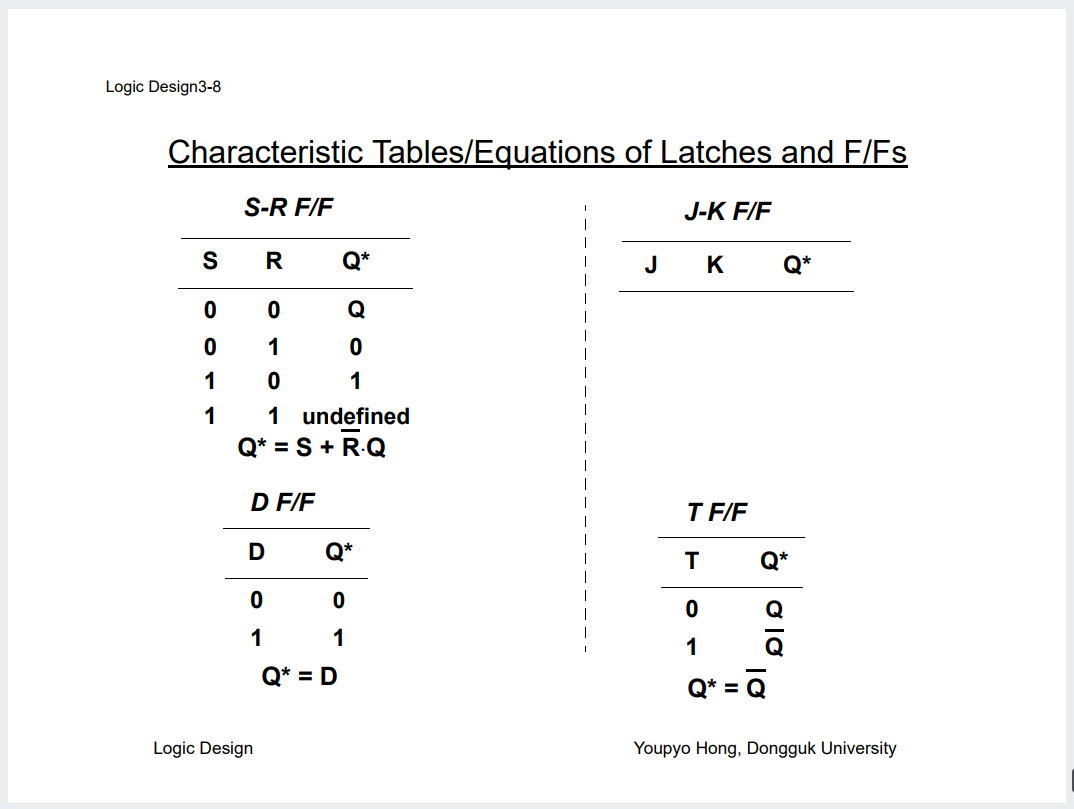

위의 D FF에서는 하나의 신호를 낭비하고 있었다.

그래서 그 신호 낭비를 줄이기 위해 JK FF를 만들었다.

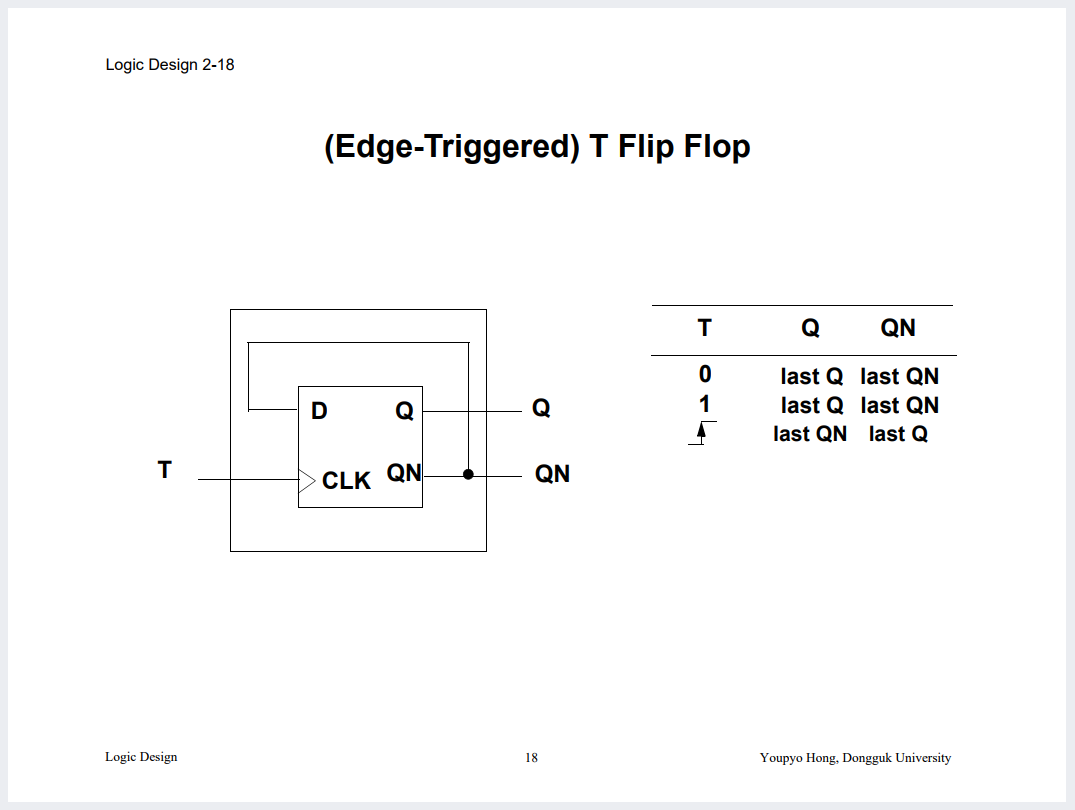

그리고 JK FF에서 00, 11 일때의 로직만을 활용하기 위한 T FF도 있다.

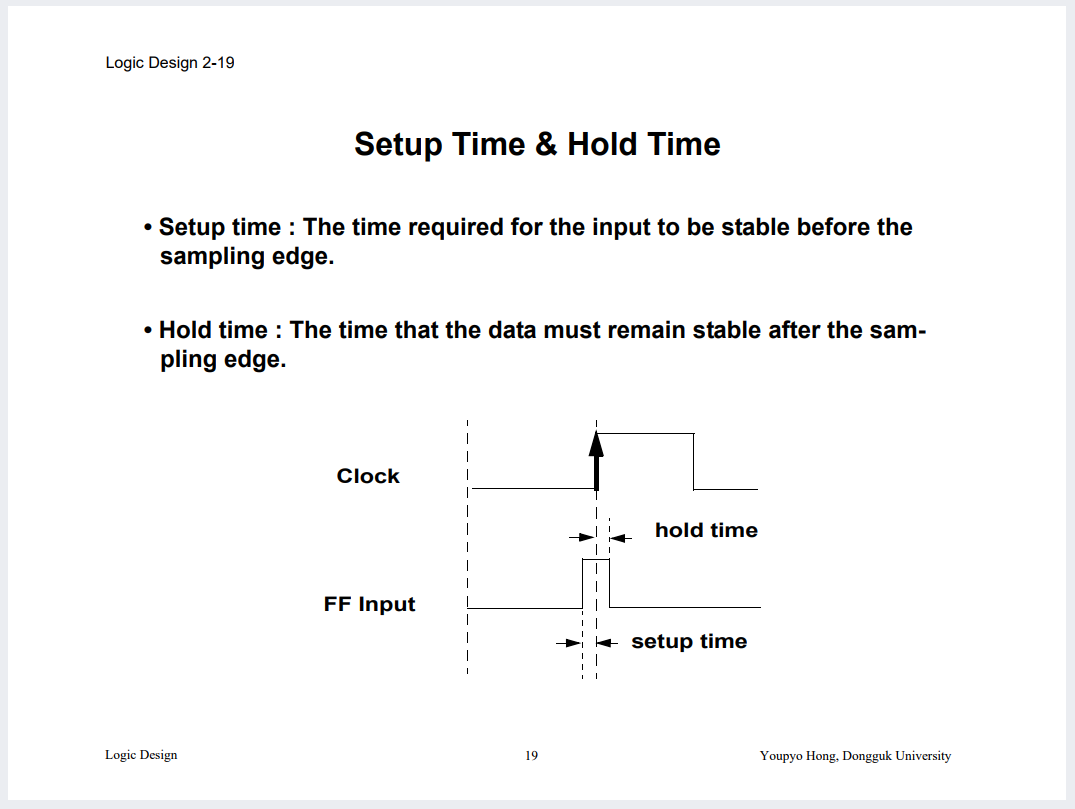

FF이 Input을 인식하기 위해, 최소한의 Setup후에 들어와주어야 하고, 일정시간을 또 Hold 해주어야 한다.

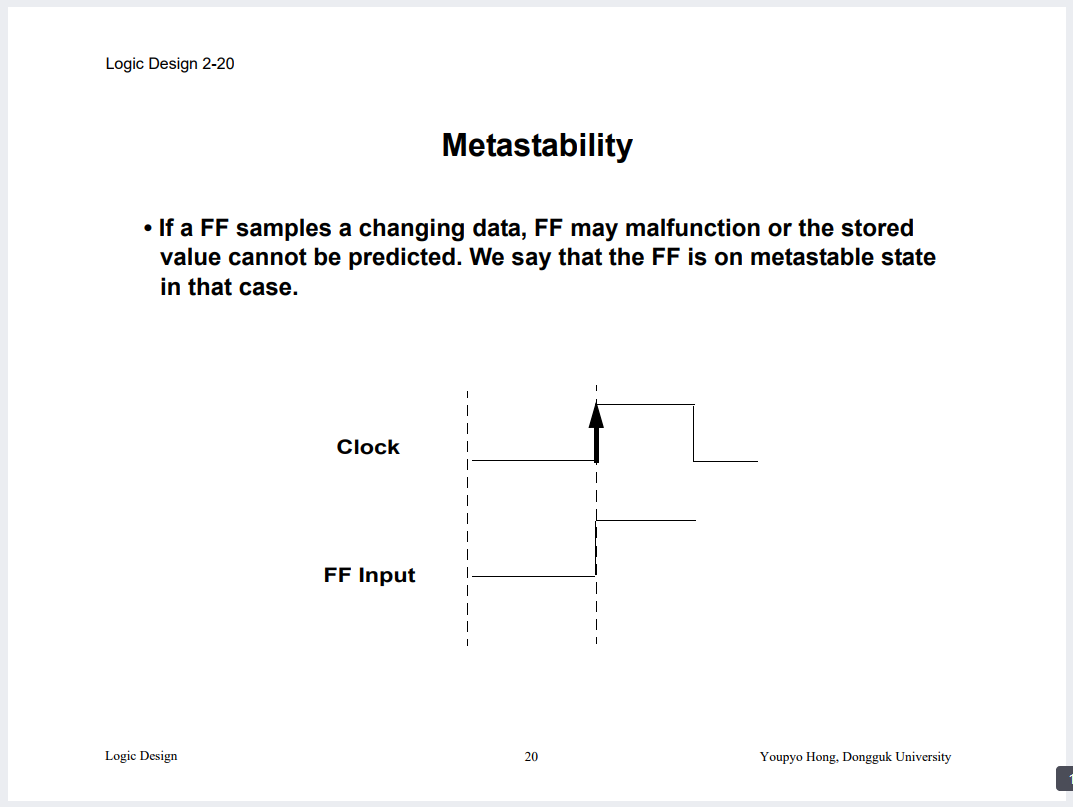

그 시간을 확보하지 않는다면, 예측이 불가능한 Metastable 문제가 발생할 수 있다.

Lecture3 : Sequential Circuits Basics

자 그런데 우리가 1bit만 다룰건 아니잖아,

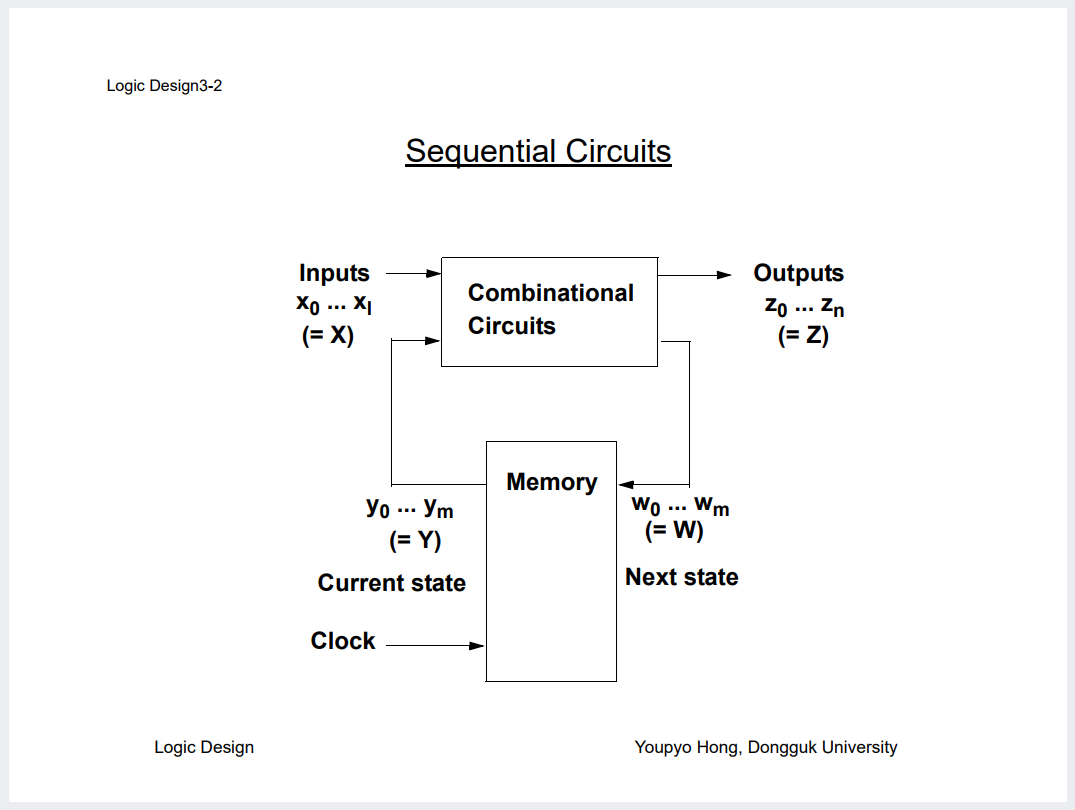

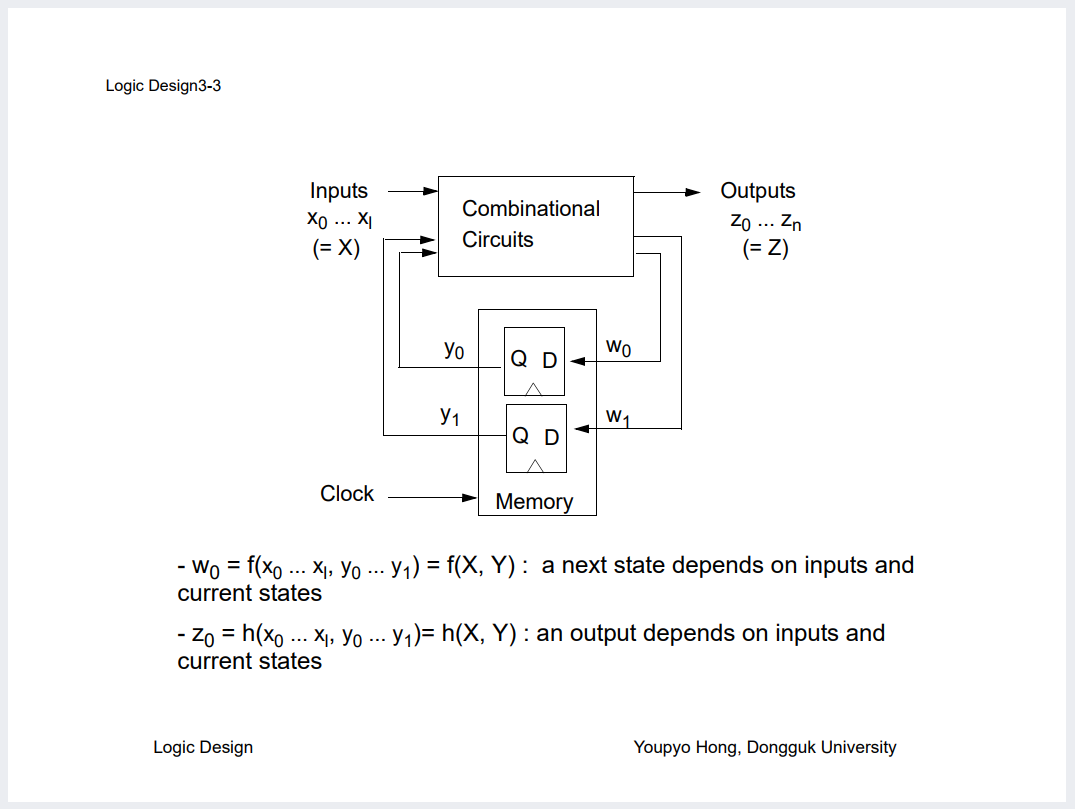

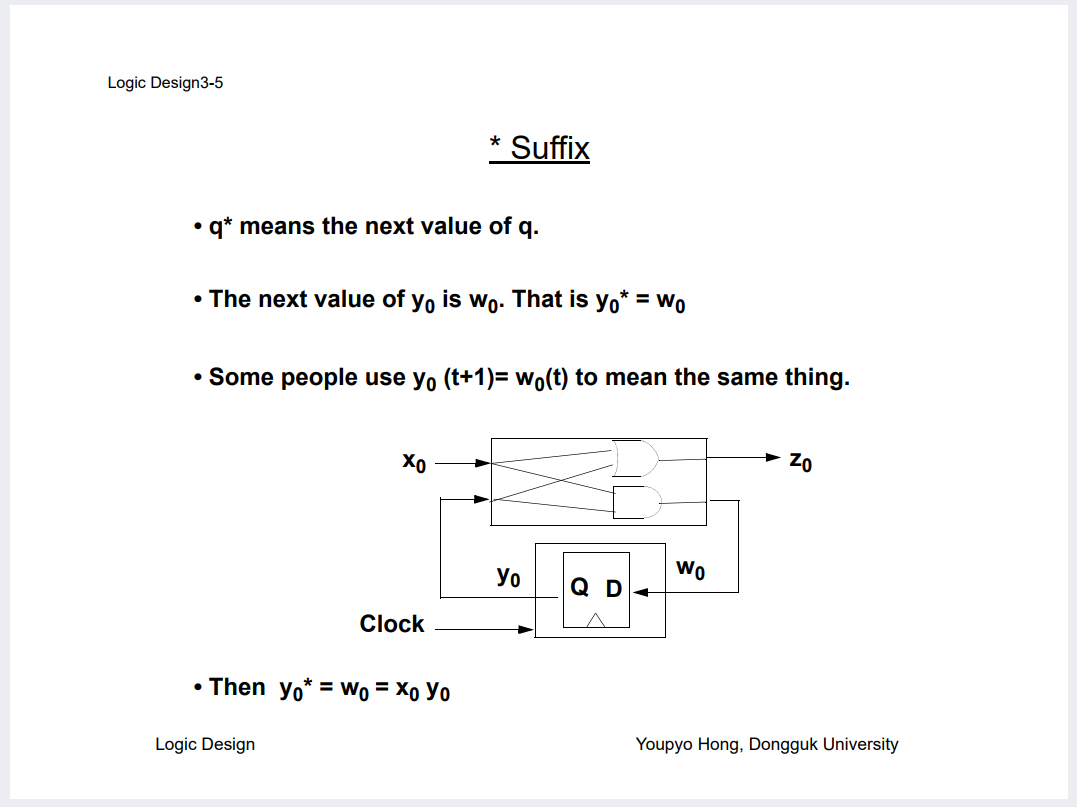

그러다보니 Sequential을 이런 형태로 인식하는게 좋다. xywz, q, q*

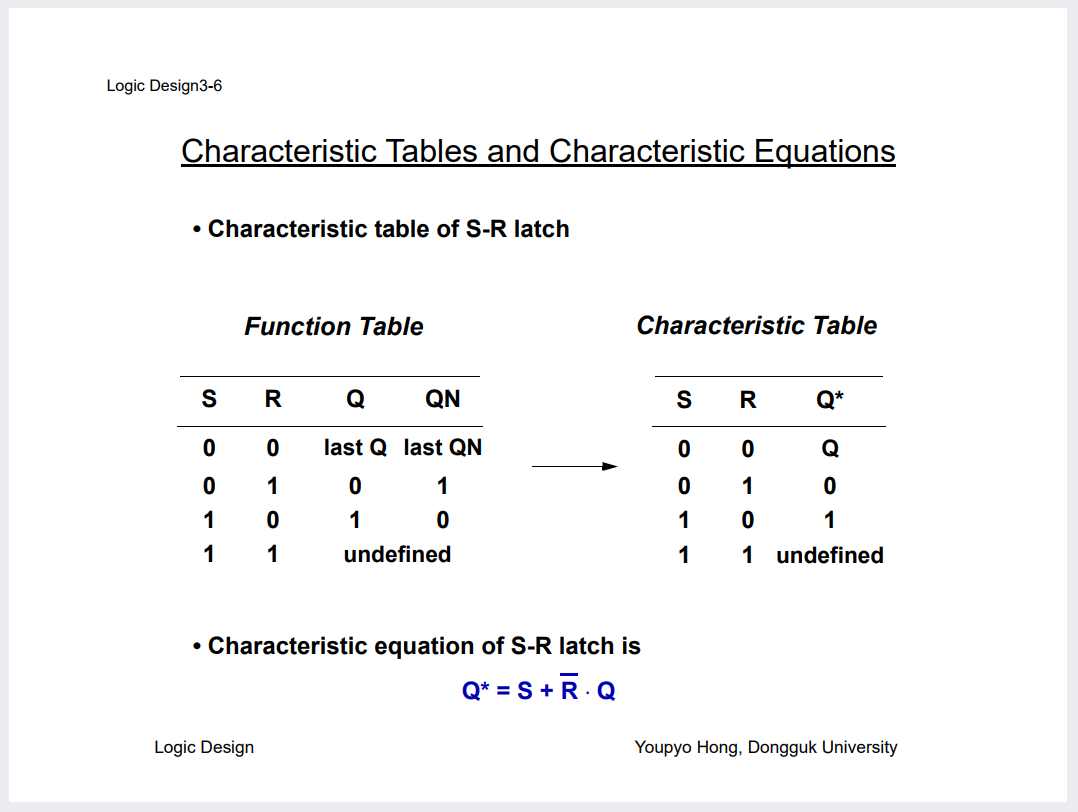

이 표현체계를 이용하면, 지난번 개념을 이렇게 정돈해서 표현할 수 있다.

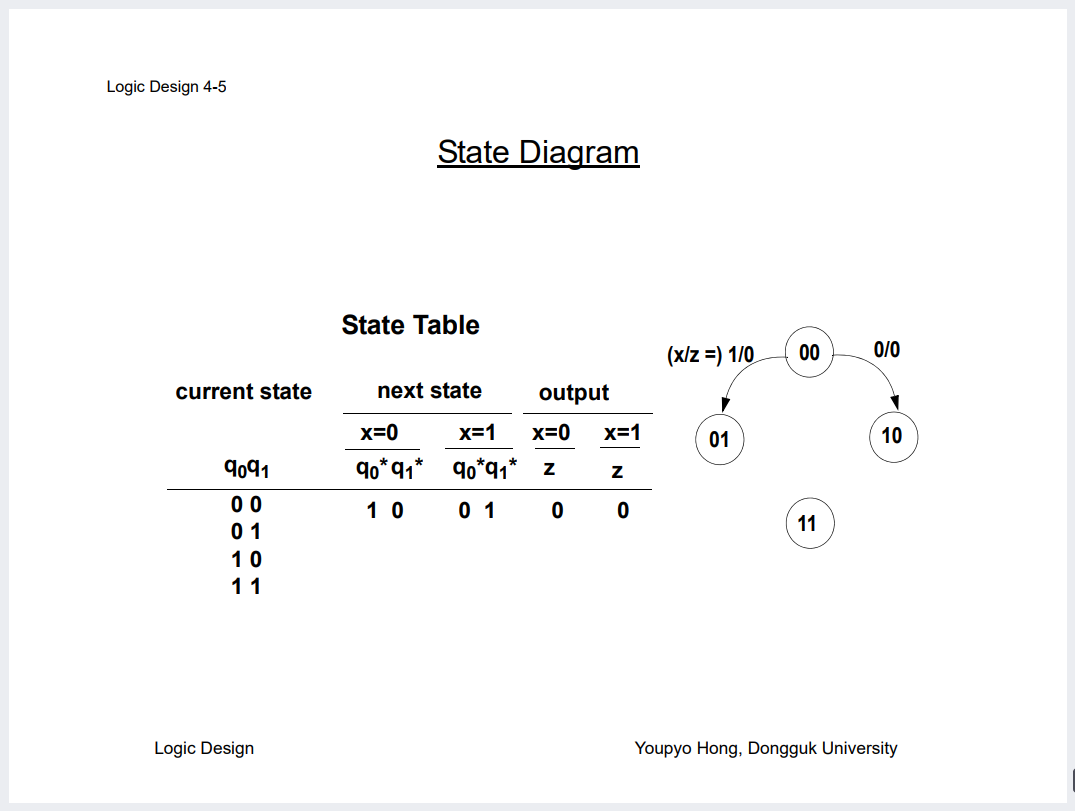

Lecture4 : Set Table & State Diagram

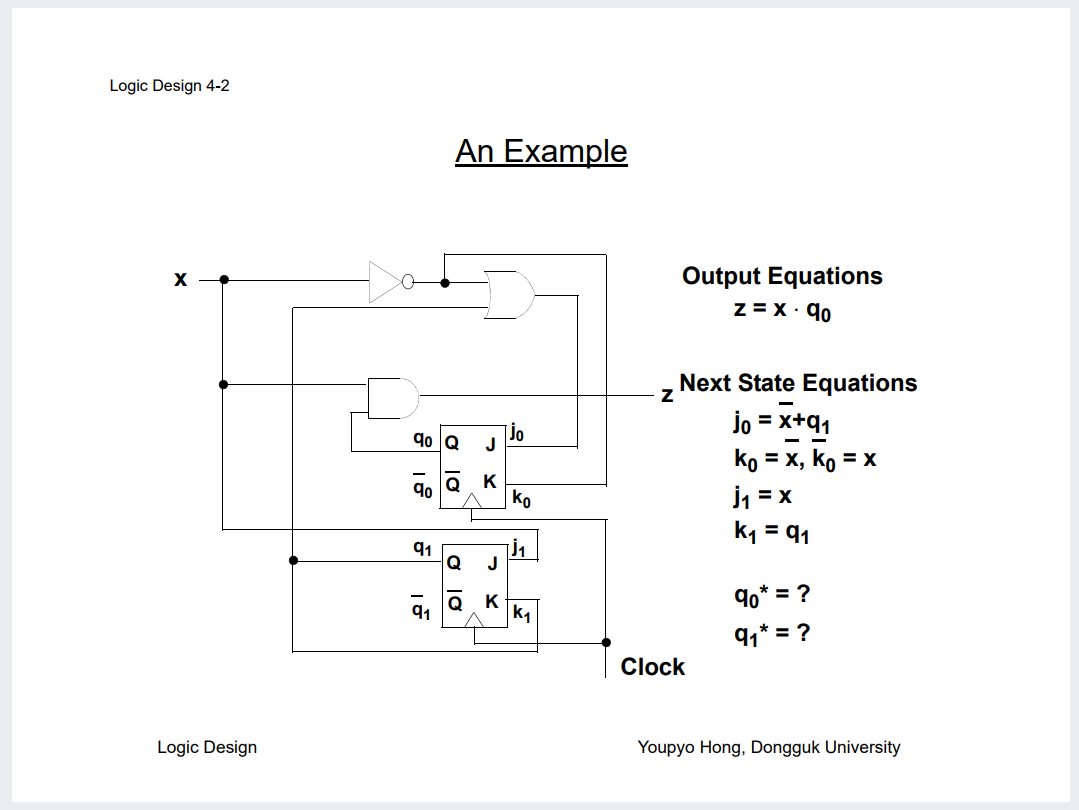

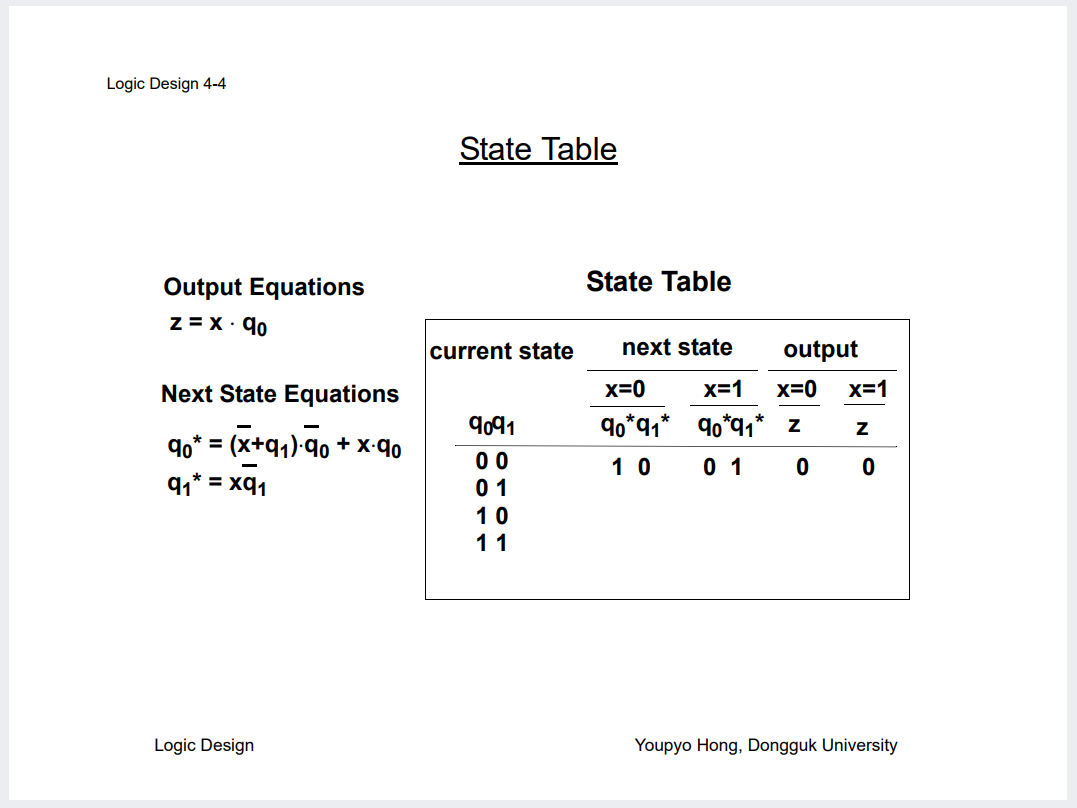

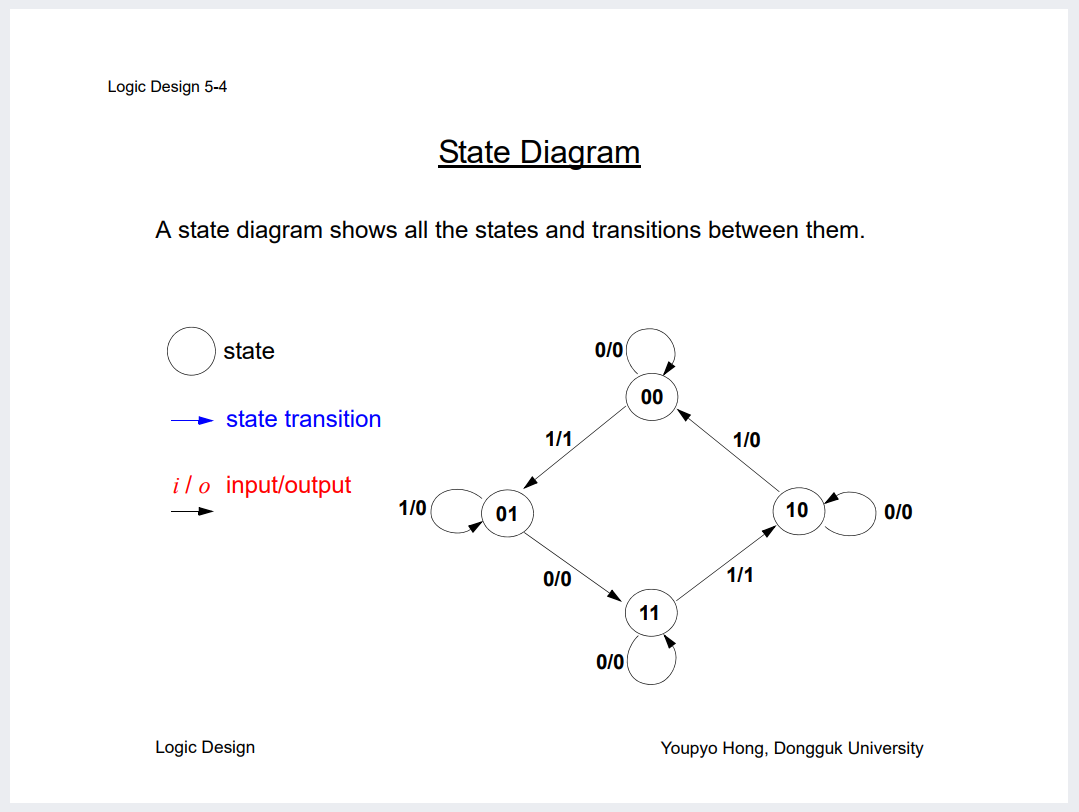

그래서 Sequential 회로에서는 Current State Equations와 Next State Equations를 분리해준다.

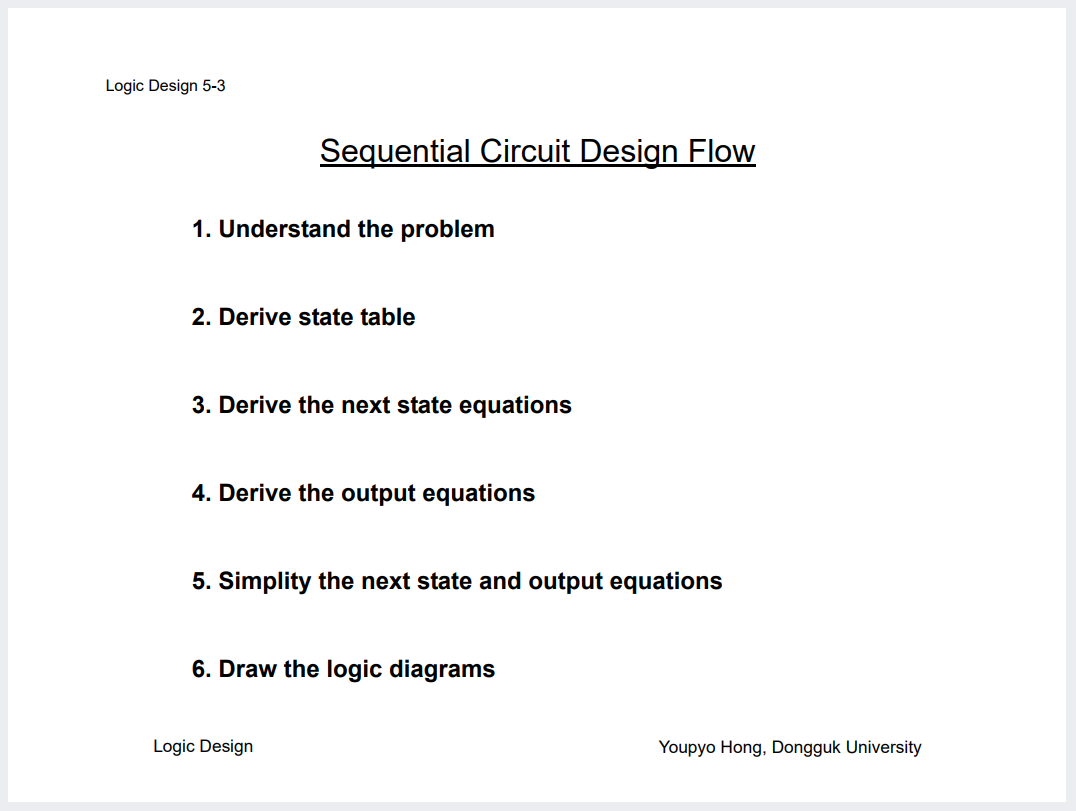

Lecture5 : Sequential Circuit Design

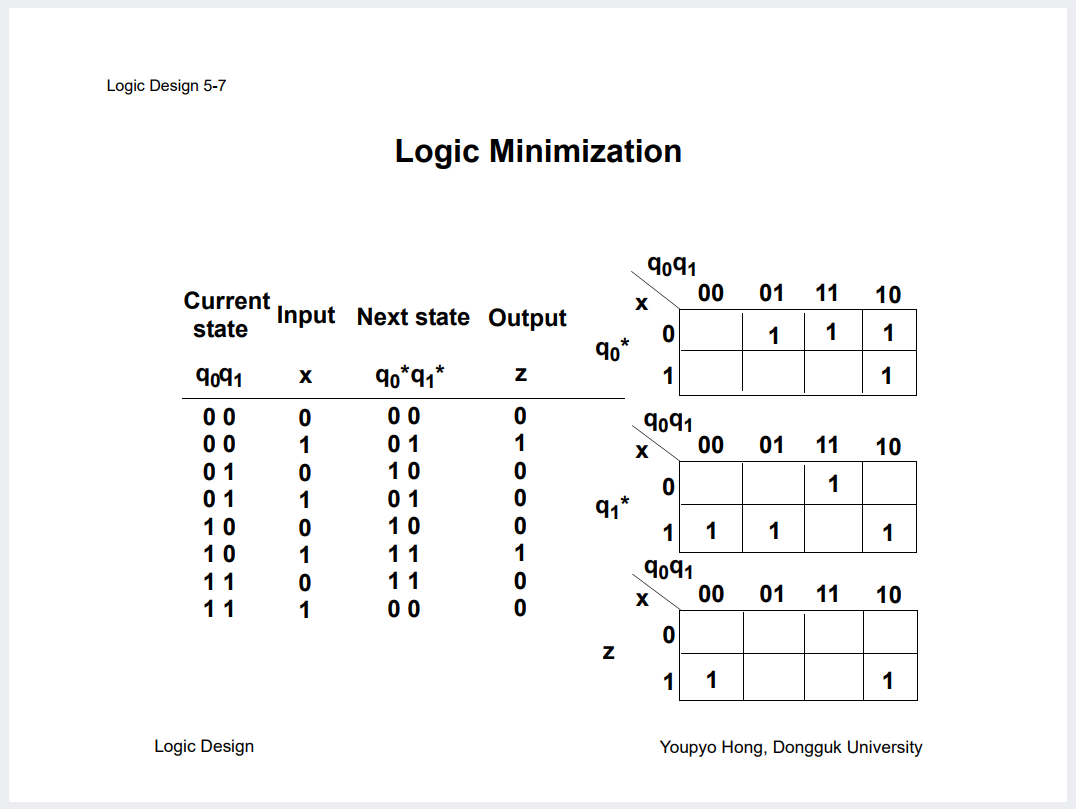

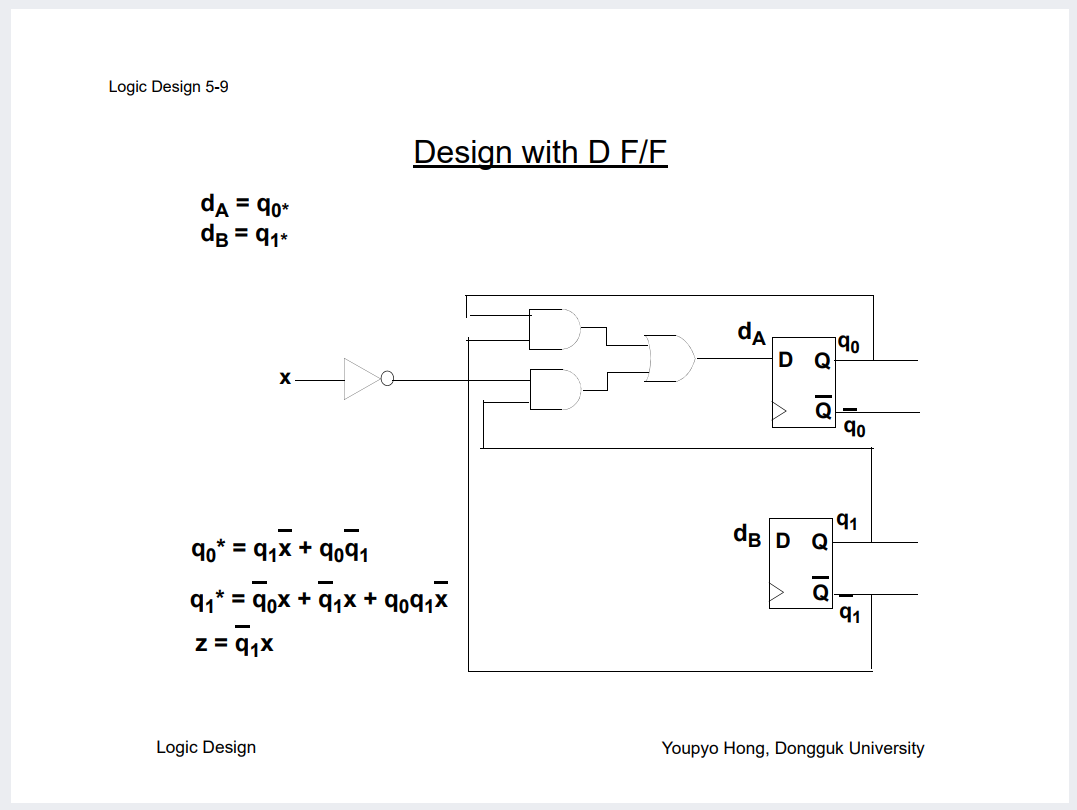

FF는 state transition을 보여줄 수 있는 Excitation Table을 통해 표현해준다.

다음 관계들로 표현이 가능하다.

q0* =

q1*=

z=

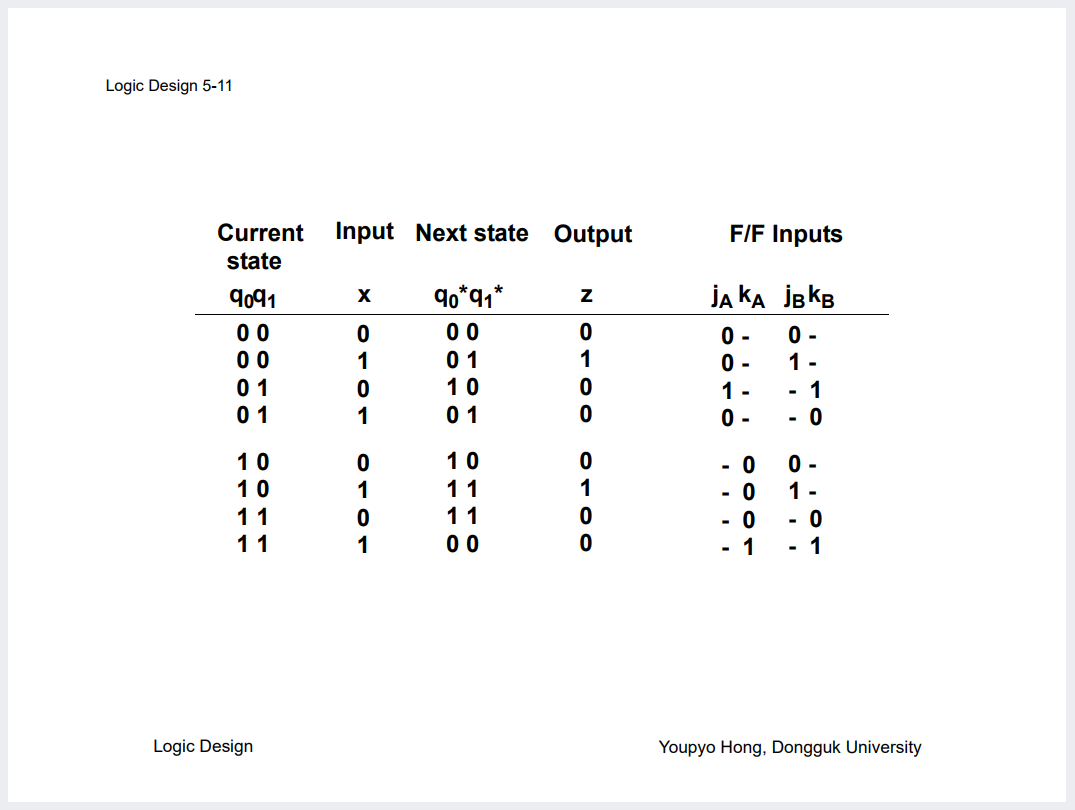

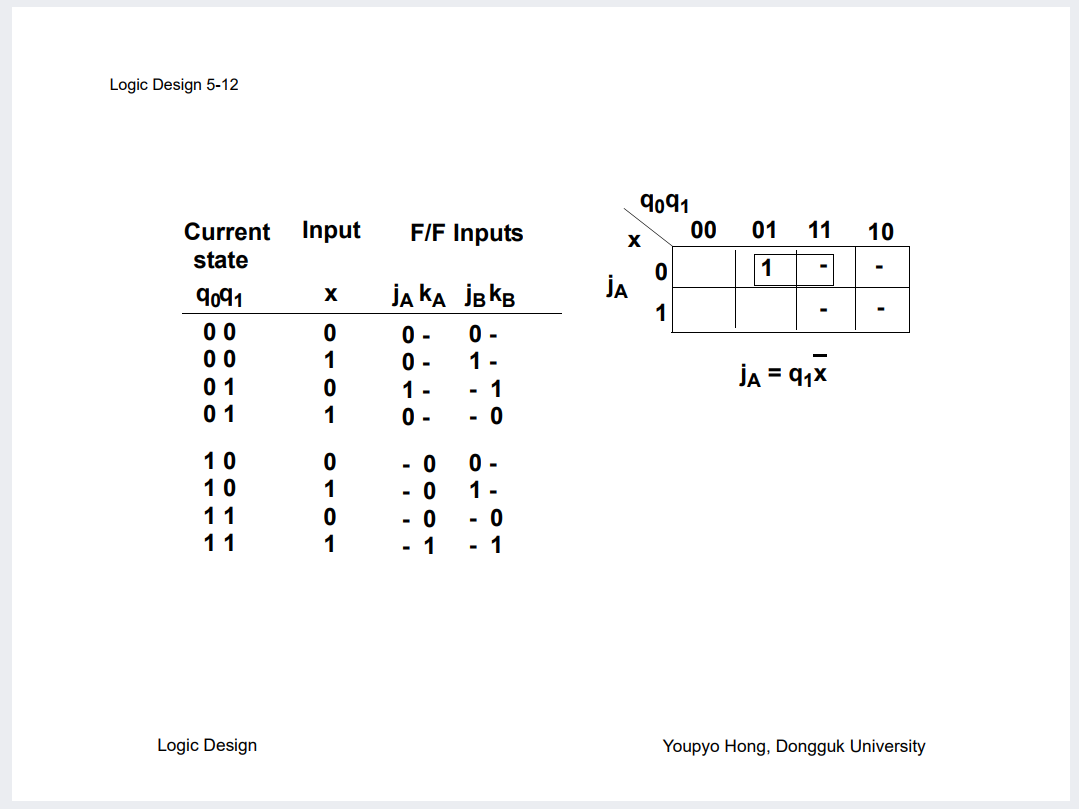

앞에서 우리가 했던 동일한 동작에 대해

D-FF를 통한 구현이 아닌 JK-FF를 통해 구현해보자.

'Engineering(SoC Design) > 디지털공학&논리회로설계' 카테고리의 다른 글

| 논리회로설계 (복습 10~12) (0) | 2022.03.11 |

|---|---|

| 논리회로설계 (복습 6~9) (0) | 2022.03.11 |

| 디지털공학 (복습 8~10) (0) | 2022.03.11 |

| 디지털공학 (복습 4~7) (0) | 2022.03.11 |

| 디지털공학 (복습 1~3) (0) | 2022.03.11 |