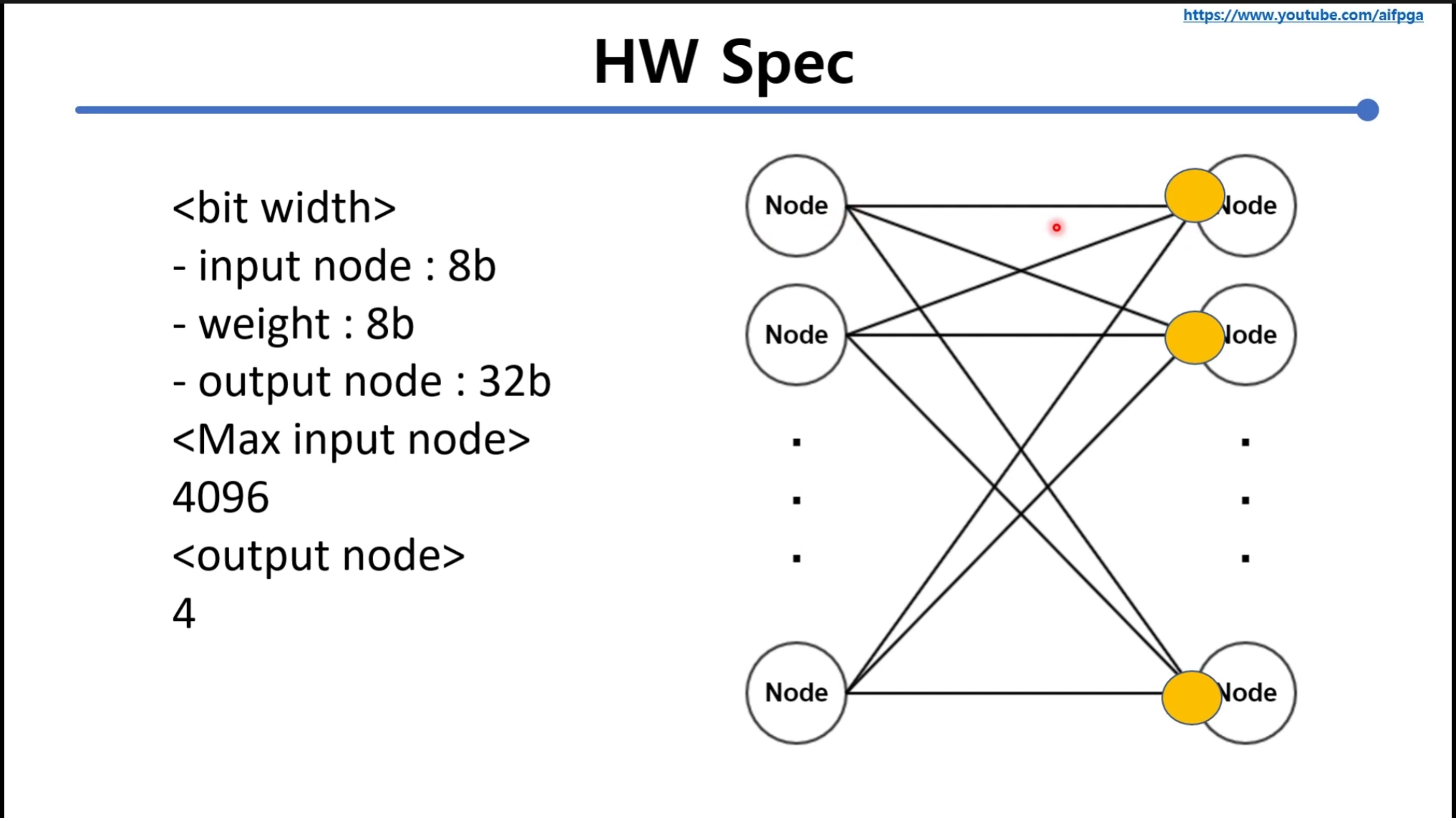

specification에서 PPA의 trade-off관계를 많이 고민해야한다. 그럼 뒷단이 많이 정리된다. software로 어떠한 동작을 할때 PPA가 너무 안좋다 -> hw를 만든다. roofline model bandwidth 가 peak가 초래하는 경우가 많음. 여기까지 오는 단계에서 PPA는 90% 이상 나왔다. 여기서부터 세부 마이크로 아키텍쳐링을 하는 것이고 Performance를 맞추기 위해서 어떻게 Architecturing을 할거냐 ... 등등 마진을 15~30%정도 두고 계산하면 맞는 경우가 많더라. 위 과정이 모두 끝난 후에 그리고서야 verilog 코딩이 이루어진다. RTL 코딩은 바로 하지 않고 모든게 정해진 상태에서 시작하는 것이다. 문서작성(그림포함)을 모두 그린 후 그 그..